1、什么是SPI?SPI是串行外设接口(Serial Peripheral Interface)的缩写,是 Motorola 公司推出的一种同步串行接口技术,是一种高速、全双工、同步的通信总线。2、SPI优点支持全双工通信

通信简单

数据传输速率块

3、缺点没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据可靠性上有一定的缺陷。

4、特点

(1):高速、同步、全双工、非差分、总线式

(2):主从机通信模式5、SPI电路连接

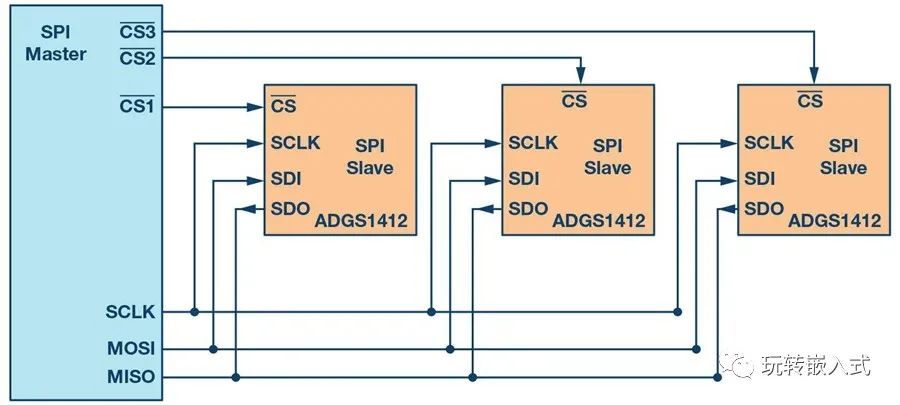

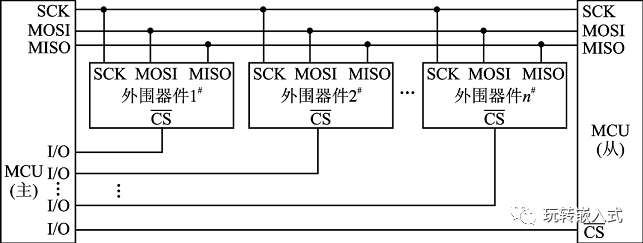

(1):SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,有三线制和四线制之分。信号线包括SDI(串行数据输入 Serial Digital IN)、SDO(串行数据输出 Serial Digital OUT)、SCLK(时钟)、CS(片选)。

(2):SDO/MOSI – 主设备数据输出,从设备数据输入

(3):SDI/MISO – 主设备数据输入,从设备数据输出

(4):SCLK – 时钟信号,由主设备产生;(5):CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低(一般低有效)。

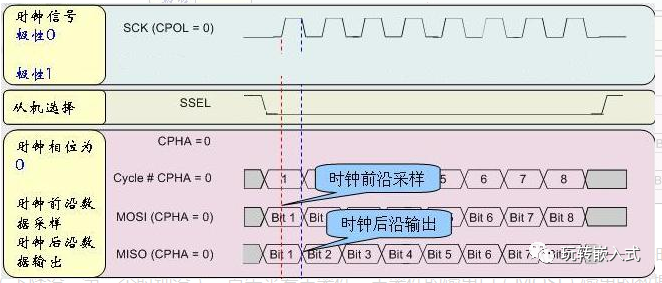

6、SPI通信模式分析SPI通信有4种不同的模式,不同的从设备在出厂时配置模式已经固定, 这是不能改变的,但通信双方设备必须工作在同一模式下,所以可以对主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来控制主设备的通信模式。 具体模式具体如下:

:CPOL=0,CPHA=0

Mode1:CPOL=0,CPHA=1

Mode2:CPOL=1,CPHA=0

Mode3:CPOL=1,CPHA=1

| 模式 | CPOL | CPHA |

|---|---|---|

| Mode0 | 0 | 0 |

| Mode1 | 0 | 1 |

| Mode2 | 1 | 0 |

| Mode3 | 1 | 1 |

时钟极性CPOL是用来配置SCLK电平的有效态的;

时钟相位CPHA是用来配置数据采样是发生在第几个边沿的。 CPOL=0表示当SCLK=0时处于空闲态,所以SCLK处于高电平时有效;

CPOL=1表示当SCLK=1时处于空闲态,所以SCLK处于低电平时有效;

CPHA=0表示数据采样是在第1个边沿,数据发送在第2个边沿;

CPHA=1表示数据采样是在第2个边沿,数据发送在第1个边沿; SPI主模块和与之通信的外设通信时,两者的时钟相位和极性应该保持一致。7、SPI 时序详解CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。 CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。 CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。 CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

注意:SPI主设备能够控制时钟信号,因为SPI通信并不像UART或者IIC通信那样有专门的通信周期、通信起始信号、通信结束信号;所以SPI协议只能通过控制时钟信号线,在没有数据交流的时候,时钟线要么是保持高电平,要么是保持低电平。 例如:工作在模式0这种时序(CPOL=0,CPHA=0),如下:

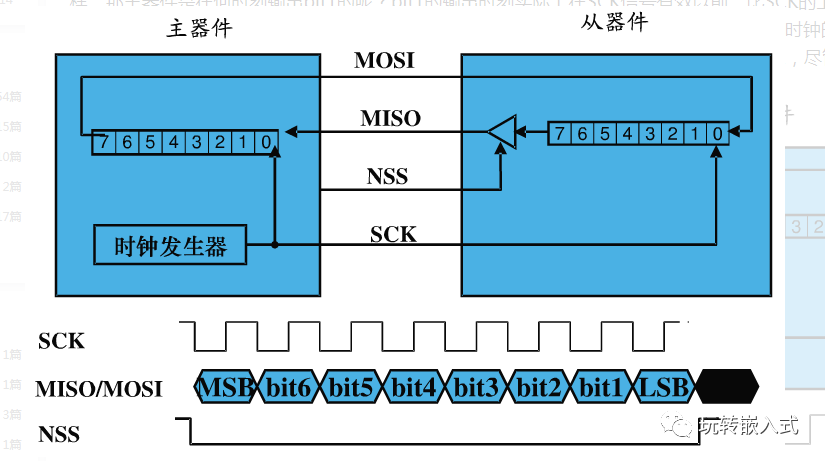

我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),在时钟的后沿输出数据(下降沿,第二个时钟沿)。首先来看主器件,主器件的输出口(MOSI)输出的数据bit1,在时钟的前沿被从器件采样,那主器件是在何时刻输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,比SCK的上升沿还要早半个时钟周期。

bit1的输出时刻与SSEL信号没有关系。再来看从器件,主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时刻输出bit1的呢。从器件是在SSEL信号有效后,立即输出bit1,尽管此时SCK信号还没有起效。 从这张图就可以很清楚的看出主从器件的bit1是怎样输出的。

编辑:jq

-

SPI

+关注

关注

17文章

1900浏览量

102138 -

IIC

+关注

关注

11文章

311浏览量

40769 -

SCK

+关注

关注

0文章

7浏览量

16692 -

miso

+关注

关注

0文章

7浏览量

5722

原文标题:SPI怎么玩?搞懂时序,运用自如

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文带你彻底搞懂K8s网络

ESP32-C5迷你开发板上手指南!轻松驱动SPI屏幕!

FPGA实现基于SPI协议的Flash驱动控制芯片擦除

GPIOB模拟spi的方法及lcd屏幕的接入

请问如何让SPI额外发出一个时钟?

TLC6989 SPI-Compatible Connectivity 芯片技术文档总结

TLC69699 SPI-Compatible Connectivity 芯片技术文档摘要

LP5899 SPI兼容连接设备技术文档总结

Linux三大主流文件系统解析

如何让SPI额外发出一个时钟?

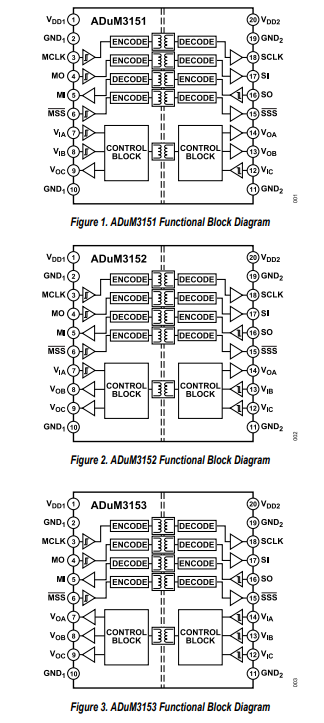

ADuM3151/ADuM3152/ADuM3153用于SPI的3.75 kV、7通道、SPI隔离器、数字隔离器技术手册

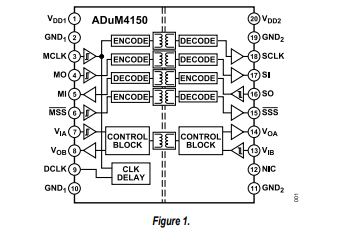

ADUM4150用于SPI高速接口的5kV专用隔离器技术手册

搞懂时序带你玩转SPI?

搞懂时序带你玩转SPI?

评论