1 概 述

扩展频谱通信具有抗干扰能力强、隐蔽性好等优点,已成为通信对抗与反对抗中最重要的技术手段,在军事通信中日益受到重视,跳频电台就是扩频通信在军事领域中的重要应用。在通信对抗中如何有效地对抗跳频电台是目前的一个热点问题。在通信对抗的教学中为了以实验的形式向人们展示跳频通信中干扰与抗干扰的原理,并能对跳频通信进行侦察和实施多种干扰的效果进行比较,为科研中寻找对跳频通信的最有效干扰方式提供有效的数据和参考,本文给出了一种基于DDS与USB技术的通信对抗教学演示系统中硬件方案的设计与实现。

2 系统整体结构设计及原理说明

系统主要由控制计算机、发射机、电子侦察模块、电子干扰模块和接收机等五部分组成,如图1所示。计算机主要是用于控制与协调各个模块的工作和数据传输,决定系统各部分的工作模式并对工作状态进行实时监视。

发射机在计算机指令的控制下,在指定的工作频段内以相应的方式发射跳频信号。电子侦察模块利用高速A/D采样技术与高速FFT实时处理技术可以快速地捕捉并计算出发射信号的工作频率点,同时将侦察到的跳频数据送至电子干扰模块。接收到侦察数据的干扰模块在计算机控制下利用FPGA控制频率合成器件产生各种调制信号,选择不同的干扰方式对通信电台实时有效的干扰。干扰信号与实际跳频信号分别送人合路器中,由合路器送至接收机比较各种不同干扰方式的实际效果。

3 器件的选择

3.1 A/D芯片与FPGA芯片

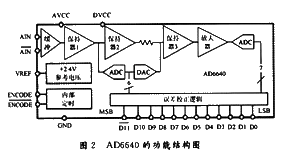

A/D芯片选用的是为宽带和多信道数字无线接收机系统而推出的12位中频快速采样芯片AD6640。

AD6640是一个高速度、高性能、低功耗,单片式12位AD转换器,内含采样保持电路和基准源。他由单电源+5 V供电,TTL/CMOS兼容电平输出,中频采样频率的典型值为70 MHz(多信道时)和200 MHz(单信道时),采样速率可达65 Mb/s,信噪比SNR的典型值为68 dB,SFDR值为80 dB,功耗为710 mW。AD6640采用两级子区式的转换结构,既保证了精度又降低了功耗,其功能模块如图2所示。从图2可以看出ADC所有需要的功能,包括输入缓冲,跟踪保持放大,数字纠错以及2.4 V参考电压都由芯片提供,从而使其设计变得更轻松。

FPGA芯片采用的是Altera公司的ACEXlK系列产品的EPlKl00芯片。其特点是将查找表(LUT)和EAB相结合,提供了高效率而又廉价的结构。基于LUT的逻辑对数据路径管理、寄存器强度、数学计算或数字信号处理(DSP)的设计提供优化的性能和效率,而EAB可实现RAM,ROM,双口RAM或FIFO功能。这使得ADEXlK适合于复杂逻辑及存储器功能,如数字信号处理、宽域数据路径管理、数据变换和微处理器等各种高性能通信应用。基于可重构CMOS SRAM单元,ACEX1K结构具有实现一般门阵列宏功能需要的所有特征,相应的多引脚数提供与系统元器件的有效接口。先进的处理功能和2.5 V低电压要求,使得AC2EX1K器件满足廉价、高容量的应用需要。

3.2 DDS芯片

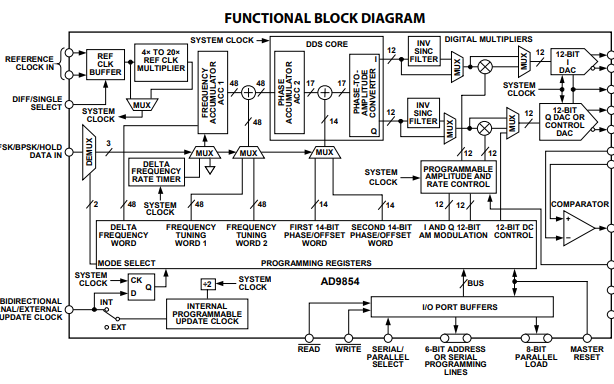

DDS芯片选用的是美国的Analog Device Inc(ADI)公司生产的DDS器件AD9854。AD9854数字频率合成器是一个采用了先进的DDS技术的高集成器件。

他具有一对内部高速、高性能的正交D/A转换器和比较器,可实现数字合成正交的I和Q路输出。当输入一准确的参考频率,AD9854即可产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号。AD9854的DDS核心具有48 b的频率分辨率。14 b相位截断保证了优良的SFDR指标。AD9854的电路工艺使同步正交信号输出的频率最高达到150 MHz,平均每秒产生1百万新频率。AD9854中4~20整数倍的可编程参考频率累加器能使外部输入的低速时钟转变成内部高速时钟(最高300 MHz)。

AD9854能实现除了基本的FSK以外的增强频谱特性的Ramped FSK。该器件采用了先进的35μmC2MOS技术使该器件只需要+3.3 V的电源供应。

系统所用的DAC为ADI公司的AD5344,他是一种低功耗12 b数模转换器。该芯片可应用于便携式电池电源仪器、可编程电压和电流源、可编程衰减器、工业处理控制器以及数字放大和补偿调节等方面。图3为其内部结构原理图。AD5344有4路12 b DAC,可在2.5~5.5 V之间正常工作,在外接+3 V电压时典型电流值为500μA,并且具备进一步将电流降至80 nA的节电模式。他的输出缓存可将输出驱动到两个电源轨道之上。通过A0和A1可控制选择哪一路输出。

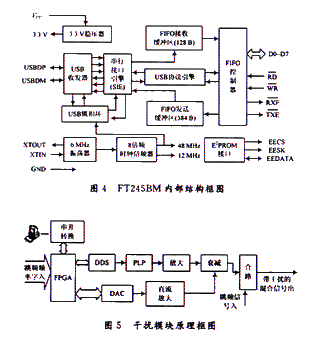

在控制模块中LISB芯片选用的是FTDI公司的FT245BM。该芯片是FTDI公司早期生产的一种较通用的支持USB 1.1标准的专用芯片,其优点在于芯片通用性好,无需固件配置,控制时序简单,而且厂家提供了完备的各类库函数供编程使用,极大地缩短了开发周期。

FT245BM内部结构框图如图4所示,FT245BM内部主要由USB收发器、串行接口引擎(SIE)、USB协议引擎和先进先出(FIFO)控制器等构成。他的一个比较明显的优点就是,内部集成的模块功能完备,不需要在使用时重新对其进行配置。在接收到主机发出的控制命令后,USB收发器自动执行命令,并通过串行接口引擎完成USB数据的串/并双向转换。USB协议引擎按照USB 1.1的规范来完成对FIFO控制器的管理,FIFO控制器通过其两个握手信号的输出端口RXF#和TXE#来引导外部主控制器对USB芯片的读写控制。

4 系统的设计实现

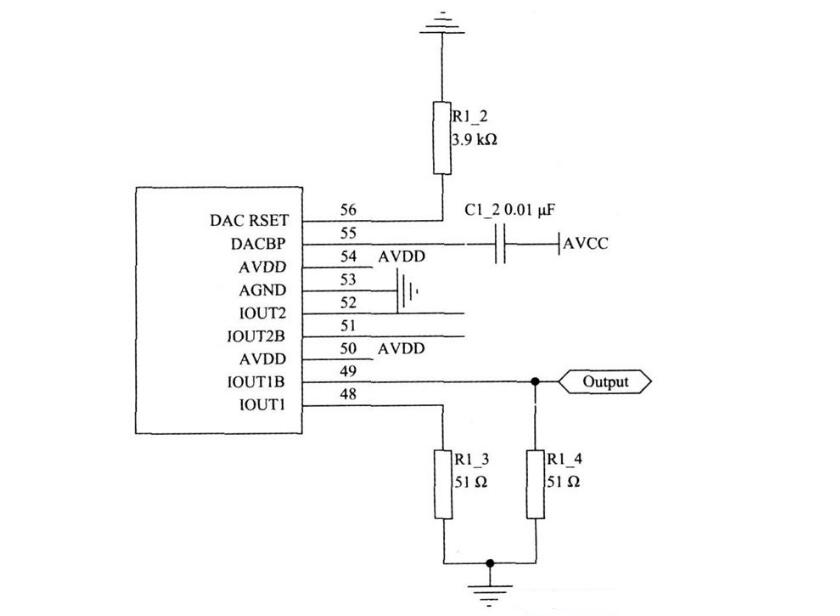

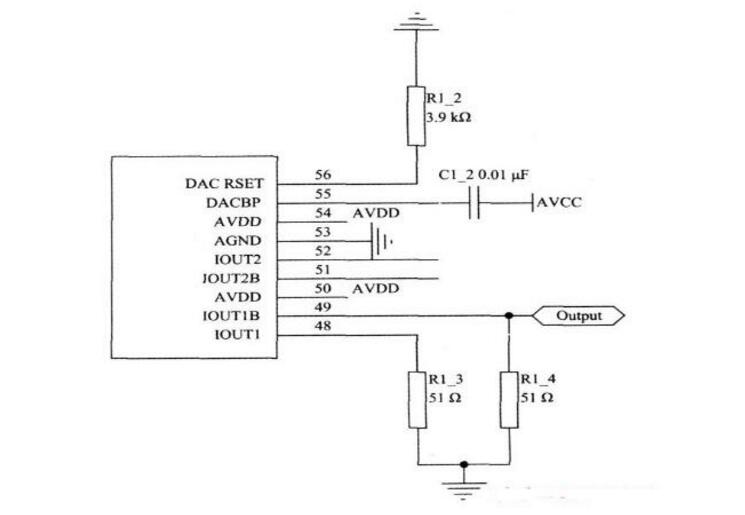

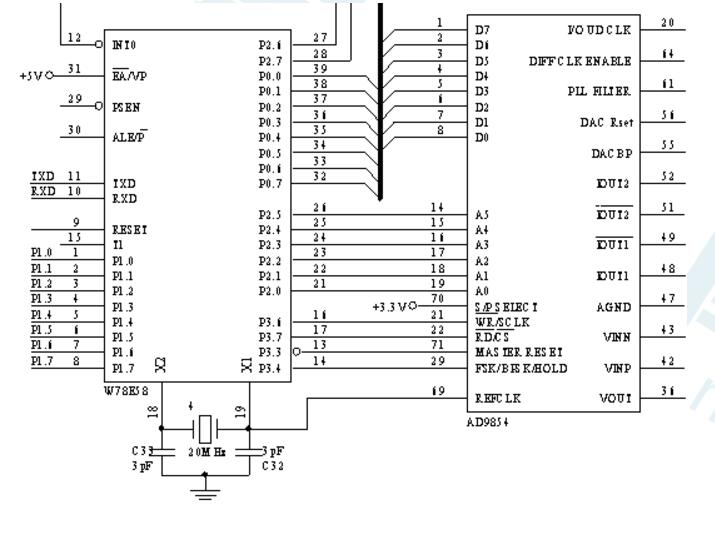

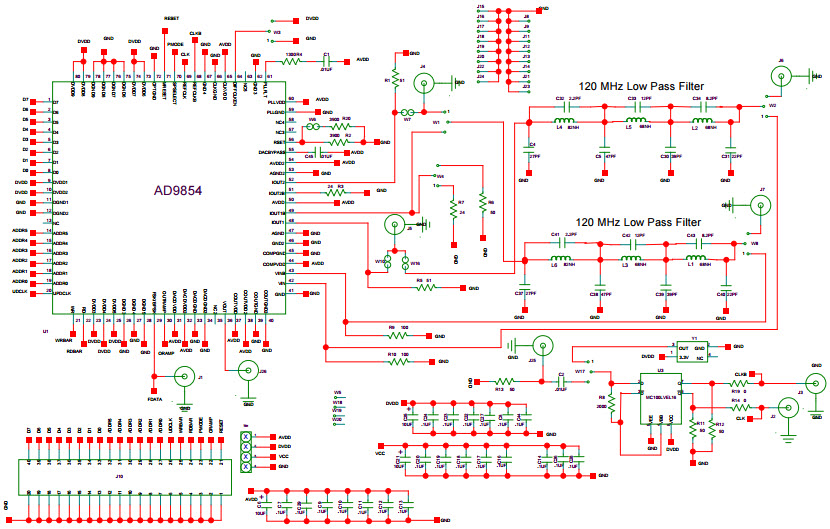

4.1 干扰模块的设计

干扰模块原理图如图5所示。在干扰模块的设计中,选用了常用的DDS芯片AD9854与FPGA相结合的方式来产生干扰频率。为了实现干扰信号功率的可控制,拟在DDS输出的信号加上衰减器。采用计算机通过USB芯片来控制干扰模式的选择和干扰信号参数的选择。DDS产生的信号先通过低通滤波再放大,目的是为抑制杂散信号。

在跟踪式干扰中,FPGA接收电子侦察所获得的通信信号,引导DDS产生同频的干扰信号。在非跟踪式干扰中,由计算机控制产生单频干扰、扫频干扰以及随机调频噪声等样式的干扰信号,这些干扰信号和原跳频信号在合路器合路输出,送给跳频接收机,以此来检验跳频通信对这些干扰样式的抗干扰能力。

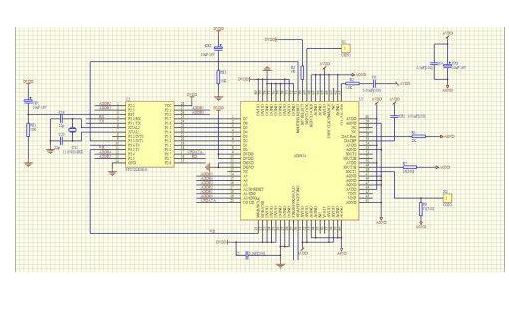

4.2 控制模块的设计

在系统的整体设计过程中,非常重要的部分就是对于整个实验系统的控制。系统的整体控制模块原理框图如图6所示。

从图中可以看出,干扰模块中的FPGA芯片,在系统控制中起着核心作用。在该模块中,FPGA主要完成4个方面的任务:

(1)实现与电子侦察模块的实时通信,不断地接收侦察模块送来的跳频信号信息,并立即做出相应的反应。

(2)实现与计算机主机的通信,控制USB芯片的读写程序,随时接收主机发出的控制指令,并完成相应的功能。

(3)实现对DDS芯片的控制,根据需要选择DDS不同的工作模式。

(4)实现对衰减器的控制,根据主机的命令选择不同的频率幅度。

5 结 语

通过对实际硬件电路的分析与调试,系统实现了计算机对USB芯片的控制、FPGA对DDS芯片的控制、侦察模块与干扰模块的互连通信以及各类干扰方式的可控实现。在进行实际试验时,通过对不同干扰方式的效果进行比较,还可以选择出对跳频电台通信最有效的干扰方式,并且对今后研究实战形式的跳频侦察干扰系统具有一定的实际参考意义。

责任编辑:gt

-

FPGA

+关注

关注

1664文章

22509浏览量

639595 -

芯片

+关注

关注

463文章

54463浏览量

469756 -

频率合成器

+关注

关注

5文章

368浏览量

33916

发布评论请先 登录

敏捷合成器的技术原理和应用场景

如何利用FPGA设计PLL频率合成器?

什么是频率合成器

AD9854驱动程序设计

ad9854调试使用心得

基于AD9854的信号发生器设计

基于AD9854产生MSK调制信号详细说明

ad9854应用电路图大全(五款ad9854信号发生/频率发生器/正交信号源电路)

stm32驱动ad9854程序分享_ad9854构成信号发生器电路

AD9854数字合成器的详细英文数据手册免费下载

基于AD9854/PCB时钟合成器的参考设计

基于EPlKl00芯片和AD9854频率合成器实现通信对抗教学演示系统的设计

基于EPlKl00芯片和AD9854频率合成器实现通信对抗教学演示系统的设计

评论