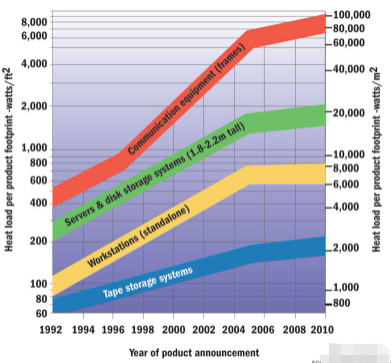

行业专家认为,对于一个典型的大型数据中心而言,其50亿美元成本的80%左右会用在设备的机械和电子基础设施上。对于数据中心服务器,高功率密度的原因之一在于存储器子系统。典型的1U服务器需要600~1,000W的电源供电。这些用于数据中心的高端服务器支持16~18个DRAM插槽。在DDR3(第三代双倍数据速率)系统上,每一个插槽都通过典型的2Gb模块平均汲取9W功率。存储器子系统总功率约为144~162W,约占系统可用功率的25%。将该总功率与典型数据中心中40,000~80,000个服务器相乘,结果为5~13MW(兆瓦特),这仅为存储器子系统的汲取功率。这些功率足以为超过13,000个美国家庭供电。

存储器协会正在推行用三种方法来提高存储器子系统的效率。这些方法已经在实验室环境中进行过测试,其中一些形式将在不久的将来推向商业市场。

第一种省电方法来自DDR3存储器子系统架构。DDR3标准的关键在于降低功耗。目前,固态存储行业的领先技术标准开发者JEDEC(电子设备工程联合委员会)正在着手开发两种省电模式,这两种模式将专注于如何降低寄存器的功耗以及如何降低RDIMM(暂存式双列直插内存模块)模块的功耗。第一种省电模式是用于DDR3寄存器的CKE(时钟使能)断电模式,这种模式要求寄存器器件在CKE输入线路处于低电平时切断其输出。当这种模式通过存储器控制器使能时,地址输出处于三态,DDR3寄存器将其功耗降低将近60%。第二种省电模式是S3电源管理模式,这种模式允许输入时钟浮动。当输入CK和CK#均保持低电平时,器件会停止工作并进入低功耗静态和待机工作模式。

实验室的测量结果显示,寄存器功耗降低了90%。“时钟停止”断电模式只能在模式激活之前,DRAM接收到自刷新命令时使用。在这种状态下,DRAM忽略除CKE之外的所有输入。因此,除了这两个信号之外,所有寄存器输出都能被进一步禁用,从而降低了RDIMM模块的总功耗。但是将存储器子系统从这两种模式唤醒所需的时间有所不同。存储器子系统从CKE断电模式开始响应只需要三个时钟周期,而从S3电源管理模式开始响应只需要几微秒。需要存储器控制器和系统管理软件来支持这些功能,从而利用这些省电功能。

存储器协会正在研究第二种方法,该方法旨在降低存储器子系统的电源电压。这个选择方案研究通过向更小尺寸的半导体工艺转移来降低电源电压。新型1.35VDDR3 DRAM正在实验室进行小批量测试。JEDEC和主要存储器制造商正瞄准供电电压为1.5V和1.35V的下一代DDR3DRAM。目前Inphi公司正在致力于为JEDEC组织起草1.35V寄存器标准。Inphi还在领头开发首个可量产的1.35VDDR3寄存器,可与1.5V寄存器向后兼容。选定的低压DRAM已在一些OEM工厂进行了初步测试,以便在1.35V下运行存储器子系统。早期数据显示,总功耗降低了16%左右,并且没有明显的性能下降。正在进行更多测试,进一步采用未来的技术降低工作电压的研究也正在进行。

第三种省电方法是降低驱动器的输出摆幅电压电平。在DDR3RDIMM标准中,DIMM上的命令和地址信号被端接到Vtt(相当于负载电阻为22Ω时Vdd/2)。DRAM可接受的最小输入电平为±175mV(在Vtt附近)。为实现可靠的工作,设计工程师对Raw CardA这样的较低密度卡也提供了三至四倍于该值的输入电平。将800mV的输出摆幅降低至400mV,可以每通道节省20mA左右。按每个DIMM41个通道,每个系统18个DIMM计算,每个系统就可能节省22W,仅一个典型的数据中心即可节省2MW左右!

应对数据中心面临的能源挑战需要研究省电解决方案,即使通过采用效率更高的省电模式降低电源电压和开关电压,存储器子系统也还是服务器系统中最大的能耗对象之一。

图:服务器系统中主要的能耗对象。

责任编辑:gt

-

电源

+关注

关注

185文章

18989浏览量

264566 -

存储器

+关注

关注

39文章

7757浏览量

172210

发布评论请先 登录

相变存储器(PCM) :新的存储器技术创建 新的存储器使用模式

汽车系统非易失性存储器的选择

多功能存储器芯片测试系统设计方案

嵌入式存储器的设计方法是什么?

相变存储器:能实现全新存储器使用模型的新型存储器

非易失性存储器有哪些_如何选择汽车系统的非易失性存储器

如何提高存储器子系统效率,有哪些有效方法

如何提高存储器子系统效率,有哪些有效方法

评论