昨日,方舟编译器官方新发布了对 RISC-V 后端的支持。

地址:https://gitee.com/openarkcompiler-incubator/mapleall

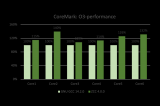

目前,方舟编译器可以在 RISC-V 的 QEMU 模拟器以及真实硬件设备上成功运行 CPU2017 的 C 程序。

本次发布后端主要包括功能相关的基本模块,如指令选择,寄存器分配和栈布局以及 ABI 支持。据介绍,因为后端移植难度主要在于重构优化,其中对指令集的描述方法(机器模型部分)暂未将流行的 DSL 机器模型语言当做第一优先级。

IT之家了解到,方舟社区表示后续会着重针对后端差异化最大的优化框架方面做补强,包括扩展基本块优化,指令流优化以及指令调度等。

责任编辑:PSY

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

编译器

+关注

关注

1文章

1669浏览量

51083 -

方舟

+关注

关注

0文章

20浏览量

8756 -

RISC-V

+关注

关注

48文章

2794浏览量

51922 -

方舟编译器

+关注

关注

0文章

63浏览量

662

发布评论请先 登录

相关推荐

热点推荐

探索RISC-V在机器人领域的潜力

编译错误。通过查阅社区讨论和修改部分编译配置,最终成功解决。这体现了RISC-V生态正在快速发展,但社区的支持至关重要。

2. ROS基础功能测试:

为了验证ROS 2环境是否正常

发表于 12-03 14:40

CIE全国RISC-V创新应用大赛 人脸识别系统介绍与移植

Insightface 及兼容依赖(解决版本冲突)

创建requirements.txt 文件:通过版本约束避开 RISC-V 不支持的特性(如 pydantic 2.x 的 Rust 编译),文件内容如下

发表于 11-08 11:19

RISC-V 蜂鸟E203中PC指针起始地址设置搭建

flashA上,初始地址0x00000000,risc-v的交叉编译文件烧录在了flashB上,初始地址0x00000000,但是arty A7只有一块flash,因此需要将2个文件都烧录在同一个flash下

发表于 10-28 07:47

提高RISC-V在Drystone测试中得分的方法

性能:内存的读写速度、延迟和带宽等都会影响到 Drystone 的性能。

指令集优化:对RISC-V指令集的优化也会影响性能。例如,对于特定的应用或计算任务,可以通过定制指令集来提高性能。

编译器优化

发表于 10-21 13:58

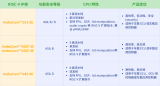

兆松科技ZCC-FuSa编译器全面支持晶心科技车规级RISC-V处理器IP核

2025 年 8 月 26 日,兆松科技宣布其车规编译器 ZCC-FuSa 全面支持 Andes 晶心科技各系列车规级的 AndesCore RISC-V CPU IP (D23-SE

兆松科技发布高性能RISC-V编译器ZCC 4.0.0版本

近日,兆松科技(武汉)有限公司(以下简称“兆松科技”)宣布正式发布高性能 RISC-V 编译器 ZCC 4.0.0 版本。新版本在性能优化、厂商自定义指令支持和软件库等方面实现全面升级

兆松科技ZCC编译器全面支持芯来科技NA系列处理器

近日,兆松科技(武汉)有限公司(以下简称“兆松科技”)宣布正式发布高性能RISC-V编译器ZCC 4.0.0版本。

RISC-V架构下的编译器自动向量化

高性能算力生态的建设,正投入编译器自动向量化优化等多项关键技术,全面助力RISC-V的高性能发展。RISC-V向量设计SpacemiT在现代CPU中,向量支持是算力的

先楫 x 兆松:打造国产高性能 RISC-V MCU生态里程碑

2025年06月06日,兆松科技(武汉)有限公司(以下简称“兆松科技”)宣布正式发布高性能RISC-V编译器ZCC4.0.0版本。新版本在性能优化、厂商自定义指令支持和软件库等方面实现

DC-ROMA RISC-V AI PC 正式发布!

UbuntuDesktop24.04LTS)隆重发布DC-ROMARISC-VAIPC及AIPCMini。本次抢先发布专为RISC-V开发者社区而设,标志着在“开放、

RISC-V的未来应走向何方

半导体行业正孜孜不倦地推动创新,在这个过程中,做出正确选择,正成为芯片成功的关键因素。在众多操作系统、编译器、调试器和其他工具的选项中,开放的RISC-V指令集架构(ISA)正在加速普及。这种开放式ISA赋予了开发者更多自由,使其能够以开源或商业资源为起点,打造专属的定制

HighTec C/C++编译器套件全面支持芯来RISC-V IP

德国萨尔布吕肯,2024年12月5日——世界领先的汽车C/C++编译器解决方案提供商HighTec EDV Systeme GmbH宣布全面支持芯来科技的RISC-V IP。HighTec编译

RISC-V架构及MRS开发环境回顾

的指令集使用模块化的方式进行组织,每一个模块使用一个英文字母来表示。RISC-V最基本也是唯一强 制要求实现的指令集部分是由I字母表示的基本整数指令子集,使用该整数指令子集,便能够实现完整的软件编译器

发表于 12-16 23:08

HighTec C/C++编译器支持Andes晶心科技RISC-V IP

汽车编译器解决方案领先供货商HighTec EDV-Systeme GmbH宣布其针对汽车市场的高度优化C/C++编译器支持Andes晶心科技的RISC-V IP。这项

方舟编译器官发布对 RISC-V 后端的支持

方舟编译器官发布对 RISC-V 后端的支持

评论