随着 DRAM 内存容量和频率的持续增长,现有电脑内存的安全性也一直没有得到提升。近日,JEDEC固态技术协会宣布的最新第一代协议是由对DRAM容量和带宽的需求增加,以及在计算系统中附加新兴的持久内存的灵活方法所驱动的。NVDIMM-P 内存能够在意外断电时保留原有数据,与英特尔傲腾(Optane)内存芯片比较类似。

JEDEC混合DIMM任务组标准化NVDIMM主席Jonathan Hinkle表示,JESD304-4.01 DDR4 NVDIMM-P总线协议为混合DIMM技术提供了正式规范,如NVDIMM-P,它使设计工程师能够将DDR的访问速度与非易失性存储器的可靠性和容量相结合,以改进数据管理。

该标准的关键目标是找到一种在运行时像DRAM一样附加和利用各种持久性存储器的方法,如磁阻随机访问存储器(MRAM)、电阻随机访问存储器(ReRAM)和相变存储器(PCRAM),包括Intel的Optane。

此图为最近发布的JESD304-4.01 DDR4 NVDIMM-P总线协议的一个示例实现,该协议为NVDIMM-P等混合内存技术提供了正式规范,使设计工程师能够将DDR的访问速度与非易失性存储器的可靠性和容量相结合。

NVDIMM-P 的新功能:

持久性:操作系统能够低延迟、高带宽访问非易失内存。

虚拟化的内存:在DDR 通道启用尽可能多的内存容量。

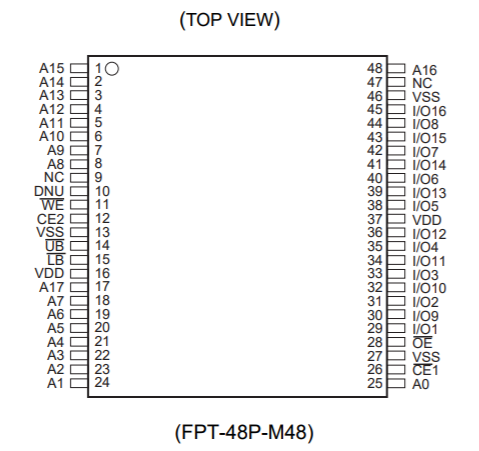

大容量:支持扩展的内存寻址功能。

支持即插即用:在电脑开机时可以直接插入标准的双列内存插槽,并立刻与同一总线上的DDR 内存交互操作。

Hinkle表示,DDR4 NVDIMM-P总线协议与目前建立计算快速链路(CXL)生态系统很好地结合在一起。CXL生态系统的部分目标是减少数据在系统内的移动距离,并将其转移到最适合工作负载的媒体上。“新的存储类型有不同的特点,我们想要低延迟,非常快地访问,但新存储不一定遵循与DRAM相同的规则。”

首先,DRAMDRAM的性能完全取决于处理器的预期。相比之下,各种新的持久内存类型需要多花几纳秒,或者需要执行某些操作才能获得数据返回。“我们需要在新协议中加入灵活性。“我们的目标是确保任何新出现的内存都能利用现有的快速通道;该协议提供的内存媒介提取涵盖了DDR通道上的任何内存介质,包括DRAM、MRAM或Optane等3DXpoint媒体。

然而,Hinkle介绍,我们必须在变量和获得更低延迟访问之间找到平衡——完全变量允许任何东西被连接,但这将增加延迟并降低性能,这有利于支持灵活性。“我们努力使它能让你从非常快的存储中得到非常快的反应。”

该协议还支持扩展内存寻址,以允许更高的内存容量,以及通过标准双重内嵌式内存模块(DIMM)插座实现即插即用互操作性,并可在同一总线上与DDR DRAM内存进行运行时互操作。

DDR4 NVDIMM-P总线协议被设计成兼容DDR4,而不是最新、最好的DDR5,因为DDR4正在广泛生产。Hinkle介绍,协议的下一个主要迭代将包括对DDR5的支持。第一次迭代花了三年多的时间解决这个问题,其目的是开发一个开放的标准来响应行业需求,并适应不同的供应商提供不同类型的新兴的、持久的记忆,而不是有一个合适的解决方案。得益于DDR4 NVDIMM-P总线协议,英特尔最近推出了OptaneDIMM,可以极大的改变服务器和数据中心处理数据集的方式。英特尔的Optane DIMM将使用3DXPoint内存,这是一种非易失性内存,是NAND和DRAM的融合。其亮点是3DXPoint在断电后保留数据,这意味着它可以作为内存和存储器进行寻址,并为许多新的用例做好准备。“这确实是一种标准方式,我们可以触摸各种不同类型的内存,它具有我们可以支持的所有特征,比如记忆持久性和更高的容量。”

英特尔正在定位DIMM以弥合DRAM和NAND之间的价格和性能差距,尽管目前还不知道具体的定价细节。但是,预计DIMM的价格远低于目前的DDR4 DRAM。

能够容纳各种持久性内存的概念并不是一个新的尝试。尽管非易失性内存主机控制器接口规范(NVMe)主要设计目标是解锁NAND闪存作为固态驱动器(SSD)的性能,此前这一性能受到硬盘驱动器架构的限制,但它也有潜力被用作其他基于持久性存储器的设备的接口,如MRAM和OPTANE媒体,而不仅仅是基于闪存的SSD。

CXL的三个协议可以单独使用,也可以在特定的用例中组合使用,内存中的加速器可以支持密集计算,内存缓冲区可以支持内存容量扩展和存储类内存。

CXL最近的快速发展还涉及到内存选项(volatile或non-volatile)的灵活性。它由三个协议组成,每一个协议都可以单独或组合使用用于特定的用例,包括支持密集计算的内存加速器或支持内存容量扩展和存储类内存的内存缓冲区。

延伸阅读——NVDIMM到底是一个什么神仙技术?

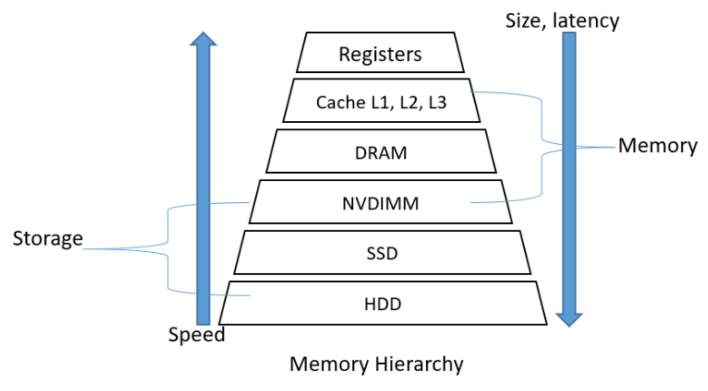

在计算机体系结构中,处理器CPU主频增长及多核的出现使其性能以每年70%的速度在增加,而以DRAM为主流的存储器性能每年提升约7%,这就导致了所谓的“内存墙”出现。应用方面,云计算、大数据和一些高性能计算平台迫切需增加内存容量。

NVDIMM就是应对这样挑战的产物,也正好能够满足相关企业提升性能的需求。

NVDIMM技术平衡内存与闪存性能差异

处理器与存储器间的性能差异催生了NVDIMM(Non-Volatile Dual in Memory Module,非易失内存模组)的出现。非易失性内存指的是即使在不通电的情况下,数据也不会消失。因此可以在计算机非正常掉电、系统崩溃或正常关机的情况下,保持数据不丢失。NVDIMM技术平衡了传统主流内存DRAM和非易失介质如Flash(闪存)/PCM(相变存储)之间的性能差。

NVDIMM的诞生一方面解决了内存容量的需求,另一方面也解决了DRAM内存掉电易失的尴尬。在速度上,NVDIMM介于DRAM内存和NAND Flash存储之间,它兼顾了DRAM访问速度快和NAND Flash容量大的优点。以DRAM为主内存的存储器容量目前在GB级别,但DRAM具有纳秒级快速访问的优点;与之相对的NAND Flash SSD存储容量已经达到TB级别,而访问速率却在微秒级。

根据JEDEC标准化组织的定义,有三种NVDIMM的实现:

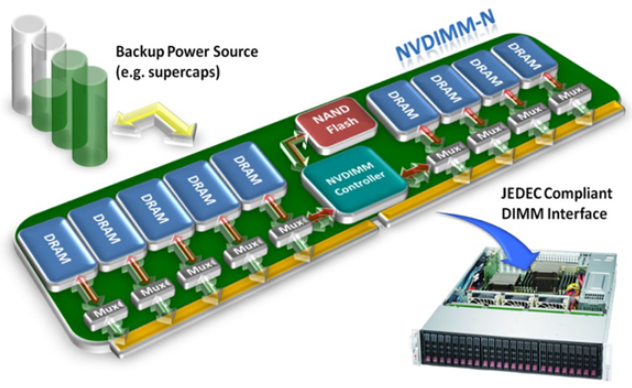

NVDIMM-N

在一个模块上同时放入传统DRAM和flash闪存。计算机可以直接访问传统DRAM。通过使用一个小的后备电源,为在掉电时,数据从DRAM拷贝到闪存中提供足够的电能。当电力恢复时,再重新加载到DRAM中。

NVDIMM-F:基于DDR接口的闪存盘

指使用了DRAM的DDR3或者DDR4总线的flash闪存,本质上讲可以认为是一块在DDR接口上的SSD。我们知道由NANDflash作为介质的SSD,一般使用SATA,SAS或者PCIe总线。使用DDR总线可以提高最大带宽,一定程度上减少协议带来的延迟和开销。NVDIMM-F的主要工作方式本质上和SSD是一样的。因此它的延迟在10的1次方微秒级。它的容量也可以轻松达到TB以上。

还有一个就是上述的NVDIMM-P。NVDIMM-P实际上是真正DRAM和flash的混合。它既支持块寻址,也支持类似传统DRAM的按字节寻址。它既可以在容量上达到类似NANDflash的TB以上,又能把延迟保持在10的2次方纳秒级。

编辑:hfy

-

DRAM

+关注

关注

40文章

2373浏览量

188171 -

DDR

+关注

关注

11文章

747浏览量

68533 -

FLASH闪存

+关注

关注

0文章

7浏览量

7846

发布评论请先 登录

意外断电之后如何避免不稳定的电冲击击坏电器

手机的新技术盘点

保留原有值将符合的值进行倍数增大后在整合

IDT 公布业界首款 DDR4 NVDIMM 电源管理集成电路

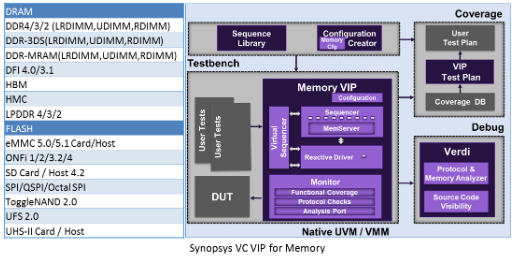

新思科技推出业内首个DDR5 NVDIMM-P验证IP 加速验证工作完成

ASIC设计方案提供商灿芯半导体为NVDIMM OEM提供控制器芯片方案

NVDIMM-P非易失内存标准公布:断电不丢数据、兼容DDR4

富士通FRAM是断电情况下也能保留数据非易失性的存储器

NVDIMM – 内存和存储的完美结合

NVDIMM-P内存最新技术,能够在意外断电时保留原有数据

NVDIMM-P内存最新技术,能够在意外断电时保留原有数据

评论