随着速率的不断提高,信号能够在链路中传输的难度越来越大,信号质量会不断下降,我们把高速信号在传输中遇到各种问题统称为信号完整性问题。通常我们认为信号完整性问题主要是从时域上去衡量,通过对波形质量的判断,我们把信号完整性问题分为以下几类:反射,串扰,振铃,地弹。另一方面我们在高速链路的表征上,人们又习惯使用S参数的形式去衡量一个通道的优劣,包括了回波损耗,插入损耗,串扰等指标。那么频域上的各种损耗的表征和比较直观的时域波形或眼图之间有什么关联呢?用时域的波形来判断信号质量的确很清晰,然而波形却不容易给我们以有效的优化手段。因此本文着重介绍如何使用频域的S参数来分析问题,看看从S参数角度去看信号完整性问题,能否得到关于链路通道更多的信息。

从时域推导S参数损耗

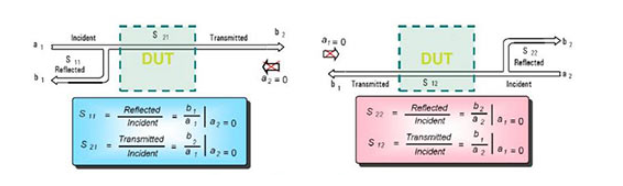

图1是对一个两端口的S参数的表征过程,通过测量入射波形和反射波,从而计算出回波损耗S11和插入损耗S21,然后用dB值进行表征。

图1 S参数的表征

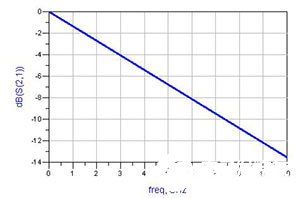

因此当我们看到一个链路的损耗如图2时,其实我们可以用时域的方式去推导它。

图2 链路损耗曲线

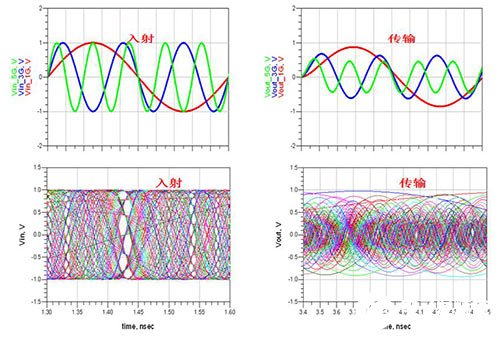

我们知道损耗曲线就是通过发送不同频率的正弦波,然后去计算反射波、传输波与入射波的比值得到的,假设如图3所示分别发送1GHz、3GHz、5GHz的正弦波,幅度为峰峰值2V,那么会得到传输前后的波形如下:

图3 正弦波的入射与传输波形

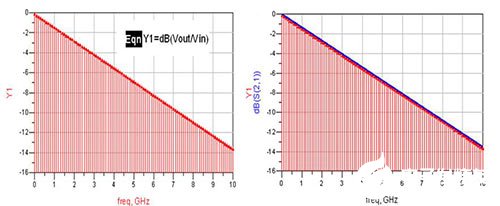

那么当时域有很多不同频率的正弦波时,就能得到很多传输后的波形,同时从图3也可以看到,不同频率的正弦波传输后的幅度是不相同的,而且频率越高的正弦波幅度越小。那么按照图1 的损耗计算公式,如果有很多个传输波形比上入射波形,就会得到上述图2的频域损耗波形了,如图4所示,分别为幅度和dB的表征。

图4 从时域推导频域损耗曲线

损耗和阻抗

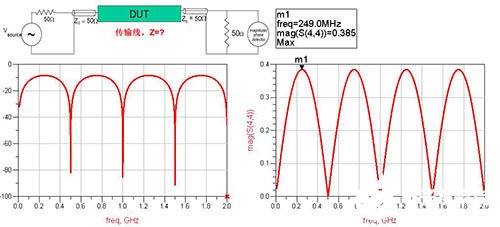

我们知道阻抗不匹配是影响信号完整性的主要原因之一,它会造成波形的过冲,反射,振铃问题的出现,如果我们仅仅观察波形的话,似乎很难知道链路的阻抗到底是多少,但是从频域S参数的回波损耗去看却可以很方便的估算出链路的阻抗。就好像图5所示一样,我们通过仿真或者测试的手段得到了链路的回波损耗曲线(分别用dB和幅度表征)后,那我们怎么能够推导出链路传输线的阻抗呢?

图5 链路的回波损耗推导阻抗

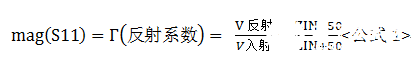

首先关于输入阻抗ZIN有如下的公式1:

然后对于ZIN的最大值反映在图5的回波损耗曲线上就能看到最差的结果,如图5中m1所示,在249MHz处有回损的最大值0.385。

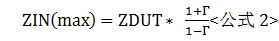

于是又有下面的公式2:

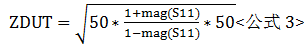

因此结合以上两个公式就能得到传输线阻抗ZDUT的公式3:

因此把回波损耗中mag(S11)=0.385代入公式就得到了传输线阻抗ZDUT=75欧姆

损耗与波形(眼图)

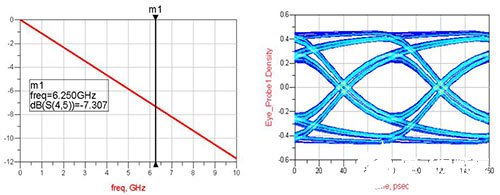

对于硬件工程师或者测试工程师而言,最直观的判断信号质量好坏的标准还是通过时域的信号质量,也就是波形或者眼图。无论是像DDR这种并行信号的波形或者像高速串行信号的眼图结果,它们的好坏可以很容易通过相关的电平标准和眼图模板衡量出来。但是如果得到了一个恶劣的时域结果,可能就不是所有人都知道链路哪里需要优化和怎样去优化。时域分析在这个时候就暴露了它的不足,不好的时域波形(眼图)能够体现的链路的设计问题其实不多,这也导致了很多缺少信号完整性或者高速理论的同行遇到一个较差的时域结果常常无从下手,很难去对PCB链路进行优化。如上文所说,S参数的确可以反映出更多PCB链路的特点和信息,通过对S参数的查看和探究,经常可以得到更多关于PCB链路优化的方向和信息,我们就以下面这个PCB设计仿真比较常见的例子进行说明。如图6所示,我们仿真一个12.5Gbps的高速信号通道,如果该通道传输线的阻抗控制得很好(差分100欧姆),线长在10inch,我们加上收发芯片的模型进行眼图仿真,就能得到一个比较好的眼图结果,通过相关的眼图模板进行衡量,无论是眼高还是眼宽都有很大的裕量,从S参数上看,可以看到此时的损耗在6.25GHz基频处为7.3dB,整个损耗曲线随着频率的升高线性下降,是比较理想的无源参数结果。

图6 比较理想的损耗和眼图结果

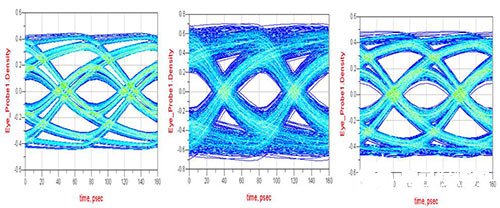

然而如果同样的网络,换一个PCB设计工程师进行设计后,在PCB链路处理得不够好的情况下,我们可以得到像图7这些比较差的眼图结果,眼高眼宽裕量都是比较小,当然我们知道这样的设计肯定导致了比较严重的信号完整性问题,产品的质量和稳定性也是不好的。

图7 不理想的眼图结果

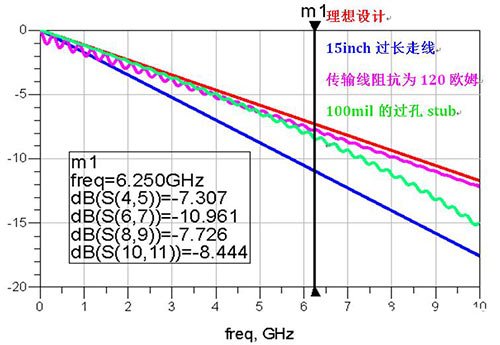

如果换作是你仿真或者测试得到了这样的眼图结果后,你能够很快的找到到底PCB链路出现了什么问题导致的吗?这三个不理想的眼图结果无论是眼高还是眼宽都比较接近,前面说到的,从时域上看只能看到像过冲,振铃,或者眼图闭合的现象,但是原因却不容易定位到,实际上它们都是PCB链路上3种比较典型的链路设计问题导致的,分别是线长过长,传输线阻抗控制不对和存在换层过孔比较长的stub(残桩)。如果从它们的S参数去看的话,我们就能看到它们的差异,如图8所示:

图8 几种情况的损耗曲线

首先,从图8的曲线,至少我们能很清楚的看到几种情况的差异,对于PCB仿真工程师而言,从频域的损耗曲线上能看到的东西就更多了。首先我们对比红色和蓝色的损耗曲线,红色我们知道是10inch的走线,阻抗控制得很理想(100欧姆差分),而且链路中没有换层过孔的stub,因此正如同上面所说的,损耗曲线在整个频域上线性度比较好,没有谐振点出现。而我们看蓝色的曲线,同样它的线性度也很好,也没有谐振点的出现,和红色曲线的区别仅仅是损耗成比例的增大了,因此我们可以判断出蓝色曲线阻抗同样控制得很好,只是线长过长导致损耗的增加而已。然后我们看粉红色的损耗曲线,和理想红色曲线对比,发现粉红色曲线呈周期的振荡,每个振荡的谐振点频率间隔相同,根据前面对S参数与阻抗的分析就可以判断,最有可能导致这种周期振荡的原因就是传输线阻抗控制得不好。最后我们分析绿色的损耗曲线,我们能看到似乎也是周期性的曲线振荡,但是另外还有一个更明显的特点,就是越往高频时,有一个很迅速的非线性跌落,这种比较窄带的跌落通过是由于链路存在分支导致的,因为有分支,在分支反射位置才会出现波形相反相位的叠加,从而导致在该频率的时候几乎没有能量传输过去,而对于点对点的高速串行信号链路来说,分支主要就是换层过孔的stub,实际上过孔stub的存在和长短,对于高速信号能否良好传输有着决定性的影响。

结语

本文主要介绍了如何通过S参数去得到更多的PCB设计信息,从而去探究通道信号质量不理想的原因和找到优化改善的方向。我们去了解信号质量的手段应该是多样化的,除了传统的查看时域的波形(眼图)外,还要从频域上去衡量。毕竟频域和时域是相互联系的。时域具有直观性,的确是第一时间要去衡量的指标,但是当时域结果不理想且凭经验又很难去定位问题的时候,从频域的角度去补充就会是一个很好的选择。信号完整性的问题表现的形式有很多很多,而且随着速率的不断提高,还会有更多的问题出现,本文介绍的S参数表征信号完整性问题仅仅只是冰山一角,S参数能够提供的信息绝不仅仅如此,篇章所限,只列出以上几个比较典型的应用。当然无论是从频域S参数还是时域去分析信号完整性问题,具备一定的理论基础肯定是前提,只有掌握了较丰富的理论知识,才有可能从得到的各种信号完整性现象中抽丝剥茧,从现象看到本质。

编辑:hfy

-

PCB设计

+关注

关注

392文章

4572浏览量

83221 -

信号完整性

+关注

关注

65文章

1337浏览量

94916

发布评论请先 登录

相关推荐

如何通过S参数去得到更多PCB设计的信号完整性

如何通过S参数去得到更多PCB设计的信号完整性

评论