PHY与PHY之间进行通信的接口称为MDI(Medium Dependent Interface,媒介专用接口)。

媒介(Medium)有背板、Cable、光纤,因媒介的不同就会有不同的通信协议;数率的不同又会有不同的通信协议。媒介和数率两两组合就可以变幻出许多种通信协议,但万变不离其宗,搞清楚协议名称的命名方式,就能一一识别。

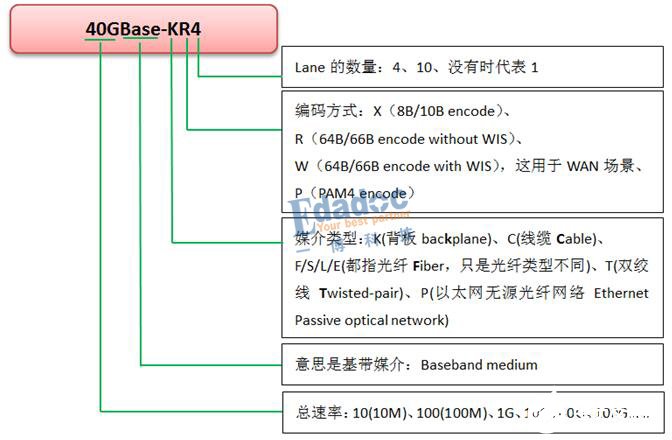

以40GBase-KR4为例进行说明:

媒介有K(背板backplane)、C(线缆Cable)、L(光纤)、T(双绞线Twisted-pair)、F(光纤Fiber Optic),其中T(双绞线Twisted-pair)只出现在≤10Mb/s的情况下,由于技术已经很古老了,高速信号不会再用到,所以本文偏重于讲解高速信号的协议,对于低速接口协议,比如采用T(双绞线Twisted-pair)、F(光纤Fiber Optic)媒介的10Base-T、10Base-F、100Base-TX、100Base-FX协议就此略过。

下面我们按媒介的不同来分类,首先来讲讲最为大家熟知的背板。

1. 背板

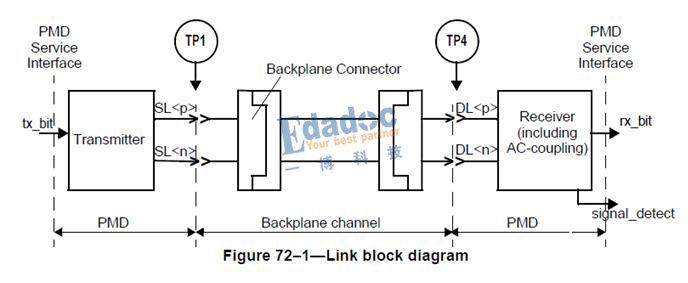

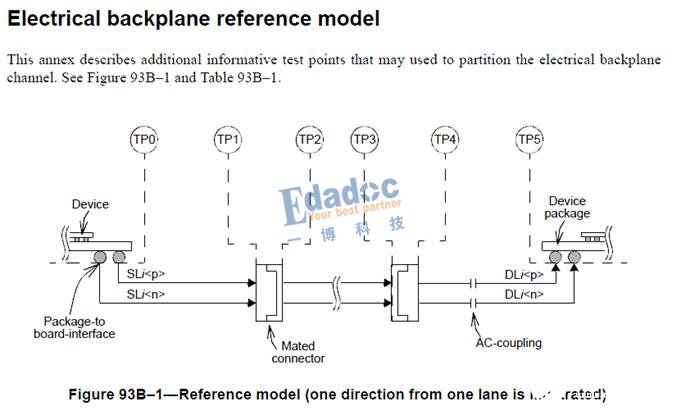

媒介采用背板,PMD与PMD之间的链路示意图如下所示:

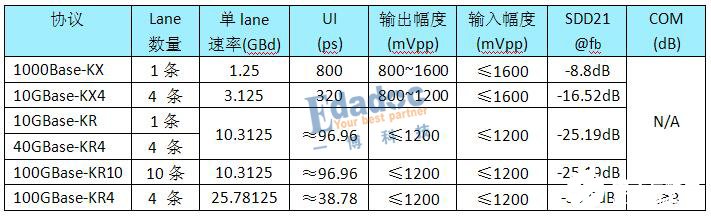

不同速率的协议及其要求如下:

说明:背板除了上面这个表格里的协议,还有100GBase-KP4,100GBase-KP4比较特殊,采用的是PAM4电平(三电平、两个眼图),而非之前的NRZ电平(两电平、1个眼图),所以对100GBase-KP4接收机的要求给出了很多新的参数。针对PAM4信号,后续单独来讲。

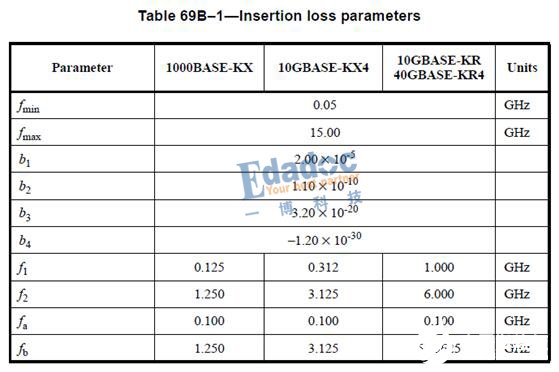

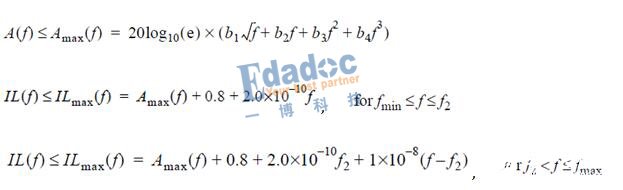

1) 1000Base-KX、10GBase-KX4、10GBase-KR、40GBase-KR4对channel的详细要求:

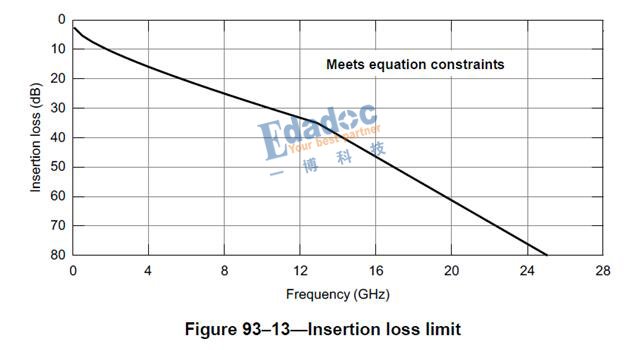

2) 100GBase-KR4对channel的详细要求:

2. CABLE

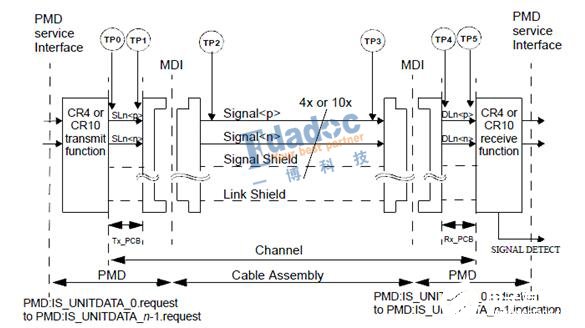

媒介采用屏蔽层平衡铜轴线缆(Shielded balanced copper cabling),PMD与PMD之间的链路框图如下所示:

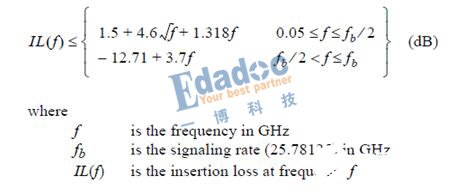

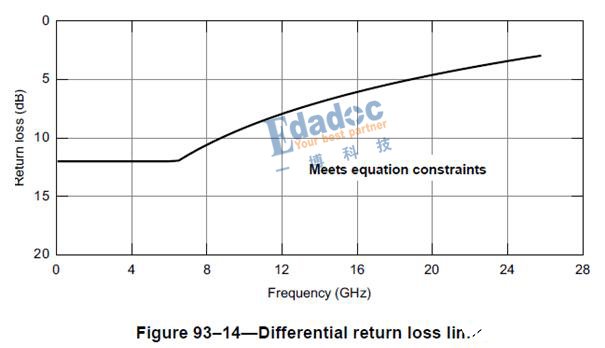

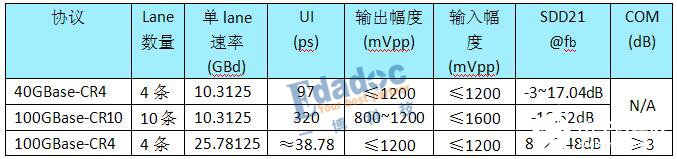

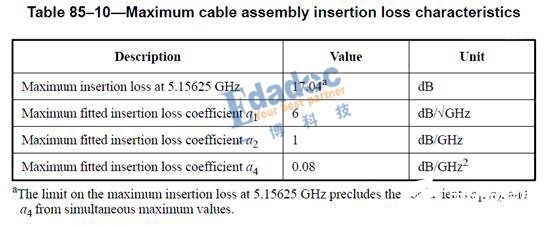

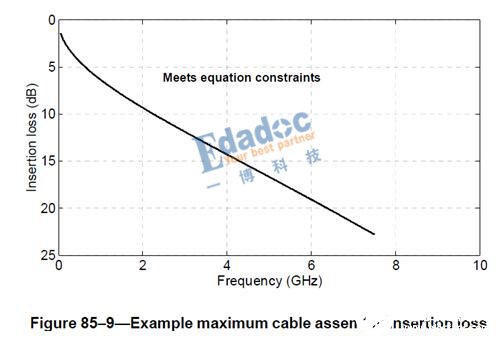

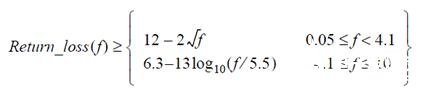

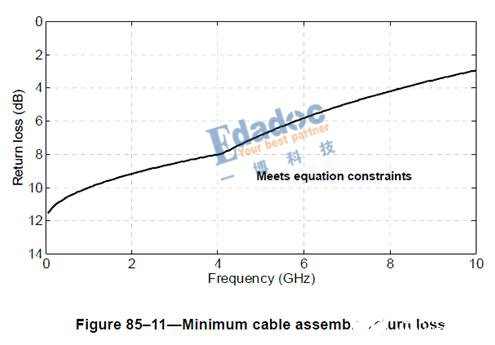

1) 10.3125GBd速率对于Cable插损具体的要求如下所示:

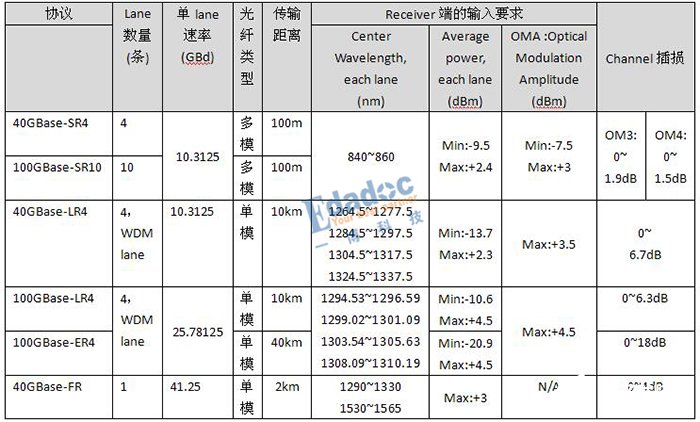

3. 光纤

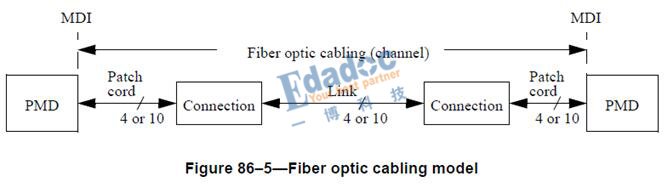

媒介采用光纤(Fiber),PMD与PMD之间的链路框图如下所示:

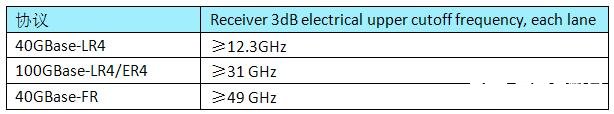

除了上面的要求,采用光纤时还对3dB滚降频点有要求,分别如下所示:

编辑:hfy

-

通信技术

+关注

关注

20文章

1170浏览量

94136 -

PHY

+关注

关注

2文章

331浏览量

53798 -

pam4

+关注

关注

2文章

38浏览量

14839

发布评论请先 登录

浅析PHY与PHY之间的通信技术(以40GBase-KR4为例)

浅析PHY与PHY之间的通信技术(以40GBase-KR4为例)

评论