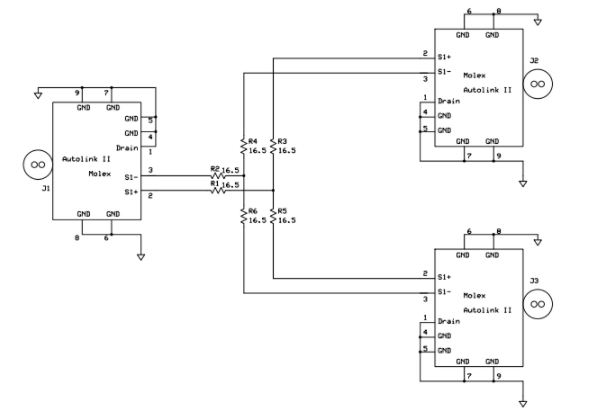

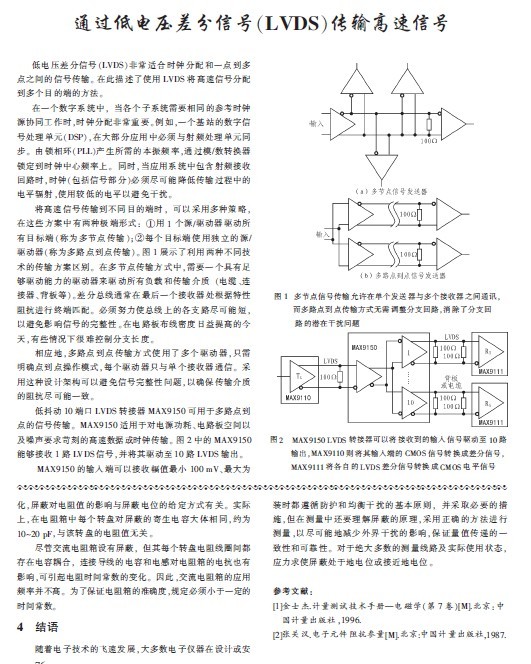

在某些应用程序中,单个数据源需要将LVDS数据发送到两个目的地。一个示例是单个视频源,它将数据发送到两个LCD面板,就像在汽车后座娱乐系统中可能会看到的那样。传统上,SERDES链路是点对点的单个发送器,通过电缆或电路板将串行数据发送到单个接收器。如果系统要求将相同的数据发送到两个目的地,则需要两个完整的链接(4个SERDES芯片和2条电缆)。图1中显示了一个示例。为方便显示图片,将显示器靠近在一起显示,但在最终应用中,显示器之间可能相距一米或更多。

提出一种允许系统设计人员拆分LVDS电缆的技术,以便单个ISL76341或ISL76321发送器可以驱动两个接收器。这样可以从BOM中省去一个SERDES芯片,并缩短了系统中的电缆总长度。在整个数据路径中保持100Ω差分阻抗环境对于消除反射和维持共模电压至关重要。由于这是降低成本的标准电路板,因此必须采用设计技术。

分离器设计

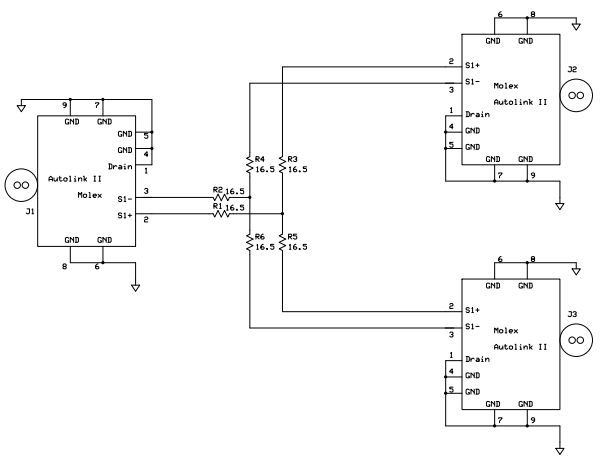

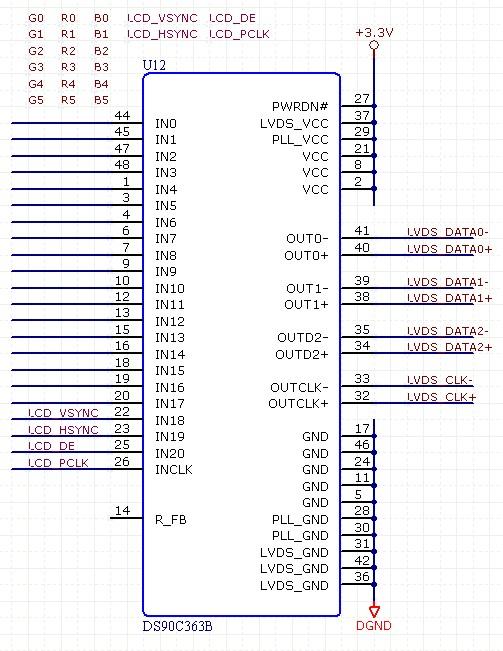

为了实现这些目标,需要将单个板添加到系统中,以将LVDS信号分成两个相同的信号。虽然预计会有一些信号损失,但我们希望将其降至最低。必须保持信号完整性,以免增加EMI。隔板的原理图如图2所示。

图2 LVDS分离器原理图

每个发射器和接收器的阻抗均为100。分析上部分支时,我们从该100Ω开始。当我们将R3和R4相加时,该分支的阻抗为133Ω。并联的两个接收器分支的阻抗为66.5Ω。最后,从发射器输出看,我们将来自发射支路R1和R2的两个串联电阻的33Ω相加,总计为99.5Ω。每个分支的分析都相同,因此每个SERDES芯片承受100Ω负载。六个16.5Ω电阻是标准的1%SMT值。这些电阻流过的电流很小,因此可以使用任何尺寸的SMT电阻。

电路板设计

分离器可以以2层或4层板设计实现。关键在于维持50Ω单端和100Ω差分传输线环境。造成这一挑战的原因是,由于信号需要交叉,因此至少有一对需要从电路板的顶层到底层。对于4层板,通过将内部层用作参考平面(GND)并将顶层和底层用作信号,可以更轻松地保持阻抗控制。信号路径中所需的过孔只会增加少量电感,而特性阻抗的变化可忽略不计。

编辑:hfy

-

接收器

+关注

关注

15文章

2637浏览量

76314 -

分离器

+关注

关注

1文章

84浏览量

16548 -

发射器

+关注

关注

7文章

916浏览量

55131 -

lvds

+关注

关注

2文章

1216浏览量

69119

发布评论请先 登录

FPGA编程LVDS信号图像处理技术

LVDS低电压差分信号

什么是lvds信号

LVDS信号电平特性

LVDS信号的PCB设计

LVDS技术原理和设计简介

电感分裂式推挽换向软开关技术的研究

LVDS信号的PCB设计和仿真分析

浅谈分离LVDS信号设计技术

浅谈分裂LVDS信号设计技术

浅谈分裂LVDS信号设计技术

评论