挑战和响应认证需要 MAC 发起者和 MAC 接收者根据隐藏的秘密和公共数据计算消息认证代码。发起者通常是 SHA-1 身份验证者或带有 SHA-1 引擎的受保护内存。MAC 接收方是应用程序的主机处理器。本应用笔记介绍了 DSSHA1 可合成 SHA-1 协处理器,它可以在专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA) 中实现,作为 DS2460 SHA-1 协处理器或基于微处理器的实现的替代方案.

质询和响应身份验证基于消息身份验证代码 (MAC) 的计算。该方法涉及两个实体,即 MAC 发起者和 MAC 接收者,它们共享一个隐藏的秘密。为了证明 MAC 发起者的真实性,MAC 接收者生成一个随机数并将其作为挑战发送给发起者。然后,MAC 发起者必须根据秘密、消息和质询计算新的 MAC,并将其发送回接收者。如果发起者证明能够为任何挑战生成有效的 MAC,则可以非常确定它知道该秘密,因此可以被认为是真实的。SHA-1 是一种经过彻底审查和国际认证的计算消息身份验证代码的算法,它是由美国国家标准与技术研究院 (NIST) 开发的。

Maxim 制造了一系列采用 SHA-1 算法的认证设备。教程 3675“通过安全认证保护研发投资”以安全存储器和 DS2460 SHA-1 协处理器的形式解释了 Maxim 认证解决方案。DSSHA1 存储器映射 SHA-1 协处理器允许在专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA) 中实现 DS2460 的计算能力,从而无需开发软件来执行复杂的 SHA -1 计算。DSSHA1 或 DS2460 计算出的 MAC 仅适用于 Maxim SHA-1 器件。

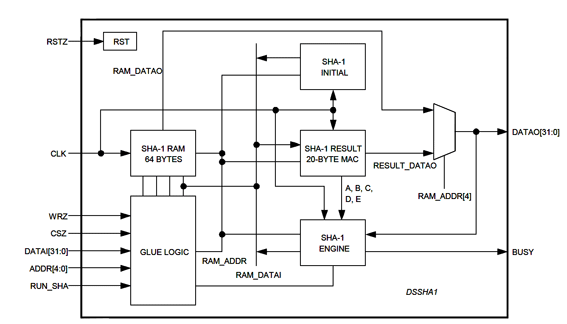

DSSHA1 是一个可合成的、内存映射的 SHA-1 协处理器,它包括一个 64 字节的通用 RAM,用于存储 64 字节的消息。输入消息用于计算 SHA-1 MAC。DSSHA1 输入和输出端口信号设计为在内部连接到 32 位总线。通过正面的比较结果,在主机系统和从属附件之间实现了认证安全。

图 1 显示了 DSSHA1 框图。表 1 描述了将 DSSHA1 连接到主机系统的信号。使用数据总线输入、地址和控制信号,将 64 字节 SHA-1 消息插入到 RAM 中。将输入信号 RUN_SHA 触发为逻辑高电平将启动 SHA-1 计算。输出 BUSY 信号指示正在发生的计算。完成 BUSY 信号后,结果寄存器包含 20 字节的消息摘要以供读取。

编辑:hfy

-

存储器

+关注

关注

39文章

7753浏览量

172158 -

微处理器

+关注

关注

11文章

2439浏览量

86125 -

Mac

+关注

关注

0文章

1131浏览量

55534

发布评论请先 登录

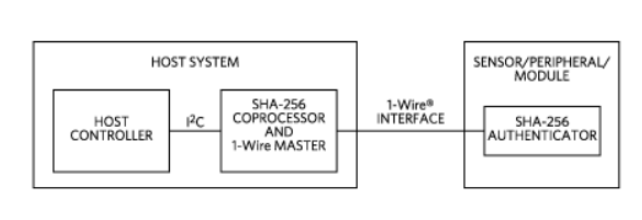

DS2465 SHA-256协处理器与1-Wire主机功能

如何通过使用FPGA高速实现SHA-1消息认证算法?

带有EEPROM的SHA1协处理器DS2460电子资料

基于SHA-1的邮件去重算法

为什么1-Wire SHA-1器件是安全的?

DSSHA1 内存映射的SHA-1协处理器

DSSHA1数据资料(英文)

Understanding the DSSHA1 Synthesizable SHA-1 Coprocessor

dssha1综合SHA-1协处理器

基于SHA-1算法的硬件设计及实现(FPGA实现)

安全协处理器/1-Wire® 主控器实现SHA-256认证

浅谈DSSHA1可综合SHA-1协处理器

浅谈DSSHA1可综合SHA-1协处理器

评论