原子层刻蚀和沉积工艺利用自限性反应,提供原子级控制。 泛林集团先进技术发展事业部公司副总裁潘阳博士 分享了他对这个话题的看法。

技术节点的每次进步都要求对制造工艺变化进行更严格的控制。最先进的工艺现在可以达到仅7 nm的fin宽度,比30个硅原子稍大一点。半导体制造已经跨越了从纳米级到原子级工艺的门槛。工程师现在必须关注结构的尺寸变化,仅相当于几个原子大小。由于多重图案模式等复杂集成增加了工艺数量,进一步限制了每个步骤允许的变化。3D NAND和finFET结构的复杂性会带来更高挑战。

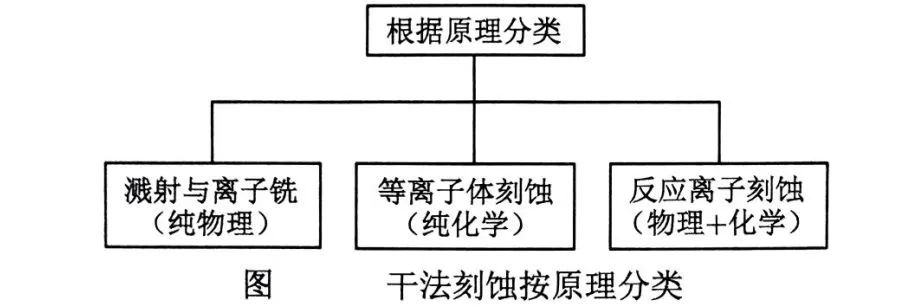

对于半导体行业而言,控制工艺变化始终都是一大关键挑战,因为它会直接影响到产品的性能、良率和可靠性,进而产生重大经济后果。工艺诱生的变化有多个来源,包括晶粒、晶圆和工具。要控制这些变化,一种方式是通过运用原子层沉积 (ALD) 和原子层刻蚀 (ALE) 等技术,这些技术本身比传统等离子体方法更加精确。

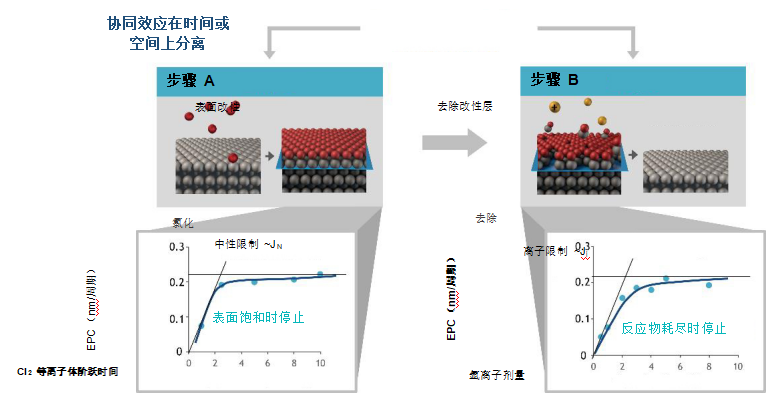

图 1. 原子层工艺中的所有半周期反应是自限性反应。

原子层工艺

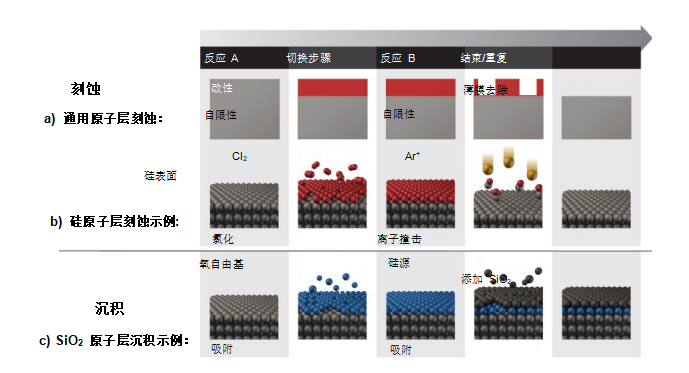

原子层工艺包括沉积和刻蚀解决方案,它们具有一些共同的特征。与连续工艺不同,它们分周期进行,每个周期都会添加或去除有限固定数量的分子层。每个周期又分为若干半周期,每个半周期分别是不同的自限性工艺,为下个半周期准备表面。例如,在 SiO2 沉积中(图1和2),第一个半周期会吸附氧原子,这个过程是自限性的,受到结合位点的限制。然后,多余的氧被从腔室中清除,表面暴露在硅原子源下,硅原子与吸附的氧发生反应,形成一层 SiO2。这个半周期工艺也是自限性的,在这种情况下,它受到氧的限制。原子层沉积的自限和有序的特性在先进逻辑和存储器芯片HVM中得到了广泛应用。

与沉积技术相同,原子层刻蚀同样分为若干半周期进行,这些半周期也是自限性的。例如,在硅刻蚀工艺中,第一个半周期将硅表面暴露在氯下,氯与第一层硅原子结合,弱化它们与底层原子的键合(图2)。当表面饱和时,该过程停止,然后清除未使用的氯。第二个半周期使用氩离子来撞击改性表面,去掉氯激活的硅顶层,而不是底层硅。氯化层去掉之后,周期完成,薄材料层已精确去除。

过去,要将原子层刻蚀工艺集成到大规模半导体生产中,我们会受制于相对连续刻蚀工艺来说较低的刻蚀速率。以下两个因素结合在一起,减少了较低刻蚀速率对整体产量的影响。第一个因素是特征尺寸持续减小,从而减少了要去除的材料数量,以及所需的ALE周期数。第二个因素是ALE技术的进步,例如快速气体交换技术,它们显著提高了循环速度。随着我们越来越多地需要对较小结构实现原子级控制,这种技术引起了更多关注。原子层刻蚀还提供了其他一些重要优势,包括改进的方向性(异向性)、更光滑的表面、更好的材料选择性、更均匀的刻蚀表面、较少的表面损坏和混合,消除了图案密度引起的非均匀效应,并改进了晶圆间的均匀性。

图 2. 原子层工艺能够去除或沉积材料。在以上刻蚀示例中,氯吸附到硅表面,然后通过氩离子撞击去除改性层。在沉积示例中,氧吸附到硅表面,硅与改性表面层相结合,沉积二氧化硅。

创新的原子层刻蚀与原子层沉积技术解决方案

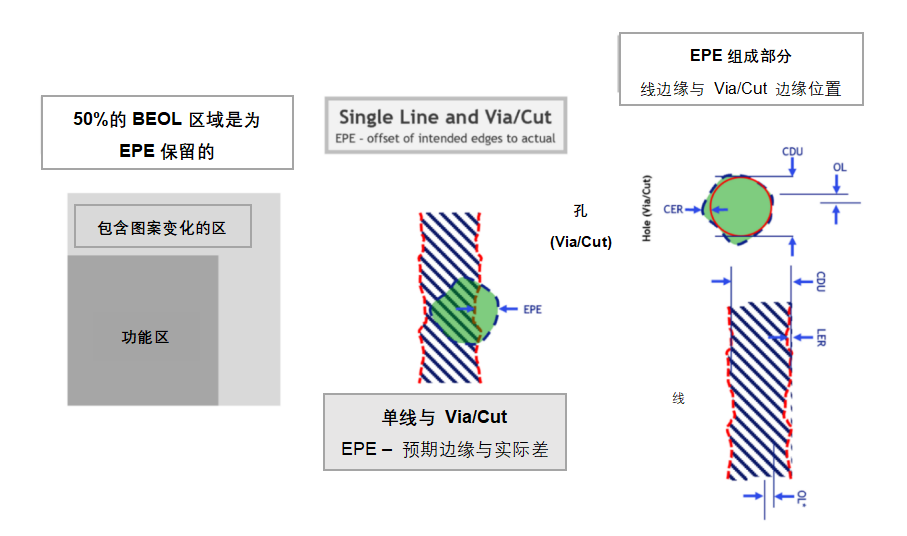

图 3. 边缘放置误差 (EPE) 最终限制空间扩展。50%的BEOL区域是为EPE保留的。因EUV光刻技术中随机缺陷引起的线和圆形边缘粗糙度极大地促进了EPE的产生。

EUV 光刻技术中的随机缺陷

在7nm和10nm节点采用EUV光刻技术的制造商面临着随机缺陷的挑战。EUV光的较短波长使其能够聚焦至更精细图案,但也意味着每个光子具有更多能量,产生更多光致酸,同时曝光更大量的光刻胶。EUV系统非常昂贵,而且必须实现较高的产量才能在成本基础上与传统 (i193) 光刻技术进行竞争,因此它们采用短曝光、低光子剂量以及以最小量光子就可以实现曝光的化学放大光刻胶 (CAR)。光刻胶中光子与光致酸在空间与时间分布上的随机变化性会导致随机缺陷,这本质上是一种统计块度,在已创建的光刻胶图案中体现为边缘和表面粗糙度。圆形边缘粗糙度 (CER) 以及线边缘粗糙度 (LER) 均是边缘定位误差 (EPE) 的组成部分,最终限制了特征尺寸可能减少的程度。在先进节点中,50% 以上的BEOL区域是为EPE保留的;设备扩展受到EPE扩展的限制而且需要节点对节点EPE下降30%(图 3)。

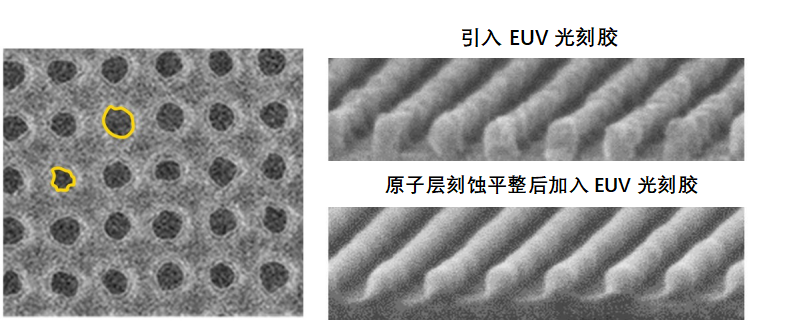

原子层刻蚀有助于减少这些随机缺陷的影响。因为它在自限性步骤中逐层进行,而且因为工艺步骤将化学活性物质与高能离子相分离,因此原子层刻蚀不会产生传统的刻蚀工艺中出现的粗糙的镶边层。更重要的是,原子层刻蚀与原子层沉积的重复循环,能够降低EUV中随机缺陷引起的粗糙度。凹凸表面比平面具有较高的表面体积比,这就导致在原子层刻蚀的过程中凸面被整平,而在原子层沉积的过程中凹面被填充。不仅随机缺陷非常小,而且在这一平整工艺过程中去除和沉积的层也非常薄,大约为半纳米。事实表明,这一工艺降低了CER并提高了小尺寸孔的CD均匀度。同样,它也降低了LER、改进了CDU,清除了细小的(小于10nm)线宽和距离中棘手的短路缺陷(图 4)。

图 4. 左图 – 黄色轮廓线表示EUV光刻技术中随机变化引起的光刻胶中孔的局部不均匀。右图 – 原子层刻蚀与原子层沉积重复循环能够显著降低光刻胶线的粗糙度。(Imec测试结构)

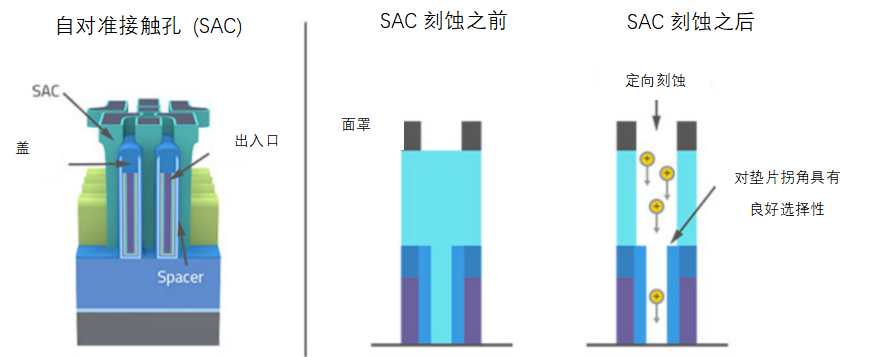

自对准接触孔刻蚀

自对准接触孔 (SAC) 通过将源极和漏极接点定位到距离栅极更近的位置而实现持续的缩放。在这一工艺中,栅极通过横向氮化硅间隔层和上覆的覆盖层与源极和漏极接点实现隔离。SAC刻蚀是最具挑战性的刻蚀工艺之一,它可以在接触点沉积之前去除相邻的二氧化硅。它必须具有高度选择性,从而清除氧化物并使氮化硅垫片保持完整。在连续刻蚀工艺中,选择性是通过沉积一个薄的氟碳聚合物涂层来实现的。在刻蚀过程中,氧化物中的可用氧分会烧掉聚合物中的碳,从而使刻蚀继续进行。而当聚合物覆盖氮化物时,没有氧分可用,而刻蚀则被抑制。问题存在于氮化硅垫片的顶处。在暴露角度为45˚-70˚时,溅射速率最大;因此,在拐角处的刻蚀速度比在平面上快,而且随着拐角变得更加圆滑,防护聚合物就更难粘附。拐角处的过度圆滑和腐蚀最终将导致栅极与源极/漏极之间的短路。

原子层刻蚀 (ALE) 通过将防护层的沉积与刻蚀步骤进行隔离,从而解决这一问题(图 5)。沉积过程中不存在离子,因此在沉积过程中存在最小溅射,且聚合物可以均匀地沉积在包含拐角的位置上。在刻蚀循环过程中,只有离子 (Ar+)存在,氧化物中的氧烧掉聚合物,而氟碳聚合物中的氟腐蚀氧化物。当聚合物消失时,氟也随之消失,如果偏压功率低于氮化硅的溅射阈值,则刻蚀停止。在氮化物上,没有氧气存在,使聚合物基本保持完整,氟的含量极低,使刻蚀得到抑制。ALE降低了拐角的圆滑度,使聚合物厚度变薄,因此可以使用更薄的垫片。ALE使用自限性半循环将表面改性步骤与主动刻蚀步骤相分离,与连续刻蚀工艺相比提供了更大的灵活性和更好的控制。(值得一提的是,通过调节各种工艺参数,可以对选择性进行逆转,优先刻蚀氮化物而非氧化物。)

图 5. 自对准接触孔采用一个横向垫片将栅极与源漏接触孔相隔离。ALE避免在垫片上角过度刻蚀,这在连续刻蚀工艺中很常见。

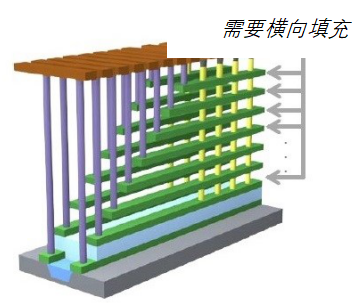

3D NAND字线的钨沉积

3D NAND利用垂直整合极大地增加了存储设备的存储密度。以往,结构局限于两个维度,通过减小尺寸从而限制密度;如今,结构在第三个维度中得以扩展。这些设备包括非常规几何图形以及极高的深宽比特征,这带来了独有的工艺挑战。

其中最具挑战性的是向字线中填充导电钨。3D NAND交替堆叠氧化物和氮化物介电层,当前一代中有多达96层,更高层数还在研发中(图 6)。密集排列且具有高深宽比的孔渗透至这些层中,按照高深宽比通道将排列分为字线。为了创建存储单元,必须移除氮化物层并以钨进行替换。这种钨必须通过深(垂直深度 50:1)通道引入,然后横向扩散,从而以无空洞的超共形沉积方式填充(之前的)氮化物水平面(横向比约 10:1)。原子层沉积能够一次沉积一个薄层,这就确保了均匀填充,并防止因堵塞而产生的空隙。

一种成功的方法就是在填充工艺中添加形状选择性抑制剂,防止在填充较高深宽比结构之前,出现较低深宽比结构中的过度沉积。由内而外的ALD工艺可以完全填充横向(水平)线且不留空隙,同时最大限度地减少了垂直通道中的沉积,从而提升了电气性能和工艺成品率。

图 6. 3D NAND采用复杂的高深宽比结构。创建字线需要超共形钨沉积,而这必须填充垂直和水平空间且不留空隙。

结语

原子层刻蚀与沉积工艺利用自限性反应,提供原子级的控制。工艺产量提升、从更小的结构中移除的材料减少、以及对原子级控制的需求不断增长,这些因素都重新引起了人们对原子层刻蚀的兴趣。原子层工艺提供的控制水平,确保其在当前乃至未来的半导体制造业中将发挥越来越重要的作用。

编辑:hfy

-

半导体行业

+关注

关注

10文章

404浏览量

41983 -

3d nand

+关注

关注

4文章

93浏览量

29703

发布评论请先 登录

半导体制造中的侧墙工艺介绍

气体检测仪贯穿半导体制造:从安全生产到工艺控制的核心应用

半导体制造中刻蚀工艺技术介绍

晶圆刻蚀清洗过滤:原子级洁净的半导体工艺核心

湿法刻蚀的工艺指标有哪些

滚珠导轨如何定义半导体制造精度?

台阶仪在半导体制造中的应用 | 精准监测沟槽刻蚀工艺的台阶高度

TSV制造技术里的通孔刻蚀与绝缘层

半导体制造中的高温氧化工艺介绍

半导体制冷机chiller在半导体工艺制程中的高精度温控应用解析

探讨半导体制造原子层刻蚀与沉积工艺的自限性反应

探讨半导体制造原子层刻蚀与沉积工艺的自限性反应

评论