时钟使能电路是同步设计的基本电路。在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理。在ASIC中可以通过STA约束让分频始终和源时钟同相,但FPGA由于器件本身和工具的限制,分频时钟和源时钟的Skew不容易控制(使用锁相环分频是个例外),难以保证分频时钟和源时钟同相,因此推荐的方法是使用时钟使能,通过使用时钟使能可以避免时钟“满天飞”的情况,进而避免了不必要的亚稳态发生,在降低设计复杂度的同时也提高了设计的可靠性。

禁止用计数器分频后的信号做其它模块的时钟,而要用改成时钟使能的方式。否则这种时钟满天飞的方式对设计的可靠性极为不利,也大大增加了静态时序分析的复杂性。

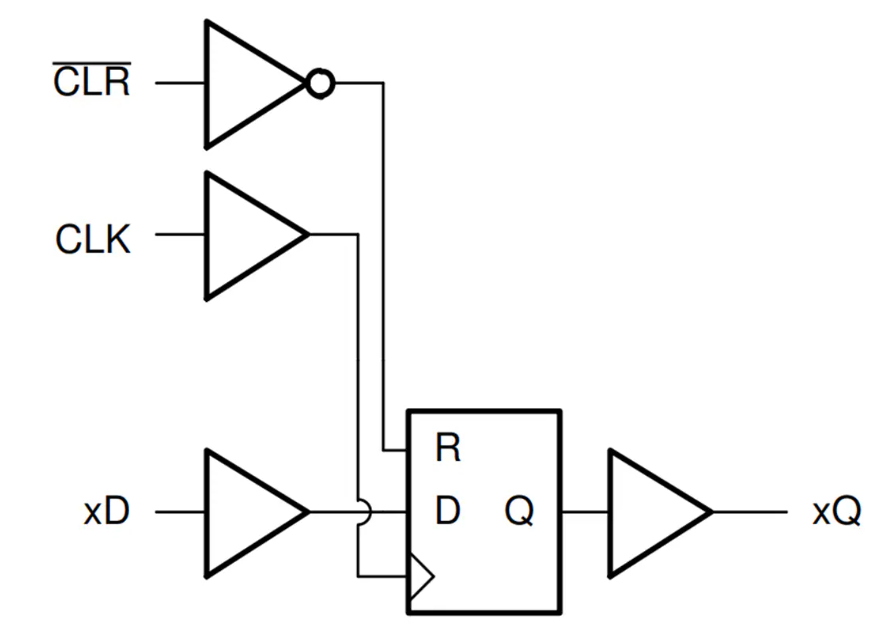

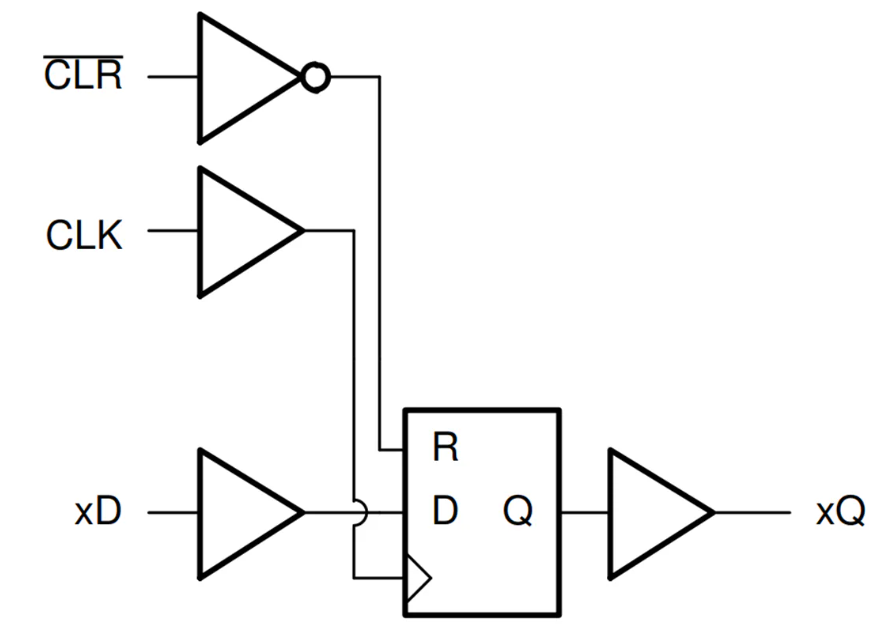

带使能端的D触发器,比一般D触发器多了使能端,只有在使能信号EN有效时,数据才能从D端被打入D触发器,否则Q端输出不改变。

我们可以用带使能端的D触发器来实现时钟使能的功能。

verilog模型举例

在某系统中,前级数据输入位宽为8位,而后级的数据输出位宽为32,我们需要将8bit数据转换为32bit,由于后级的处理位宽为前级的4倍,因此后级处理的时钟频率也将下降为前级的1/4,若不使用时钟使能,则要将前级的时钟进行4分频来作后级处理的时钟。这种设计方法会引入新的时钟域,处理上需要采取多时钟域处理的方式,因而在设计复杂度提高的同时系统的可靠性也将降低。为了避免以上问题,我们采用了时钟使能以减少设计复杂度。

例1:采用时钟使能

module clk_en(clk, rst_n, data_in, data_out); input clk; input rst_n; input [7:0] data_in; output [31:0] data_out; reg [31:0] data_out; reg [31:0] data_shift; reg [1:0] cnt; reg clken; always @(posedge clk or negedge rst_n) begin if (!rst_n) cnt <= 0; else cnt <= cnt + 1; end always @(posedge clk or negedge rst_n) begin if (!rst_n) clken <= 0; else if (cnt == 2'b01) clken <= 1; else clken <= 0; end always @(posedge clk or negedge rst_n) begin if (!rst_n) data_shift <= 0; else data_shift <= {data_shift[23:0],data_in}; end always @(posedge clk or negedge rst_n) begin if (!rst_n) data_out <= 0; else if (clken == 1'b1) data_out <= data_shift; end endmodule

例2:采用分频方法

module clk_en1(clk, rst_n, data_in, data_out);

input clk;

input rst_n;

input [7:0] data_in;

output [31:0] data_out;

reg [31:0] data_out;

reg [31:0] data_shift;

reg [1:0] cnt;

wire clken;

always @(posedge clk or negedge rst_n)

begin

if (!rst_n)

cnt <= 0;

else

cnt <= cnt + 1;

end

assign clken = cnt[1];

always @(posedge clk or negedge rst_n)

begin

if (!rst_n)

data_shift <= 0;

else

data_shift <= {data_shift[23:0],data_in};

end

always @(posedge clken or negedge rst_n)

begin

if (!rst_n)

data_out <= 0;

else

data_out <= data_shift;

end

endmodule

编辑:hfy

-

FPGA

+关注

关注

1664文章

22502浏览量

639176 -

asic

+关注

关注

34文章

1278浏览量

124941 -

Verilog

+关注

关注

31文章

1374浏览量

114718 -

时钟

+关注

关注

11文章

1999浏览量

135230 -

D触发器

+关注

关注

3文章

181浏览量

49896

发布评论请先 登录

深度解析 74HCT574:八位 D 型正边沿触发触发器的多功能应用

74LVC374A:8位D型正边沿触发触发器的深度解析

74LVTN16374:高性能16位D型边缘触发触发器的深度解析

74LVC74:双D型正边沿触发触发器的深度解析

74LVC1G74:单D型正边缘触发触发器的卓越之选

74HC574:八进制D型正边沿触发触发器的详细解析

74HC374:八进制D型正边沿触发触发器的详细解析

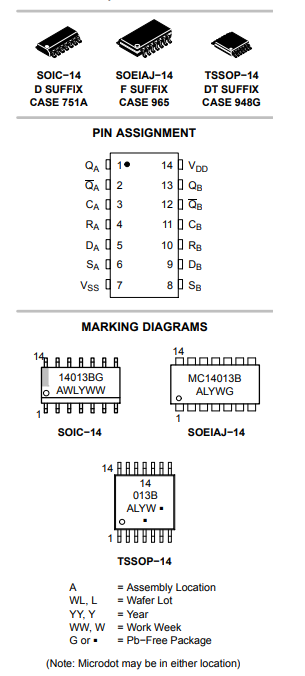

CD4013BNSR CMOS 双通道 D 类触发器

MC74VHCT374A Octal D型触发器技术解析与应用指南

SN74AHCT374-Q1 汽车级八路边沿触发D型触发器数据手册摘要

SN74LV8T273 八路D型触发器技术文档总结

Texas Instruments SN74ACT174-Q1六路D型触发器数据手册

Texas Instruments SN74AC174-Q1六路D型触发器数据手册

ON Semiconductor MC14013BDTR2G 双D型触发器参数特性 EDA模型 数据手册

verilog模型举例:利用D触发器实现时钟使能

verilog模型举例:利用D触发器实现时钟使能

评论