互联结构包括直通模式、只转换模式、N-1互联模式、N-M互联模式。

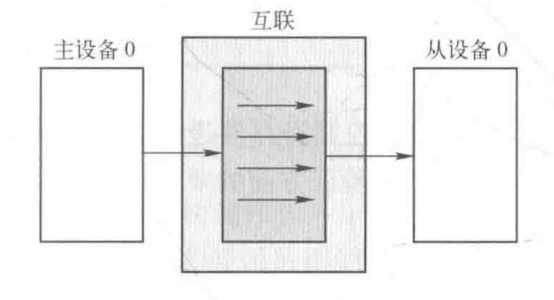

1. 直通模式

当只有一个主设备和一个从设备使用AXI互联时,AXI互联不执行任何转换或流水线功能,AXI互联结构退化成直接的线连接。在这种模式下,没有延迟,同时不消耗逻辑资源。

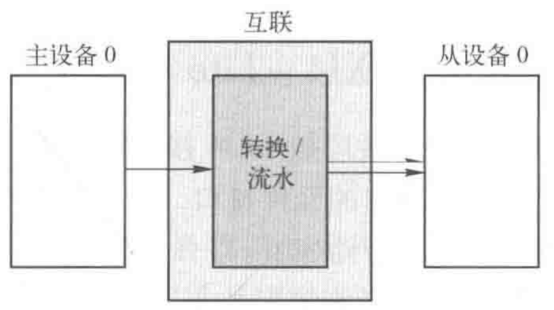

2. 只转换模式

当连接一个主设备和一个从设备时,AXI互联执行不同的转换和流水线功能:数据位宽转换、时钟速率转换、AXI-Lite从适应、AXI-3从适应、流水线。在只转换模式下,AXI互联不包含仲裁、解码或布线逻辑,但是可能产生延迟。

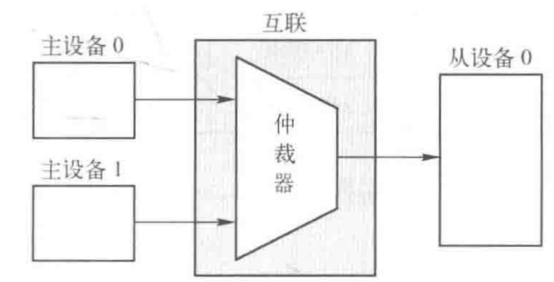

3. N-1互联模式

N-1互联模式是多个主设备访问一个从设备,典型地,一个存储器控制器,很显然需要仲裁逻辑。这种情况下,AXI互联不需要地址译码逻辑。在这种配置中,也可以执行数据宽度和时钟速率转换。

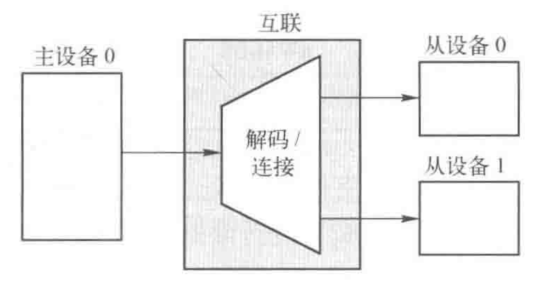

4. 1-N互联模式

1-N互联结构是一个主设备访问多个存储器映射的从外设。在这种模式下,AXI互联不执行仲裁。

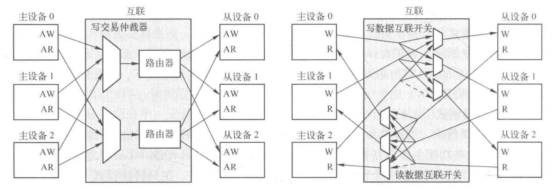

5. N-M互联模式

AXI互联提供了一种共享地址多数据流拓扑结构,这种结构包含稀疏的数据交叉开关连接、单线程写和读地址仲裁。

编辑:hfy

-

Zynq

+关注

关注

10文章

625浏览量

49243 -

AXI

+关注

关注

1文章

143浏览量

17793 -

存储器控制器

+关注

关注

0文章

8浏览量

4956

发布评论请先 登录

NVMe IP之AXI4总线分析

看看在SpinalHDL中AXI4总线互联IP的设计

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南

全面介绍ZYNQ-AXI互联IP

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3与AXI4写响应的依赖区别

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

漫谈AMBA总线-AXI4协议的基本介绍

zynq中AXI4的五种互联结构介绍

zynq中AXI4的五种互联结构介绍

评论