描述:

在《Virtex UltraScale+ FPGA 数据手册》(DS923) 中,XCVU27P-3E 器件和 XCVU29P-3E 器件的最低量产软件和速度规格已从 Vivado 工具 2019.2 v1.28 更新至 Vivado 工具 2020.1.1 v1.30。

XCVU27P-3E 器件和 XCVU29P-3E 器件的速度文件参数以及速度/温度等级在 2020.1.1 版中已更新,包括已纠正了集成块接口建立时间和保持时间参数。

受此影响的主要集成块包括:PCIe、Interlaken 和 100G Ethernet MAC。

速度文件更新中,部分参数要求已放宽,部分参数要求则进一步收紧。

解决方案:

对于 XCVU27P-3E 器件和 XCVU29P-3E 器件以及速度/温度等级设计,请使用 Vivado Design Suite 2020.1.1 或更高版本。

您可通过以下方式来评估时序问题对于您使用 Vivado 工具 2019.2 - 2020.1 所构建的设计产生的影响:在 Vivado 2020.1.1 或更高版本中,对已完全实现的设计检查点 (.dcp) 文件重新运行时序分析。

如果您的比特流是使用 Vivado 工程模式生成的,则必须找到已完全实现的 .dcp 文件。

通常,已完全实现的 .dcp 文件应位于如下某一路径中,具体取决于布线后是否已启用 phys_opt_design。

project_myDesign.runs/impl_1/myDesign_routed.dcp

project_myDesign.runs/impl_1/myDesign_postroute_physopt.dcp

例如,如果已完全实现的 .dcp 文件为 myDesign_routed.dcp,则上述命令应如下所示:

#Open the final dcp for the finished design open_checkpoint project_myDesign.runs/impl_1/myDesign_routed.dcp #Report timing report_timing_summary -file myDesign_timing_summary_routed.rpt

如果在受影响的主要集成块上出现时序违例,则必须在 Vivado 2020.1.1 或更高版本中对设计进行重新编译以达成时序收敛。

原文标题:面向 XCVU27P-3E 器件和 XCVU29P-3E 器件的 Vivado 2020.1.1 量产速度文件更新

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

-

PCIe

+关注

关注

16文章

1421浏览量

87548 -

Vivado

+关注

关注

19文章

846浏览量

70474

原文标题:面向 XCVU27P-3E 器件和 XCVU29P-3E 器件的 Vivado 2020.1.1 量产速度文件更新

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

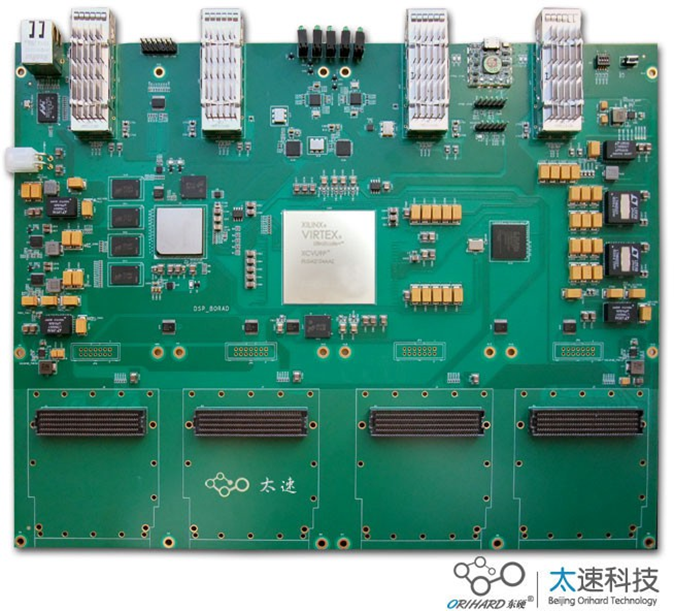

设计原理图:U200E 基于VU9P的4路QSFP28光纤PCIeX16收发卡

集中式ZDM-E0400P3热电阻RTD测温模块(1) — 基础应用

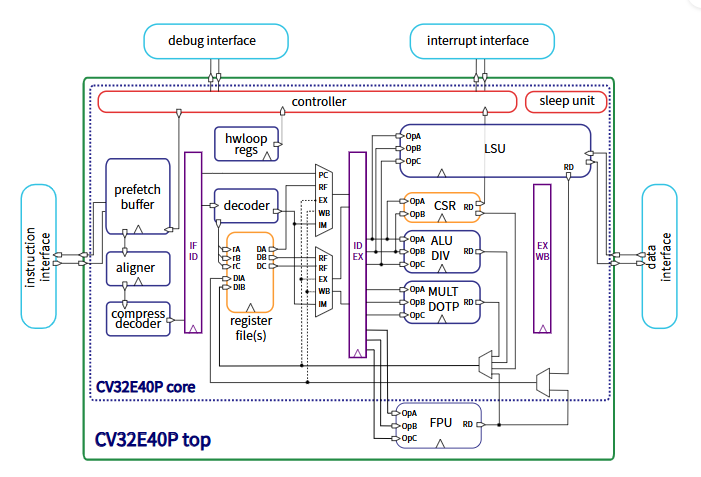

CORE-V(OpenHW Group)CV32E40P 详细解读

DD20-48E0524B3C3 DD20-48E0524B3C3

PDD12-18E0507A3C2 PDD12-18E0507A3C2

DD10-36E0524A3R2 DD10-36E0524A3R2

DD10-36S24E3C2 DD10-36S24E3C2

PFD6-18D18E2(C)3 PFD6-18D18E2(C)3

DD6-05S24E3C2 DD6-05S24E3C2

FK6-36S24E2C3 FK6-36S24E2C3

KW3-24D24E3R3 KW3-24D24E3R3

KW1-24D15E3R3 KW1-24D15E3R3

DA10-220S3V3P2D4 DA10-220S3V3P2D4

XCVU27P-3E和 XCVU29P-3E的速度文件参数已更新

XCVU27P-3E和 XCVU29P-3E的速度文件参数已更新

评论