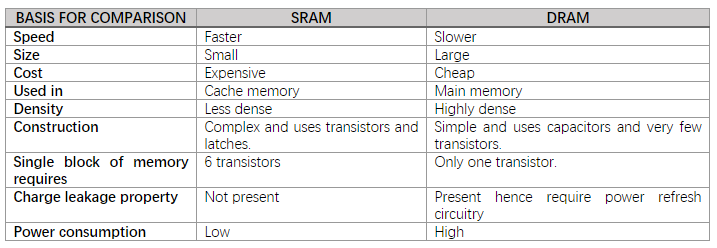

SRAM VS DRAM

SRAM如何运作

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DRAM

+关注

关注

40文章

2373浏览量

188164 -

sram

+关注

关注

6文章

808浏览量

117223

原文标题:SRAM与DRAM真正区别,你真的明白吗

文章出处:【微信号:gh_c472c2199c88,微信公众号:嵌入式微处理器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

DRAM,SRAM,SDRAM的关系与区别

一般不是行列地址复用的SDRAM-------同步的DRAM,即数据的读写需要时钟来同步问题2:为什么DRAM要刷新,SRAM则不需要?答:这是由RAM的设计类型决定的,

发表于 08-15 17:11

EEPROM、EPROM、FLASH、SRAM、DRAM、SDRAM的区别.

本帖最后由 eehome 于 2013-1-5 10:01 编辑

EEPROM、EPROM、FLASH、SRAM、DRAM、SDRAM的区别.

发表于 12-20 15:19

ROM、RAM、DRAM、SRAM和FLASH的区别

求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。另一种称为动态RAM(Dynamic RAM/DRAM),DRAM保留数据的时间很短,速度也比S

发表于 11-04 10:09

请问串口SRAM和并口SRAM的引脚区别?

首先来看一下并口和串口的区别:引脚的区别: 串口SRAM(或其它存储器)通常有如下的示意图: 串口SRAM引脚引脚只有SCK,CS#,SI,

发表于 06-17 16:26

DRAM,SRAM,FLASH和新型NVRAM:有何区别?

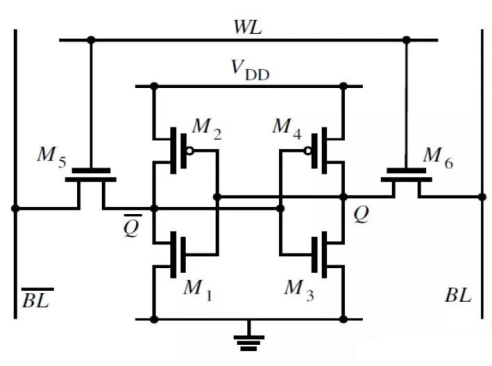

但是,SRAM的每个位昂贵得多,因为它需要六个晶体管,而DRAM则需要一个晶体管和电容器。因此,通常在仅需要少量高速存储器的CPU高速缓存中找到SRAM。FlashFLASH是

发表于 09-25 08:01

串口SRAM和并口SRAM的引脚区别是什么

首先来看一下并口和串口的区别: 引脚的区别: 串口SRAM(或其它存储器)通常有如下的示意图: 串口SRAM引脚 引脚只有S

发表于 12-10 16:42

一文详解SRAM特点和原理

SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此

发表于 05-30 07:18

•2.3w次阅读

DRAM、SRAM和Flash原理解析

DRAM、SRAM和Flash都属于存储器,DRAM通常被称为内存,也有些朋友会把手机中的Flash闪存误会成内存。SRAM的存在感相对较弱,但他却是CPU性能发挥的关键。

发表于 07-29 11:14

•1.4w次阅读

SRAM和DRAM的区别

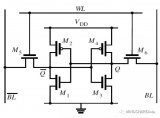

SRAM的S是Static的缩写,全称是静态随机存取存储器。而DRAM的D是Dynamic的缩写,全称是动态随机存取存储器。这两者有什么区别呢?首先我们看看SRAM的结构,你可以网上搜

一文读懂SRAM和DRAM资料下载

电子发烧友网为你提供一文读懂SRAM和DRAM资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大

发表于 04-15 08:40

•17次下载

SRAM和DRAM有什么区别

型的随机存取存储器(RAM),它们在多个方面存在显著差异。以下将从定义、工作原理、性能特点、应用场合以及发展趋势等方面详细阐述SRAM和DRAM的区别。

SRAM与DRAM的结构差异和特性区别

的定位,仍是高性能计算场景下的重要基石。理解二者的根本差异,有助于我们在不同应用场景中做出更合适的技术选型与优化策略。接下来我们就来讲讲SRAM与DRAM具体有哪些区别。

一文看清SRAM与DRAM真正区别!

一文看清SRAM与DRAM真正区别!

评论