AMD今天公布的好消息太多了,都让人有点眼花缭乱了,去年是CPU、GPU同时升级7nm,2020年虽然不会有新工艺,但CPU、GPU架构也全面升级了。

对AMD来说,这两年最大的变化当属CPU工艺,随着台积电的7nm量产,AMD代工厂从GF转向台积电这一步是押对宝了,确保了Zen处理器路线图能够长期稳定发展下去。

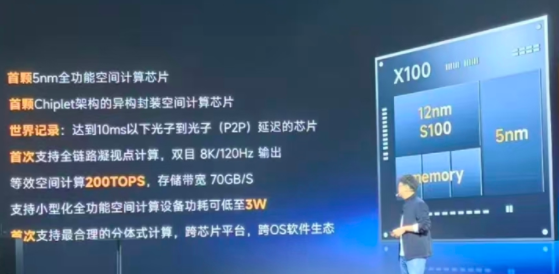

今天AMD官方公布了Zen4架构,也确定了会用上5nm工艺,这将是首个5nm X86处理器。

在这次的分析师大会上,AMD还对比了自家CPU的工艺与竞争对手的工艺,指出AMD在2022年之前都会保持工艺优势。

AMD的对比数据没有提及友商名字,不过大家都知道是谁,对比的指标也是晶体管密度及每瓦性能比,这是CPU工艺的关键指标之一。

在晶体管密度上,友商在14nm上肯定是没什么优势了,不过10nm节点追赶的很快,AMD使用的7nm勉强可以达到1亿晶体管/mm2,友商的10nm节点就有这样的水平了。

AMD在7nm之后会转向5nm,台积电说法是晶体管密度提升80%,友商在10nm之后会转向7nm,不过7nm的关键参数都没公布。

2022年的时候,AMD已经上了5nm,友商这时候依然会是7nm工艺,AMD的PPT显示他们在晶体管密度上依然小有优势。

至于每瓦性能比,友商追赶的速度比晶体管密度更甚,AMD使用的7nm相比10nm还有一定的优势,但是到了2022年两家的每瓦性能比就几乎一致了。

从工艺上来看,AMD对友商的实力还是有清醒认识的,虽然最近几年在14nm、10nm节点上落后了一些,但是性能、密度优势不容忽视,2022年双方的差距就会急速缩小。

当然,2022年的时候AMD也绝对称不上落后,总体上依然小有优势,只是不会再有7nm vs.14nm这样明显的落差了。

除了CPU工艺,AMD在封装工艺上也会加速,尽管他们在MCM多模封装、Chiplets小芯片设计上领先了,但是在2.5D/3D封装上面,AMD实际上是要比友商的EMIB、Foveros封装是要落后的。

当然,友商的3D封装技术虽然先进,但是在实际进度上却不尽如人意,真正落地的产品没几个,现在也就Lakefield这一个而已,AMD追赶依然有机会。

AMD现在也宣布了新一代的X3D封装,混合2.5D及3D封装,带宽密度提升了10倍,不过详情欠奉,具体细节及发布时间还有待公布。

责任编辑:wv

-

处理器

+关注

关注

68文章

20148浏览量

246942 -

amd

+关注

关注

25文章

5647浏览量

138997

发布评论请先 登录

那么龙芯CPU性能如何呢?

元服务上架自检

基于蜂鸟E203架构的指令集K扩展

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

创飞芯40nm HV工艺OTP IP完成上架

江波龙企业级DDR5 RDIMM率先完成AMD Threadripper PRO 9000WX系列兼容性认证

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

千亿美元打水漂,传三星取消1.4nm晶圆代工工艺

千亿美元打水漂,传三星取消1.4nm晶圆代工工艺

专访AMD王启尚 从RDNA 4到FSR 4,AMD GPU技术创新引领行业新发展

AMD官方确定Zen4架构会用上5nm工艺 且表示在2022年之前都会保持工艺优势

AMD官方确定Zen4架构会用上5nm工艺 且表示在2022年之前都会保持工艺优势

评论