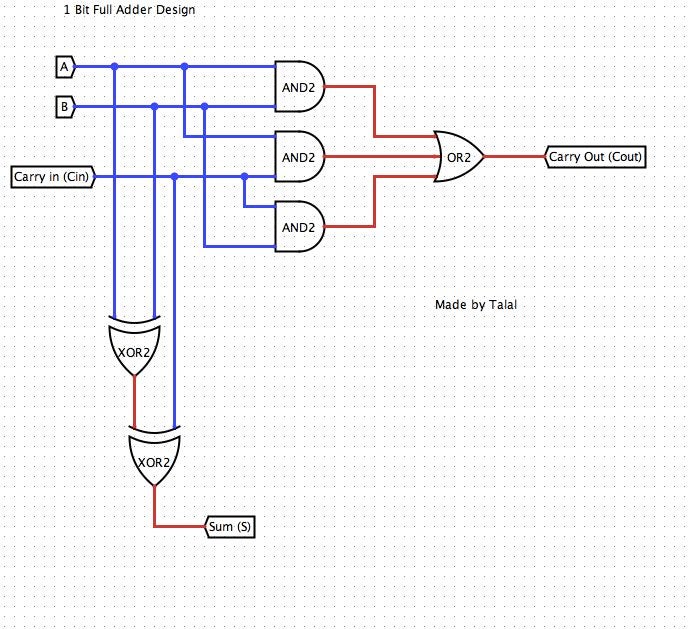

步骤1:推导出真值表布尔函数和原理图

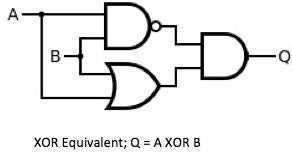

显示了一位完整加法器的真值表在第一个图中;使用真值表,我们能够导出求和和进位的布尔函数,如第二张附图所示。此外,派生的布尔函数将我们引向一位全加器的示意图设计。最后,我没有任何XOR IC芯片,所以我使用了等效的XOR混合门,如上图所示。

步骤2:在面包板上实现

如果开关处于打开状态,则表示关闭。

如果开关处于断开状态,则表示打开。

白线代表A。

蓝线代表B。

黄线代表[Cin]进位。

绿色LED代表总和。

红色LED代表进位(Cout)。

责任编辑:wv

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

加法器

+关注

关注

6文章

183浏览量

31233

发布评论请先 登录

相关推荐

热点推荐

E203V2长周期乘法器核心booth算法解读

解决,以下为数据通道中加法器的操作数选择:

此外,在乘法器运算中部分和作为加法器的一个操作数,两个32位数相乘,则如前所述共有16个部分和

发表于 10-24 09:33

如何在vivado上基于二进制码对指令运行状态进行判断

在扩展指令时我们常常需要一些手段来帮助我们判断指令是否能够成功运行、运行状态是否正确。一方面,我们可以通过模拟器来实现,另一方面,在没有模拟器的情况下,我们可以通过将所扩展指令的二进制

发表于 10-24 06:46

e203乘法运算结构及算法原理

Booth算法

对于普通的乘法运算,以两个8比特二进制数为例,可以写为图一所示的8个部分积之和:

同理,两个32位二进制数相乘,在扩展符号位

发表于 10-22 06:43

e203 ALU乘法运算结构及算法原理

Booth算法

对于普通的乘法运算,以两个8比特二进制数为例,可以写为图一所示的8个部分积之和

同理,两个32位二进制数相乘,在扩展符号位

发表于 10-22 06:12

除法器工作原理介绍

二进制除法器的本质是多次减法,直到余数小于除数为止。对应的两个N bit二进制数的除法算法如下。

1、设置2N bit寄存器A的低N位存放被除数,设置2N bit寄存器B的高N

发表于 10-21 08:32

数字IC设计中的除法器的工作原理

除法器介绍

二进制除法器的本质是多次减法,直到余数小于除数为止。对应的两个N bit二进制数的除法算法如下。

1、设置2N bit寄存器A的低N位

发表于 10-21 07:20

bcd编码的应用 bcd与二进制的区别

BCD(Binary-Coded Decimal)编码是一种二进制编码形式,用于表示十进制数字。它将每个十进制数字(0-9)直接编码为一个四

怎样构建并测试一位二进制完全加法器

怎样构建并测试一位二进制完全加法器

评论