Altera寻找HDL工具

SANTA CRUZ,加利福尼亚州Altera公司已宣布OEM交易,以转售合成和模拟产品,这是对第三方EDA工具的最强支持Synopsys和Mentor Graphics的工具。这些交易强调了基于HDL的合成和仿真在高密度FPGA设计中日益增长的重要性。

作为Quartus和Max + Plus II开发环境的一部分,Altera将提供Synopsys的FPGA Express或Mentor的Exemplar LeonardoSpectrum选择。综合工具。 Altera还将提供Mentor的Model Technology ModelSim VHDL和Verilog仿真器。

Altera工具定价将保持相同,基于PC的许可证每年订购2,000美元,Synopsys和Mentor工具将在3月份作为升级发送给大约20,000名当前用户,这是最大的注入之一迄今为止基于HDL的设计工具。 OEM工具仅适用于Altera器件。

Altera历来选择进行自己的工具开发,目前提供自己的VHDL和Verilog综合作为Quartus和Max + Plus II封装的一部分。 Altera市场营销高级副总裁Erik Cleage表示,该公司已经意识到第三方综合工具在高密度逻辑方面做得更好。

“我们认为这对我们有利为客户带来最好的性能,以及这些第三方工具的形式,“Cleage说。 “它还允许我们对我们的综合开发进行优先排序,以支持改进布局和布线工具,我们认为我们可以最好地利用性能。”

Altera不提供HDL仿真器,到目前为止在其客户群中看到非常有限的HDL仿真使用。但该公司认为模拟将随着密度的增长而变得越来越重要,这就是为什么Altera选择引入ModelSim工具,Cleage说。

播种基地

Altera以来定价远低于Synopsys或Mentor对独立产品的收费,这些公司不能指望从OEM交易中赚到很多钱。但Mentor HDL部门总经理兼副总裁Anne Wagner表示,获得Altera巨大客户群的工具是一个很好的策略。

“现在我们与所有主要的FPGA公司签订了OEM协议,”她说过。 “这使我的FPGA设计工具掌握在超过85%的设计师手中。对于我们来说,这对我们来说是一个很好的交易,对我们来说是一个很大的商机。”

作为OEM交易一部分的Synopsys和Mentor工具仅提供Altera器件的库。因此,两家公司都认为有些用户需要付费才能升级到成熟的独立工具以获得通用设备支持。

Cleage注意到Altera在几年前仅在Verilog中转售了Exemplar合成,之后该公司开发了自己的Verilog合成。 Altera去年还与Synopsys合作创建了Altera特定版本的FPGA编译器,该版本可供Synopsys Design Compiler用户免费使用。

然而,最新的OEM协议是Altera最广泛的术语第三方EDA工具。 “这是我们部署第三方功能的理念上的改变,”Cleage表示。

截至今天,Cleage说,大多数使用Altera Flex和Apex设备的设计人员使用HDL综合。大多数使用较不复杂的Max器件的大多数都使用Altera的AHDL语言或原理图输入。但是使用HDL模拟的情况要少得多,因为用户可以简单地对设备进行编程,插入设备,看看是否有效。

“有些人认为更少模拟并充分利用可编程性,“克利奇说。 “坦率地说,我们推动了这一观点。但很明显,人们越来越倾向于模拟。”

Altera承诺Synopsys和Mentor工具将与Quartus和Max + Plus II紧密集成。 Altera工具营销总监Dave Greenfield说:“从一个工具到另一个工具,它将更加流畅,并且可以更有效地传递参数。”

但是, Greenfield表示,Altera设计人员仍然可以“非常有效地”使用其他第三方综合和仿真工具。

Synopsys和Mentor工具将于2000年3月推出所有新订阅,并将作为升级发送当时发货给订户。 Altera每年为基于PC的许可证收费2,000美元,基于Unix的许可证收费2,995美元。

-

Altera

+关注

关注

37文章

818浏览量

158122 -

VHDL代码

+关注

关注

2文章

13浏览量

21032 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44372

发布评论请先 登录

Altera CEO Raghib Hussain首次访华圆满落幕

使用Simulink自动生成浮点运算HDL代码(Part 1)

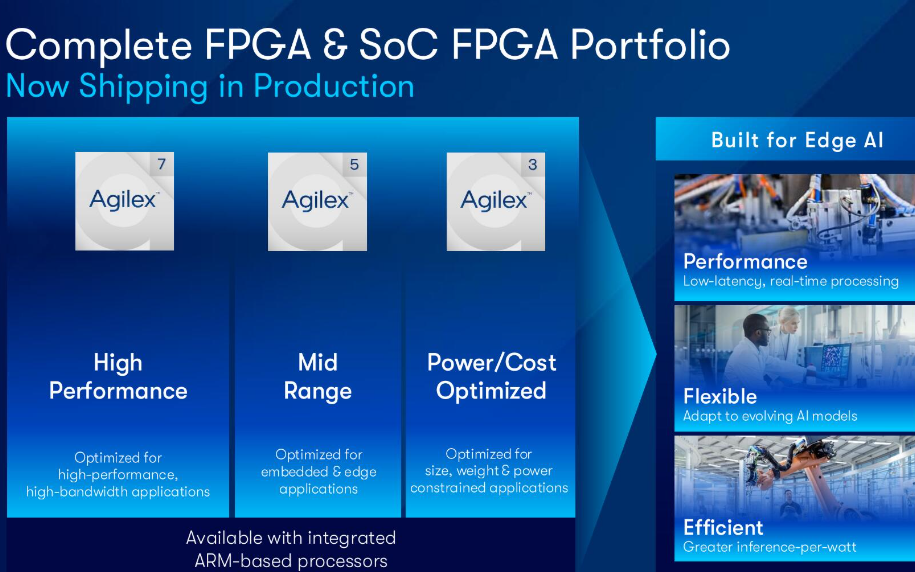

Altera进一步扩展 Agilex™ FPGA 产品组合,全面提升开发体验

银湖资本完成对Altera 51%股权的收购

使用Altera SoC FPGA提升AI信道估计效率

Altera Agilex 3 FPGA和SoC产品介绍

Altera大学成立,助力FPGA教学发展与人才培养

FPGA Verilog HDL语法之编译预处理

一文详解Verilog HDL

Altera发布最新FPGA产品和开发工具套件

Intel为什么在2015年收购Altera?现在又为什么抛弃Altera

Altera正式独立运营:FPGA行业格局将迎来新变局

Altera发布全新合作伙伴加速计划

Altera推出解决方案合作伙伴加速计划

大多数FPGA的程序存储器(FLASH)为什么都放在外面呢?FPGA的主要应用

Altera在外面寻找的HDL工具

Altera在外面寻找的HDL工具

评论