随着集成电路工艺制程技术的不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,MOS器件的特征尺寸不断缩小,MOS器件面临一系列的挑战。例如短沟道效应(Short Channel Effect - SCE),热载流子注入效应(Hot Carrier Inject - HCI)和栅氧化层漏电等问题。为了克服这些挑战,半导体业界不断开发出一系列的先进工艺技术,例如多晶硅栅、源漏离子注入自对准、LDD离子注入、polycide、Salicide、SRD、应变硅和HKMG技术。另外,晶体管也从MOSFET演变为FD-SOI、Bulk FinFET和SOI FinFET。

1.1铝栅MOS管

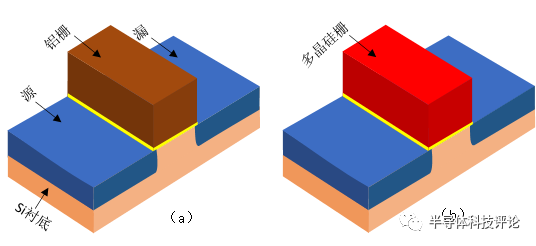

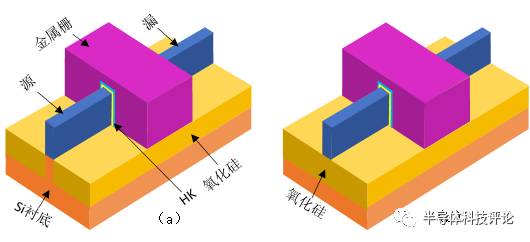

MOS诞生之初,栅极材料采用金属导体材料铝,因为铝具有非常低的电阻,它不会与氧化物发生反应,并且它的稳定性非常好。栅介质材料采用SiO2,因为SiO2可以与硅衬底形成非常理想的Si-SiO2界面。如图1.13(a)所示,是最初铝栅的MOS管结构图。

图1.13铝栅和多晶硅栅的MOS管结构图

1.2多晶硅栅MOS管

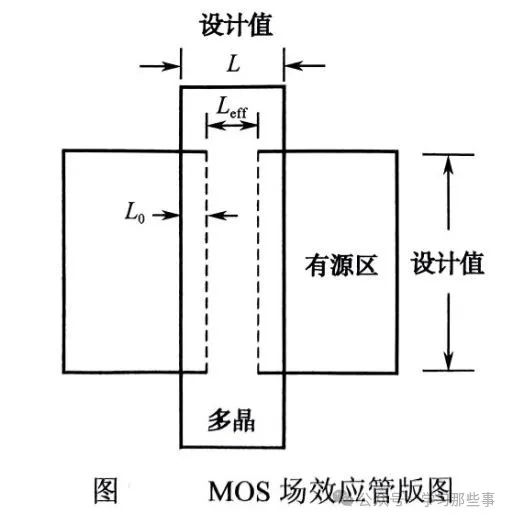

随着MOS器件的特征尺寸不断缩小,铝栅与源漏扩散区的套刻不准问题变得越来越严重,源漏与栅重叠设计导致,源漏与栅之间的寄生电容越来越严重,半导体业界利用多晶硅栅代替铝栅。多晶硅栅具有三方面的优点:第一个优点是不但多晶硅与硅工艺兼容,而且多晶硅可以耐高温退火,高温退火是离子注入的要求;第二个优点是多晶硅栅是在源漏离子注入之前形成的,源漏离子注入时,多晶硅栅可以作为遮蔽层,所以离子只会注入多晶硅栅两侧,所以源漏扩散区与多晶硅栅是自对准的;第三个优点是可以通过掺杂N型和P型杂质来改变其功函数,从而调节器件的阈值电压。因为MOS器件的阈值电压由衬底材料和栅材料功函数的差异决定的,多晶硅很好地解决了CMOS技术中的NMOS和PMOS阈值电压的调节问题。如图1.13(b)所示,是多晶硅栅的MOS管结构图。

1.3Polycide技术

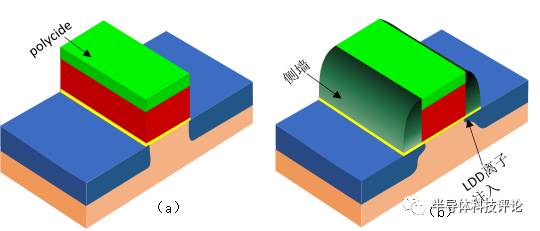

多晶硅栅的缺点是电阻率高,虽然可以通过重掺杂来降低它的电阻率,但是它的电阻率依然很高,厚度3KÅ的多晶硅的方块电阻高达36ohm/sq。虽然高电阻率的多晶硅栅对MOS器件的直流特性是没有影响的,但是它严重影响了MOS器件的高频特性,特别是随着MOS器件的特征尺寸不断缩小到亚微米(1um≥L≥0.35um),多晶硅栅电阻率高的问题变得越发严重。为了降低多晶硅栅的电阻,半导体业界利用多晶硅和金属硅化物(polycide)的双层材料代替多晶硅栅,从而降低多晶硅栅的电阻,Polycide的方块电阻只有3ohm/sq。半导体业界通用的金属硅化物材料是WSi2。如图1.14(a)所示,是多晶硅和金属硅化物栅的MOS管结构图。

1.4LDD 离子注入技术

20世纪60年代,第一代MOS器件的工作电压是5V,栅极长度是25um,随着MOS器件的特征尺寸不断缩小到亚微米,MOS器件的工作电压并没有减小,它的工作电压依然是5V,直到MOS器件栅极长度缩小到0.35um时,MOS器件的工作电压才从5V降低到3.3V。2008年,MOS器件的栅极长度缩小到45nm,MOS器件的工作电压缩小到1V。栅极长度从25um缩小到45nm,缩小的倍率是555倍,而MOS器件的工作电压只从5V缩小到1V,缩小的倍率是5倍,可见MOS器件的工作电压并不是按比例缩小的。随着MOS器件的特征尺寸不断缩小到亚微米级,MOS器件的沟道横向电场强度是不断增强的,载流子会在强电场中进行加速,当载流子的能量足够大时形成热载流子,并在强场区发生碰撞电离现象,碰撞电离会形成新的热电子和热空穴,热载流子会越过Si/SiO2界面的势垒形成栅电流,热空穴会流向衬底形成衬底电流,由热载流子形成的现象称为热载流子注入效应。随着MOS器件的特征尺寸不断缩小到亚微米,热载流子注入效应变得越来越严重,为了改善热载流子注入效应,半导体业界通过利用LDD (Lightly Doped Drain - LDD)结构改善漏端耗尽区的峰值电场来改善热载流子注入效应。如图1.14(b)所示,是利用LDD结构的MOS管结构图。

图1.14金属硅化物和LDD结构的MOS管结构图

1.5Salicide技术

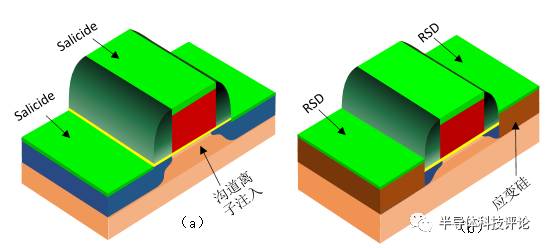

随着MOS器件的特征尺寸缩小到深亚微米(0.25um≥L),限制MOS器件缩小的主要效应是短沟道效应。为了改善短沟道效应,MOS器件的扩散区结深也不断缩小,结深不断缩小导致扩散区的电阻不断变大,因为扩散区的纵向横截面积变小,另外金属互连的接触孔的尺寸也减小到0.32um以下,接触孔变小导致接触孔与扩散区的接触电阻升高了,单个接触孔的接触电阻升高到200ohm以上。为了降低扩散区的电阻和接触孔的接触电阻,半导体业界利用硅和金属发生反应形成金属硅化物(silicide)降低扩散区的电阻和接触孔的接触电阻。可利用的金属材料有Ti、Co和Ni等,金属材料只会与硅和多晶硅发生反应形成金属硅化物,而不会与氧化物发生反应,所以Silicide也称为自对准金属硅化物Salicide(Self Aligned Silicide)。另外扩散区和多晶硅栅是同时形成Silicide,所以不需要再考虑进行多晶硅栅的polycide。如图1.15(a)所示,是Salicide的MOS管结构图。

1.6沟道离子注入和晕环离子注入技术

MOS器件的特征尺寸缩小到深亚微米导致的另外一个问题是短沟道效应引起的亚阈值漏电流。随着MOS器件的栅极长度缩小到0.25um,源漏之间的耗尽区会相互靠近,导致它们之间的势垒高度降低,形成亚阈值漏电流。虽然MOS器件的栅极长度从0.33um缩小到0.25um时,器件的工作电压也从3.3V降低到2.5V,但是MOS器件的亚阈值区的漏电流依然很大。为了降低MOS器件的亚阈值区的漏电流,需要增加一道沟道离子注入和晕环(Halo)离子注入增加沟道区域的离子浓度,从而减小源漏与衬底之间的耗尽区宽度,改善亚阈值区的漏电流。如图1.15(a)所示,进行沟道离子注入的MOS管结构图。

图1.15 Salicide和应变硅的MOS管结构图

1.7RSD和应变硅技术

随着MOS器件的特征尺寸不断缩小到90nm及以下时,短沟道效应中的器件亚阈值电流成为妨碍工艺进一步发展的主要因素,尽管提高沟道掺杂浓度可以在一定程度上抑制短沟道效应,然而高掺杂的沟道会增大库伦散射,使载流子迁移率下降,导致器件的速度降低,所以仅仅依靠缩小MOS器件的几何尺寸已经不能满足器件性能的提高,需要一些额外的工艺技术来提高器件的电学性能,例如应变硅技术。应变硅技术是通过外延生长在源漏区嵌入应变材料使沟道发生应变,从而提高载流子迁移率,最终提高器件的速度。例如NMOS的应变材料是SiC,PMOS的应变材料是SiGe。另外,随着源漏的结深的短减小,源漏扩散区的厚度已经不能满足形成Salicide的最小厚度要求,必须利用新技术RSD(Raise Source and Drain)技术来增加源漏扩散区的厚度。RSD技术是通过外延技术生长在源漏区嵌入应变材料的同时提高源漏扩散区的厚度。如图1.15(b)所示,是采用应变硅和RSD技术的MOS管结构图。

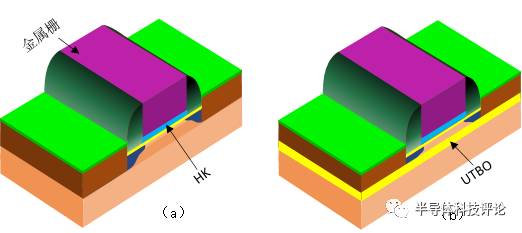

1.8HKMG技术

当MOS器件的特征尺寸不断缩小45nm及以下时,为了改善短沟道效应,沟道的掺杂浓度不断提高,为了调节阈值电压Vt,栅氧化层的厚度也不断减小到1nm。1nm厚度的SiON栅介质层已不再是理想的绝缘体,栅极与衬底之间将会出现明显的量子隧穿效应,衬底的电子以量子的形式穿过栅介质层进入栅,形成栅极漏电流Ig。为了改善栅极漏电的问题,半导体业界利用新型高K介电常数(High-k - HK)介质材料HfO2来代替传统SiON来改善栅极漏电流问题。SiON的介电常数是3.9,而HfO2的介电常数是25,在相同的EOT条件下,HfO2的物理厚度是SiON的6倍多,这将显著减小栅介质层的量子隧穿的效应,从而降低栅极漏电流及其引起的功耗。但是利用HK介质材料代替SiON也会引起很多问题,例如导致多晶硅栅耗尽效应形成高阻栅,HK介质材料与多晶硅的界面会形成界面失配现象降低载流子迁移率,HK介质材料还会造成费米能级的钉扎现象。目前半导体业界利用金属栅(Metal Gate - MG)取代多晶硅栅电极可以解决Vt漂移、多晶硅栅耗尽效应、过高的栅电阻和费米能级的钉扎等现象。利用HK介质材料代替SiON和利用金属栅取代多晶硅栅的技术称为HKMG工艺技术。如图1.16(a)所示,是采用HKMG技术的MOS管结构图。

图1.16采用HKMG技术的MOS管结构图和FD-SOI

1.9FD-SOI晶体管

当MOS器件的特征尺寸不断缩小22nm及以下时,仅仅提高沟道的掺杂浓度和降低源漏结深已不能很好的改善短沟道效应。加利福尼亚大学伯克利分校的胡正明教授基于SOI的超薄绝缘层上的平面硅技术提出UTB-SOI(Ultra Thin Body - UTB),也就是FD-SOI晶体管。研究发现要使FD-SOI有效抑制短沟道效应,并能正常工作,绝缘层上硅膜的厚度应限制在栅长的四分之一左右。对于25nm栅长的晶体管,FD-SOI的硅膜厚度应被控制在5nm左右。FD-SOI晶体管的沟道厚度很小,栅的垂直电场可以有效的控制器件的沟道,从而降低了器件关闭时的漏电流,抑制短沟道效应。如图1.16(b)所示,是FD-SOI晶体管的剖面图。

1.10Bulk FinFET和SOI FinFET晶体管

另外,1989年,Hitachi公司的工程师Hisamoto对传统的平面型晶体管的结构作出改变提出的基于体硅衬底,采用局部氧化绝缘隔离衬底技术制造出全耗尽的侧向沟道三维晶体管,称为DELTA(Depleted Lean-Channel Transistor)。胡正明教授依据Hisamoto的三维晶体管提出采用三维立体型结构的体FinFET和SOI FinFET代替平面结构的MOSFET作为集成电路的晶体管,由于三维立体晶体管结构很像鱼的鳍,所以称为鳍型场效应晶体管。如图1.17所示,是Bulk FinFET和SOI FinFET晶体管的剖面图。

FinFET晶体管凸起的沟道区域是一个被三面栅极包裹的鳍状半导体,沿源-漏方向的鳍与栅重合的区域的长度为沟道长度。栅极三面包裹沟道的结构增大了栅与沟道的面积,增强了栅对沟道的控制能力,从而降低了漏电流,抑制短沟道效应,同时也有效的增加了器件沟道的有效宽度,并且增加了器件的跨导。另外为了改善栅极漏电流,FinFET晶体管的栅介质也采用HK材料,栅极也采用金属栅。

图1.17 Bulk FinFET和SOI FinFET

-

电阻

+关注

关注

88文章

5737浏览量

178576 -

电极

+关注

关注

5文章

881浏览量

28292 -

MOS

+关注

关注

32文章

1624浏览量

99783

发布评论请先 登录

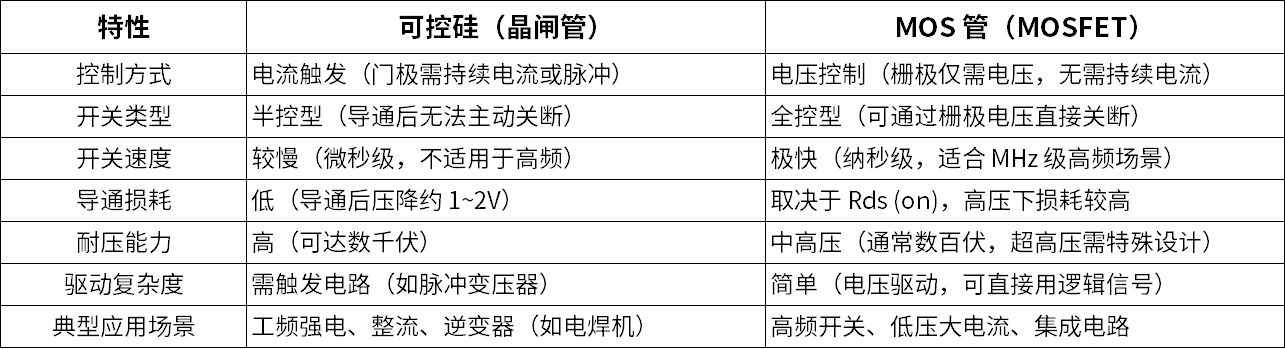

开关器件应用辨析:可控硅能否替代MOS管?

MOS管在电动牙刷中的应用分析

高效迷你化MOS管在快充头的核心应用

电子元器件失效分析与典型案例(全彩版)

工业电机行业现状及未来发展趋势分析

GaN、超级SI、SiC这三种MOS器件的用途区别

高速 MOS 驱动电路设计和应用指南

MOS高温挑战终结者?仁懋三款MOS器件引爆主机能效革命

2025年电子元器件市场展望:瑞沃微深度剖析机遇与挑战的前瞻预测

关于MOS器件的发展与挑战分析介绍

关于MOS器件的发展与挑战分析介绍

评论