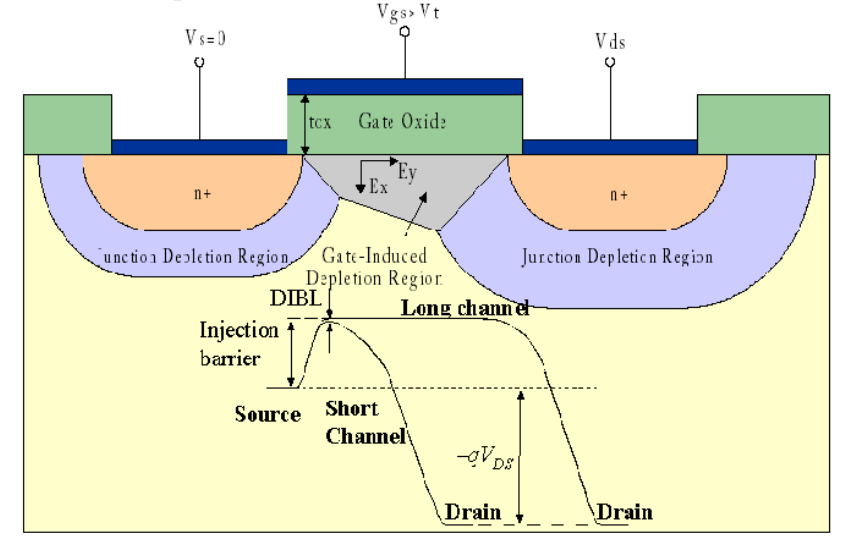

新思科技近日宣布MPW(多项目晶元)领先供应商MOSIS已选择新思科技IC Validator工具进行物理验证。IC Validator功能齐全的物理验证解决方案,辅助以高度可扩展的引擎,助力MOSIS 大大提高物理验证速度。MOSIS在FinFET工艺技术设计中为全芯片设计规则检查(DRC)和版图对照原理图(LVS)signoff部署了IC Validator。

“MOSIS 提供MPW设计,为用户加快生产速度并降低成本。我们需要一种高效的物理验证解决方案,以确保设计流片的准时交付。IC Validator使我们的工程师具备满足生产力和性能要求的各项功能,按时sign off。”

IC Validator是新思科技Fusion Design Platform™的关键组件。它是一个全面的物理验证工具套件并可高度扩展,包括DRC、LVS、可编程电气规则检查(PERC)、虚拟金属填充和可制造性设计(DFM)增强功能。IC Validator在架构时便秉持实现高性能和可扩展的宗旨,利用智能内存感知负载调度和平衡技术,让主流硬件得到最大程度的利用。它可在多台机器上同时使用多线程和分布式处理方法,利用可扩展性优势,扩展到1000余个CPU。

“在先进的工艺技术中,由于制造复杂性的增强,按既定进度完成物理验证成为新的挑战。IC Validator满足所有主要晶圆代工厂所提供的高性能、可扩展性和现成经优化的运行指令集(runset),为设计人员实现了生产芯片的最快途径。”

-

新思科技

+关注

关注

5文章

926浏览量

52645 -

MOSIS

+关注

关注

0文章

2浏览量

2364

原文标题:MOSIS基于新思科技IC Validator进行FinFET芯片物理验证

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

matlab的算法部署在simulink中

【产品介绍】L-Edit IC和L-Edit Advanced:模拟/混合信号 (AMS) 版图

生成Bitstream的DRC LUTLP-1错误的解决办法

华大九天Argus DRC技术详解

霍尔IC在电动晾衣架中的应用与原理分析

霍尔IC在无刷电机中的应用与原理

行芯科技揭示先进工艺3DIC Signoff破局之道

PPS注塑IC元件封装中的应用优势与工艺

Microchip通过设计内signoff DRC在成熟节点定制IC设计中实现显著的生产率提升

是否可以使用OpenVINO™部署管理器在部署机器上运行Python应用程序?

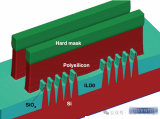

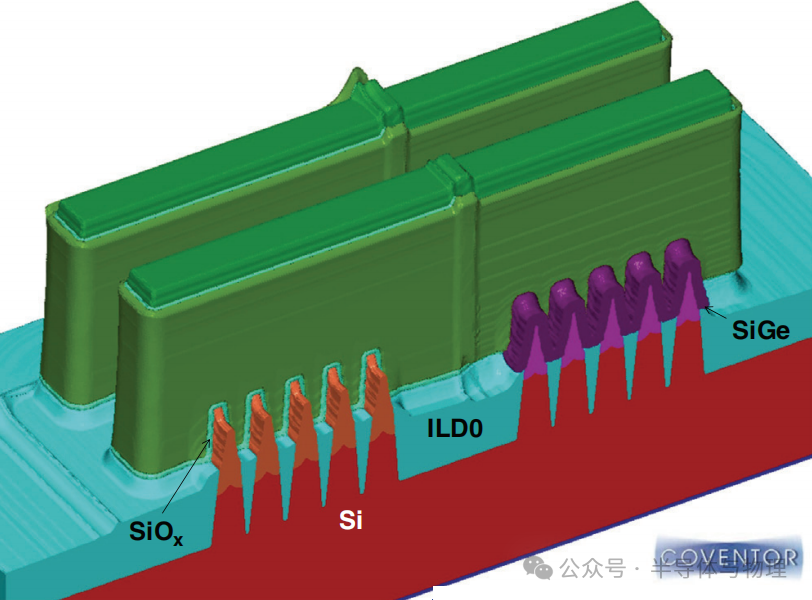

FinFet Process Flow-源漏极是怎样形成的

MOSIS在领先的FinFET工艺设计中为DRC和LVS signoff部署IC Validator

MOSIS在领先的FinFET工艺设计中为DRC和LVS signoff部署IC Validator

评论