在DRC的修复过程中,我们可以先分析并修复PR工具里面的DRC,等DRC的数目比较少了之后,我们就可以把PV工具里面signoff DRC的结果load到PR工具里面去分析并做自动或者手工的修复。

对于比较顽固的DRC(工具做了多轮修复都修不掉的Case),可以手工分析并修复,对于修复的方法,有以下两点建议:

1. 打破DRC检查的条件

2. 根据DRC的要求去修复

1.打破DRC检查的条件

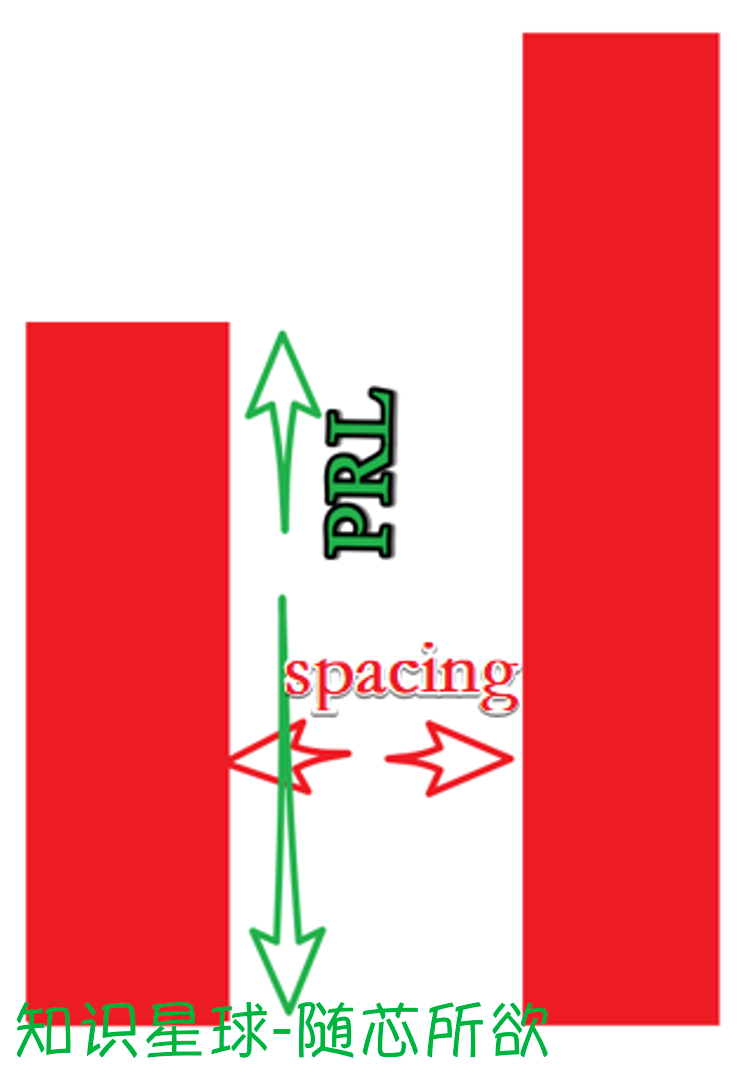

可以打破DRC check的条件,比如length或者PRL(parallel run length)或者width,条件不成立的话自然就没有DRC了。 举个例子,比如下面的两个Shape,工具检查报出来两个shape之间的距离太小了,要想满足DRC,Spacing必须是现在的3倍,那么只能强制拉开这两个Shape么?对于底层的DRC,拉开的话手工修复是比较麻烦的,还需要做很多连线尤其是DPT的工艺,还需要注意Color。其实还有一些其他简单的解法,就是破坏这个检查成立的条件,比如这种Case一般都会要求在PRL(Parallel run length)大于某个值的情况下Spacing要求是某个值。那么其实只要稍微缩短一下左边的那段Shape,使其小于PRL的条件,那么这种DRC自然也就解掉了。根本不用大张旗鼓的去拉开两个Shape。

再比如,下面的Case,在一个宽线(PG)和细线(signal)之间有Spacing违反,signal wire是两倍宽度的线,且周边的线都非常密集,想拉大距离是比较困难的,那么如何修这个问题呢?

实际上它们之间的最小Spacing和两个net的宽度以及RPL都有关系,上面的Case如果缩短PRL不容易的话其实可以从...

编辑:黄飞

-

DRC

+关注

关注

2文章

157浏览量

38368 -

DPT

+关注

关注

0文章

14浏览量

7024

原文标题:DRC的分析与手工修复经验分享

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DRC分析和修复经验分享

DRC分析和修复经验分享

评论