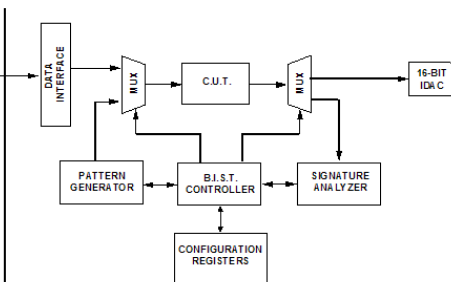

利用FPGA可重复编程的特性,通过脱机配置,建立BIST逻辑,即使由于线路被操作系统的重新配置而令BIST结构消失,可测性也可实现。本文给出一种基于BIST利用ORCA(Optimized

2018-11-28 09:02:00 4021

4021

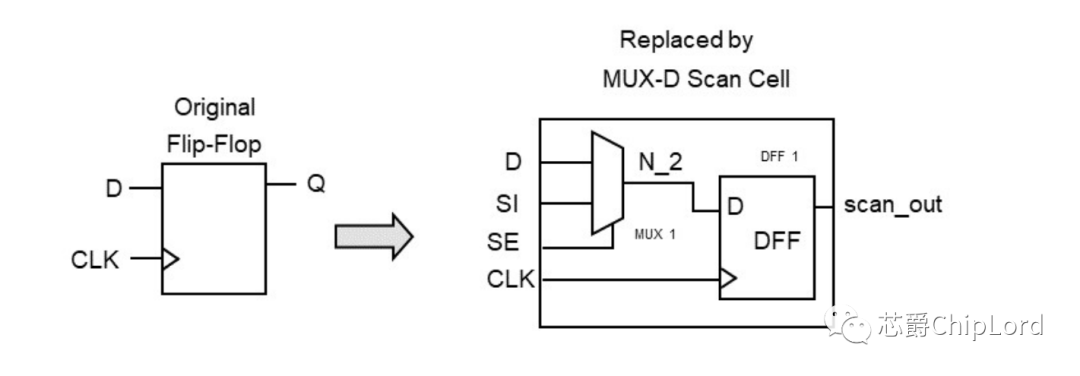

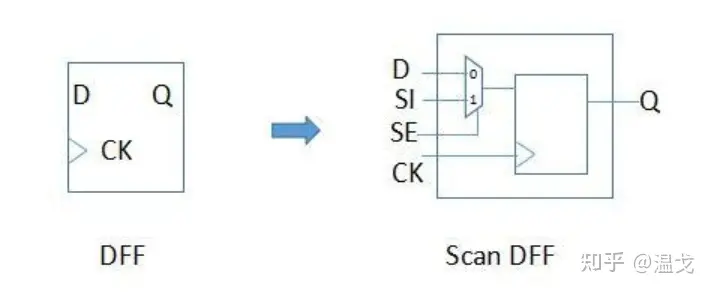

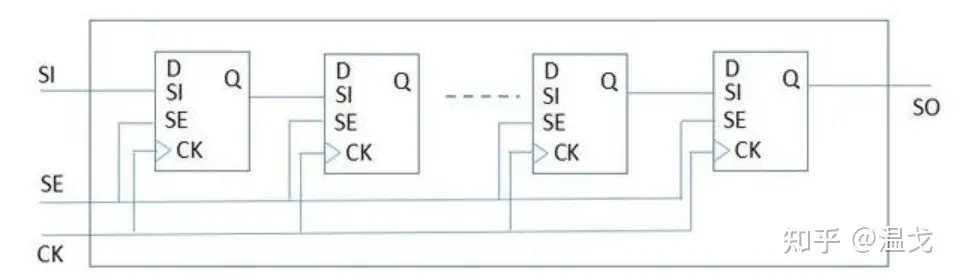

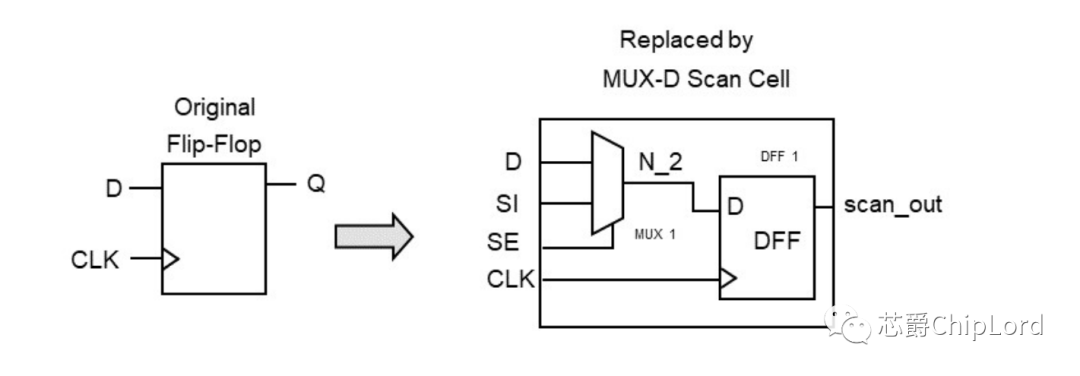

如下图所示:左边是普通寄存器,右边是可扫描寄存器,D端前面加一个二选一的MUX,选择端是scan_enable,为1时选择SI端,为0时选择D端。

2023-09-15 10:10:37 1762

1762

。为什么还会有2.4GHz的本振信号呢?是我理解错了,还是我测试错了?我测试的频谱图如附件所示。一张是使能BIST的,一张是不使能BIST的。附件Screen_0061.png83.6 KBScreen_0062.png82.9 KB

2018-08-01 09:10:10

BOARD EVALUATION SCAN90004

2023-03-30 11:45:02

SCAN921025 - 30-80 MHz 10 Bit Bus LVDS Serializer and Deserializer with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921025H - High Temperature 20-80 MHz 10 Bit Bus LVDS SerDes with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921226 - 30-80 MHz 10 Bit Bus LVDS Serializer and Deserializer with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921226HSM - High Temperature 20-80 MHz 10 Bit Bus LVDS SerDes with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921260 X6 1:10 Deserializer with IEEE 1149.1 (JTAG) and at-speed BIST datasheet (Rev. F)

2022-11-04 17:22:44

SCAN921821 Dual 18-Bit Serializer w/Pre-emph, IEEE 1149.1 JTAG & At-Speed BIST datasheet (Rev. C)

2022-11-04 17:22:44

SCAN926260 - Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN926260 Six 1-10 Bus LVDS Deserializers w/IEEE 1149.1 & At-Speed BIST datasheet (Rev. H)

2022-11-04 17:22:44

SCAN926260TUF - Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN926260TUFX - Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN928028 8 Channel 10:1 Serializer with IEEE 1149.1 and At-Speed BIST datasheet (Rev. F)

2022-11-04 17:22:44

AD9361 BIST功能验证相关事项想请问各位大拿,AD9361 BIST功能验证是用于验证收发通道的链路部分,而数据接口部分是不是验证不到?当前调试过程中出现的问题是:配置模式FDD 1R1T

2021-09-14 22:29:00

ad9361初始化完成后使用bist模式测试ad9361的收发链路功能是否正确。配置寄存器0x3F4的值为0x5B时即连接到RX Dataport端口时,使用vivado下的ILA抓取输入端rx波形

2019-11-17 23:03:17

模块。测试中,使能ENSM进入FDD状态,切换BIST灌入Tx Chain (etc. SPIWrite 03F453),FPGA内部抓取接收信号,可以看到IQ正弦波,但是质量很差,类似噪声。后面我调节

2019-01-08 11:09:07

M0 在使用时有两个scan IO 接口,分别为.SE.RSTBYPASS这两个IO在芯片scan mode下需要做特别处理吗?我们能否把它当成普通的数字IP直接进行top级的scan 呢?谢谢!如果进行top级的scan,能否把这里的SE置0, RSTBYPASS也置0?

2022-08-22 15:20:07

虽然可测性设计(DFT)与内置自检(BIST)技术已在SoC(系统级芯片)设计中受到广泛关注,但仍然只是被看作“后端”的事。实际上,这些技术在器件整个设计周期中都非常重要,可以保证产品测试错误覆盖率

2011-12-15 09:53:14

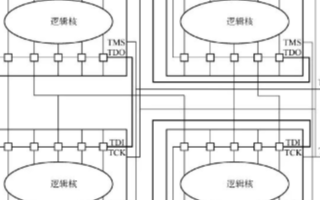

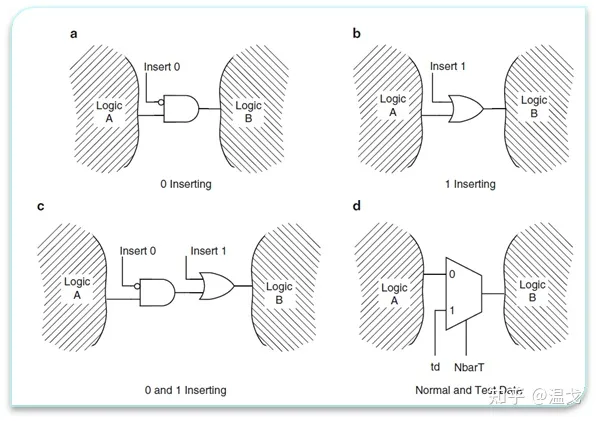

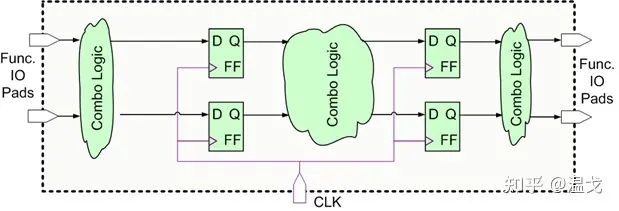

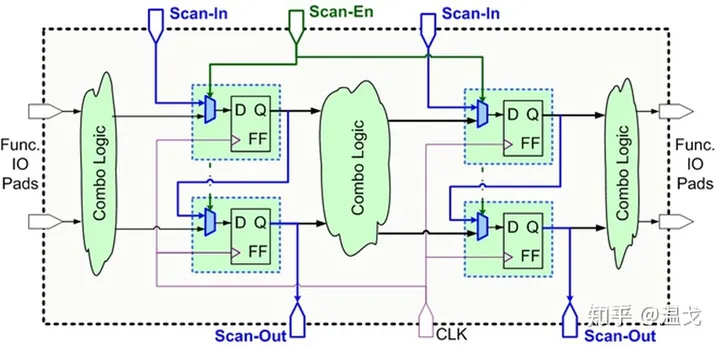

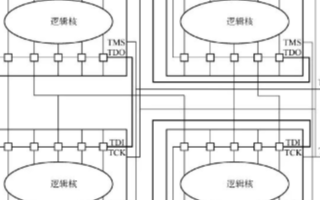

边界扫描测试 为了对电路板级的逻辑和连接进行测试,工业界和学术界提出了一种边界扫描的设计,边界扫描主要是指对芯片管脚与核心逻辑之间的连接进行扫描。扫描路径设计(Scan Design) 扫描路径

2011-12-15 09:35:34

嗨,我试图在ISE / SDK 14.6下编译BIST的13.4版本,但是我遇到了一些与丢失文件和目录有关的错误。我想知道其他人是否已经移植了BIST源代码。至少我想知道你将如何继续这项任务。所以,如果你有任何想法,我想听听他们。问候,KT

2020-03-17 10:22:01

你好,我没有意识到有一种方法可以运行工厂加载到QSIP中的测试。一位同事在上面加载了一个XmWorks文件,现在我无法使用以前的BIST。有没有办法重置为默认值或您是否会发送新的下载?谢谢,克里斯

2019-09-12 10:46:39

我们现在正在评估 S32K BIST 功能,当 sw 调用 apiBist_Run() 以启动 bist 时,但 mcu 重置。它发生在 Bist

2023-04-14 07:09:06

/ src / subdir.mk似乎是原因。在“C_SRCS + =”部分中:“../src/pcap.c \ / C:/zc706_bist/zc706_bist

2020-04-08 09:52:55

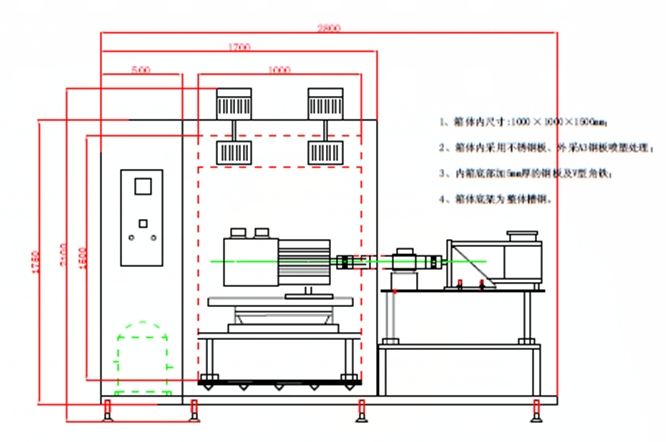

封装功能测试,覆盖1-1200管脚的各种封装形式BGA、QFP、PGA、PLCC、TSSOP、DIP等。 IC功能测试服务:利用BOUNDARY SCAN(边界扫描)测试设备提供各种常用芯片的直流功能

2009-07-21 11:40:36

s32g274a的板子支持BIST吗?如果板子支持,如何在 s32g274a 上使用在线 BIST?

2023-04-20 07:15:26

嗨,我正在使用带有DTM固件的BlueNRG-2芯片。它通过SPI连接到主处理器STM32。该蓝牙设备在外围设备中起作用(某些传感器)。 广告工作正常:作为主设备的另一个设备接收ADV_IND

2018-09-26 17:50:33

你好任何人都可以解释为什么四种 DDR 验证 BIST 测试类型无法执行并且颜色编码指示“…………测试脚本中的错误”?我能够成功执行 DDR 验证阶段和其他四种 DDR 验证测试类型(DMA 测试

2023-04-06 08:54:58

问题如题:在SimpleBLEObserver和 SimpleBLECentral的范例工程中,都没有找到设置LE_Scan_Window和LE_Scan_Interval这两个参数的语句,是有缺

2020-03-17 09:11:19

在BIST测试中,其他测试通过了闪存测试,失败的信息是 - 初始化时失败 - 闪存测试失败(1)可以任何人告诉我为什么,谢谢!

2020-05-05 08:42:01

你好我正在尝试在SP605评估板上运行BIST。我没有改变紧凑型闪存内容。我按照“Xilinx Spartan-6 FPGA SP605评估套件UG525入门指南”中的说明进行了跳线设置。但是当我按

2019-07-22 13:25:24

几个月的研究,我们没有设法取悦他,他告诉我们只是对故障覆盖做一些测试。这是我们需要采用BIST设计并在VHDL(我们认为)中实现并测试它的文档。这是文件。欢迎任何想法或帮助/解决!BIST.doc 1848 KB

2020-04-23 09:55:03

大家好,我只是想运行Digilent Xilinx Spartan-6(Atlys_Demo_BIST)附带的初始测试程序。所以我连接电源和HDMI插头(HDMI当然)并启动电路板,没有任何反应

2019-07-24 14:24:18

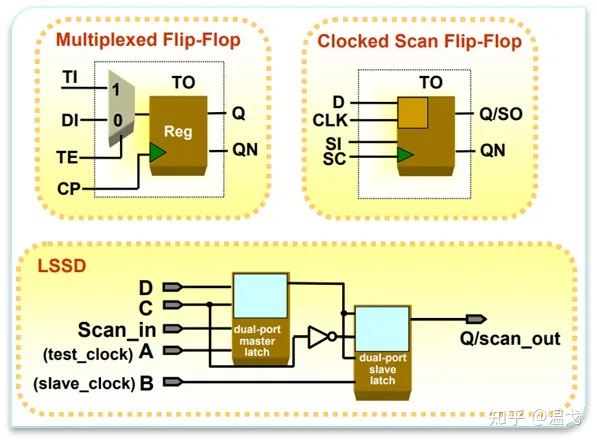

前面一期的公众号文章“让你彻底理解DFT”帮助大家理解了DFT所解决的问题。一句话来概括之就是:借助特定的辅助性设计,产生高效率的结构性测试向量以检测生产制造过程中引入芯片中的各种物理缺陷。Scan

2016-06-14 14:20:20

设计,例如压缩/解压、无线模块、网络模块等。而一块SoC芯片的功能可能是多个独立模块的总和。另外,芯片的制造需要经历化学、冶金、光学等工艺过程,在这些过程中可能引入物理缺陷导致其不能正常工作。因此对芯片的测试

2019-09-20 07:09:28

怎么实现基于LFSR优化的BIST低功耗设计?

2021-05-13 06:21:01

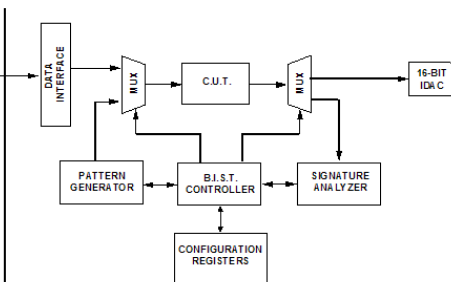

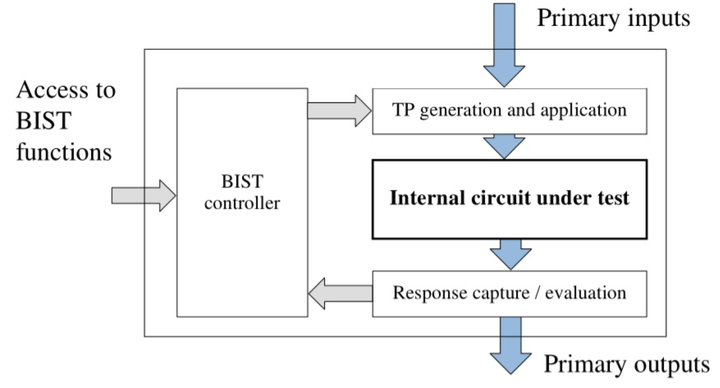

引言大多数IC设计工程师都了解数字BIST的工作原理。它用一个LFSR(线性反馈移位寄存器)生成伪随机的位模式,并通过临时配置成串行移位寄存器的触发器,将这个位模式加到待测电路上。数字BIST亦用

2019-07-19 06:18:30

你好,我无法在我的Ubuntu 14.04 [.2] 64位桌面上运行BIST程序(如xtp242中所指定)。以下是我所做的一些事情: - 从Xilinx购买了Xilinx Zynq-7000

2019-10-08 10:58:00

通过FPGA进行并口的时序控制,寄存器已经成功读写,官方文档上BIST相关寄存器 BIST Control设置使能,并将计时器赋值,输入和通道寄存器也设置,直接读取BIST I/Q Path

2018-08-18 07:04:30

请教一下各位,刚刚开始搞ad9361,ad9361 bist测试rx port只需要配置0x3f4寄存器就可以吗?还需要配置其他寄存器吗?如何配置?0x3f4配置为0x5b,如何测试rx port是否正常?现在通过示波器抓rx port data上没有任何波形。

2018-08-16 06:58:45

您好,我正在使用 S32K344 评估 S32K BIST 功能。调用Bist_Run(BIST_SAFETYBOOT_CFG)时遇到hard fault,如图。它发生

2023-04-20 06:44:58

The SCAN921260 integrates six deserializer devices into asingle chip. The SCAN921260 can

2009-10-13 10:01:52 24

24 The SCAN921821 is a dual channel 18-bit serializer featuringsignal conditioning, boundary SCAN

2009-10-13 10:03:30 10

10 The SCAN926260 integrates six 10-bit deserializer devicesinto a single chip. The SCAN926260 can

2009-10-13 10:05:04 8

8 The SCAN928028 integrates eight serializer devices into asingle chip. The SCAN928028 can

2009-10-13 10:07:10 19

19 The SCAN25100 is a 2457.6, 1228.8, and 614.4 Mbps serializer/deseralizer (SerDes) for high-speed

2009-10-14 08:40:07 17

17 The SCAN12100 is a 1228.8 and 614.4 Mbps serializer/deseralizer(SerDes) for high-speed

2009-10-14 08:44:37 17

17 摘要:针对某SOC中嵌入的8KSRAM模块,讨论了基于MarchC-算法的BIST电路的设计。根据SRAM的故障模型和测试算法的故障覆盖率,研究了测试算法的选择、数据背景的产生,并完成了基于Ma

2010-04-26 15:18:30 29

29 介绍了用于IP核测试的内建自测试方法(BIST)和面向测试的IP核设计方法,指出基于IP核的系统芯片(SOC) 的测试、验证以及相关性测试具有较大难度,传统的测试和验证方法均难以满足

2010-12-13 17:09:11 10

10 在BIST(内建自测试)过程中,线性反馈移位寄存器作为测试矢量生成器,为保障故障覆盖率,会产生很长的测试矢量,从而消耗了大量功耗。在分析BIST结构和功耗模型的基础上,针

2010-12-23 15:35:11 0

0 黑盒测试与白盒测试区别

黑盒测试 黑盒测试也称功能测试或数据驱动测试,它是在已知产品所应具有的功能,通

2008-10-22 12:40:02 8981

8981 基于BIST的编译码器IP核测

随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合

2008-12-27 09:25:39 794

794

低功耗的BIST伪随

2011-01-10 10:47:06 34

34 通常我们在设计芯片的同时,可以根据芯片本身的特征,额外地把可测性电路设计(Design For Testability)在芯片里。谈到可测性的电路设计,内建自测试(BIST)和基于扫描Scan—Based)的电路设计

2011-06-10 10:13:45 2119

2119

数字BIST的工作原理:用一个LFSR(线性反馈移位寄存器)生成伪随机的位模式,并通过临时配置成串行移位寄存器的触发器,将这个位模式加到待测电路上。

2011-11-23 15:24:27 2428

2428

衡量电机发热程度是用“温升”而不是用“温度”。电机测试中涉及到温度的测试主要时温升测试及环境温度测试,两者是既有区别又有联系的关系。

2016-06-03 09:23:35 3768

3768

基于功能复用的抗老化BIST设计_梁华国

2017-01-07 16:00:43 0

0 低成本BIST映射电路的设计与优化_张玲

2017-01-07 21:39:44 2

2

3 使用Testcompress 实现EDT压缩scan chain

4 使用Testcompress 产生测试DC/ACpattern,同时产生测试验证的Testbench

2017-10-26 16:01:36 34653

34653

随着FPGA在现代电子系统中应用的不断增多.FPGA的测试技术也得到非常快的发展。其中,内建白测试(BIST)的方法已经成为一种主流的解决方案。BIST方法一般来说可以分为两大类,一类是离线BIST

2017-11-08 14:21:46 1

1 本文开始介绍了什么是耐压测试和介绍进行耐压测试的原因以及直流与交流耐压测试的比较,其次介绍了绝缘测试的特性,最后介绍了绝缘和耐压的区别以及区分了耐压测试与绝缘测试的区别。

2018-04-03 09:30:10 103243

103243 电子发烧友网为你提供TI(ti)SCAN921821相关产品参数、数据手册,更有SCAN921821的引脚图、接线图、封装手册、中文资料、英文资料,SCAN921821真值表,SCAN921821管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)SCAN921260相关产品参数、数据手册,更有SCAN921260的引脚图、接线图、封装手册、中文资料、英文资料,SCAN921260真值表,SCAN921260管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)SCAN921025H相关产品参数、数据手册,更有SCAN921025H的引脚图、接线图、封装手册、中文资料、英文资料,SCAN921025H真值表,SCAN921025H管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)SCAN926260相关产品参数、数据手册,更有SCAN926260的引脚图、接线图、封装手册、中文资料、英文资料,SCAN926260真值表,SCAN926260管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)SCAN928028相关产品参数、数据手册,更有SCAN928028的引脚图、接线图、封装手册、中文资料、英文资料,SCAN928028真值表,SCAN928028管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)SCAN921226H相关产品参数、数据手册,更有SCAN921226H的引脚图、接线图、封装手册、中文资料、英文资料,SCAN921226H真值表,SCAN921226H管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

电子发烧友网为你提供TI(ti)SCAN921224相关产品参数、数据手册,更有SCAN921224的引脚图、接线图、封装手册、中文资料、英文资料,SCAN921224真值表,SCAN921224管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:16:58

内置自测(BIST),曾经保留用于复杂的数字芯片,现在可以在许多具有相对少量数字内容的设备中找到。

2019-04-12 14:14:28 2466

2466

到巨大的数字系统级芯片设计中。虽然片上内置自测(BIST)与环回操作相结合是昂贵的自动测试设备(ATE)的广泛采用的替代方案,但其高速模拟部分的故障覆盖率较差,严重影响整体产品现在,一种称为无矢量测试的方法正在出现,它提供了两种方法中的最佳方法:片上I/O BIST的成本效益与基于ATE的信号完

2023-11-10 16:57:23 270

270 边界扫描测试(Boundary scan)是为了解决印制电路板(PCB)上芯片与芯片之间的互连测试而提出的一种解决方案。它与内部扫描有明显的区别,前者是在电路的输入/输出端口增加扫描单元,并将这些

2020-04-13 17:31:16 10213

10213

α测试和β测试的区别

2020-06-29 11:22:49 25177

25177 静态测试,动态测试的区别:程序是否运行。

2020-08-19 17:13:58 8475

8475 文主要探讨了用全扫描结构(FULL SCAN METHOD)来实现数字电路可测性设计(DESIGN FOR TEST)的原理与方法。其中涉及到扫描结构(SCAN)的算法依据、电路的基本结构、测试矢量

2021-03-26 14:48:18 22

22 arp-scan.zip

2022-05-05 09:51:25 5

5 LBIST (Logic build-in-self test), 逻辑内建自测试。和MBIST同理,在关键逻辑上加上自测试电路,看看逻辑cell有没有工作正常。BIST总归会在芯片里加入自测试逻辑,都是成本。

2022-08-29 15:33:30 2169

2169 的BIST签名检查敏感,后者可以检测单个比特错误。同样的数字接口检查可以在生产测试车间执行,也可以在现场的系统级自检中执行。

2023-02-01 15:36:14 997

997 接着上文,MCU芯片设计了mbist、scan chain之后,功能仿真失败?

2023-02-20 09:35:15 955

955 [摘要] T-Scan系统能精确记录咬合接触的时间、 力量、 面积和动态分析咬合接触情况, 自问世以来通过产品的

不断更新与发展, 使其更好地运用于口腔临床和科研工作中。 本文就 T-Scan 系统的特点和临床应用作一综述。

[关键词] T-Scan 系统; 咬合接触; 咬合分析; 临床应用

2022-04-01 15:59:51 1925

1925

AI芯片和SoC芯片都是常见的芯片类型,但它们之间有些区别。本文将介绍AI芯片和SoC芯片的区别。

2023-08-07 17:38:19 2103

2103 模拟到数字的信号不可控,需要和数字registered outputs mux一下提高test coverage。关键词是registered output! 这个技巧俗称scan loopback。

2023-12-08 11:24:40 533

533

FPGA芯片和普通芯片在多个方面存在显著的区别。

2024-03-14 17:27:34 223

223

电子发烧友App

电子发烧友App

评论