在整个PCBA生产制造过程中, PCB 设计是至关重要的一部分,今天主要是关于 PCB 杂散电容、影响PCB 杂散电容的因素,PCB 杂散电容计算,PCB杂散电容怎么消除。

一、什么是杂散电容?

从这个名字本身我们就可以知道,杂散的意思就是:“无章程,漫无目的,不在该在的地方。”

因为我们可以说杂散电容是电路各部分之间存在的不可避免的、无意的和不需要的电容。

杂散电容电容图

电容不仅仅存在于电容内部,事实上,任何两个处于不同电位的表面,并且足够靠近以产生电场,都具有电容,就像真正的电容一样。

这种影响通常存在于电路中,例如:在导电线路和元件引线之间,这种意外的电容被称为杂散电容。

杂散电容可能导致电路内正常电流流动的中断。

二、PCB 杂散电容大小计算

在普通的计算中,杂散电容大小公式:C = Q/V,是对在差分电位上积累的电荷的测量。

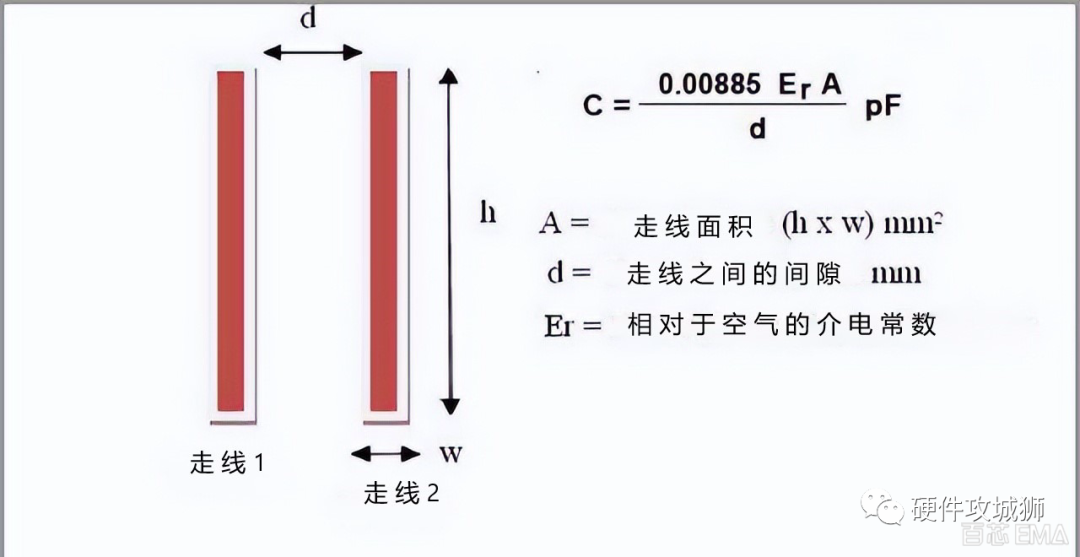

在PCB 设计中,杂散电容大小公式变为 :C= ϵA/D,这意味着电容值与绝缘体的介电常数、面积、导体之间的距离之间的关系。

杂散电容计算公式

三、影响 PCB 杂散电容数量的因素

电容构造中,有三个因素决定了产生的杂散电容的数量,这些因素都会通过影响特定量的电场力(任何两个板之间的电压)产生的电场通量的量来影响杂散电容。

1、板间距

保持所有其他因素不变,板之间的间距越大,杂散电容就越小。

另一方面,更小的板间距会产生更多的杂散电容。

更紧密的板间距会导致更高的场力,并且对于施加到两个板的任何特定电压,这会导致相对较高的场通量(电荷在两个尺度上累积)。

PCB 图

2、板块面积

所有其他变量都是常数,更大的板面积提供更多的杂散电容,而较小的板面积产生更少的杂散电容。

3、介电材料

保持所有其他变量不变,介电材料的较高介电常数会产生较大的杂散电容,而介电材料的较低介电常数会产生较小的杂散电容。

相对介电常数表示材料的介电常数,它接近真空(纯)。

例如,相对介电常数为 7 的玻璃的标准介电常数是真空的 7 倍。因此,当所有其他变量都相等时,它将导致产生比纯真空强 7 倍的电场通量。

四、PCB 设计如何降低杂散电容?

在很多应用中,多条信号之间的杂散电容可能会耗尽或者影响整个设计。

在较低频率下,杂散电容往往可以忽略不计,在高频下,杂散电容可能是电路中主要的问题,我们可以在布局的时候尽量降低杂散电容。

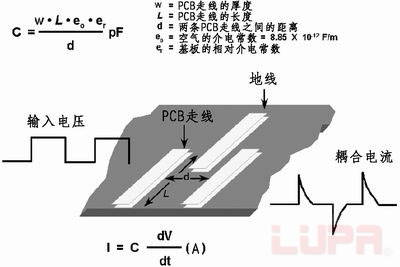

杂散电容通常是信号线与另一条信号线或者基板与信号线之间产生的电耦合而产生的。

以下是减少杂散电容的一些方法:

1、控制好电子元件的引线,保持比较短

保持电子元件的引线非常短,并且以消除电容耦合的方式对元件进行分组,可以减少杂散电容的生成。

这里举一个简单的例子:一般从制造商买来的新的电感,电感的引脚都会非常常,如下图所示,引线可以在电感上衍生几英寸。但是,将具有这么长引线的电感插 入电路中可能会在电路中产生一些问题。

当你的电感具有非常常的引线靠近彼此时,这些引线本质上是电线,当电路中电线彼此靠近时,就会产生电容效应,即使是少量的电线也可能产生具有相当大的电容。

杂散电容可以用来阻止或者阻止低频信号,这是因为电容或者充当电容的设备对低频信号具有高阻抗,因此,低频信号很难通过具有电容特性的电路,当你在电路中添加不需要的电容时,电路可以阻止低频信号通过,如果是无线电路或者音频电路,则可能会阻塞整个电路频率范围。

因此,电感引线必须保持较短(理想长度小于 1.5mm),以有效阻止杂散电容,产生电容效应,电容效应会限制电感通过低频信号的能力。

表面贴纸电感可能更适用于电路,因为无铅端子直接放置在电路的电源平面上,几乎可以阻止所有电容。因为表面贴装元件没有引线,这可以限制电感,并且允许电感在电路中更好地传递低频信号。

2、增加元器件或者组件之间的间距

增加元器件,组件,走线或者电缆等各个网络的之间的间距非常重要,这样可以减少杂散电容的产生。

因为杂散电容距离成反比,距离大,杂散电容就小,距离小,杂散电容就大。

3、添加屏蔽导体

也就是说在要求低的各种网络之间放置另一个参考信号,也就是屏蔽导体。例如:在相邻走线之间添加一条接地铜带。

铜带起到屏蔽作用,可以防止电荷积聚,从而减少杂散电容的产生。

4、减少走线宽度

当导体的横截面积增加时,杂散电容会增加,因此减少走线宽度,尤其是对于传导高频信号的走线。

5、去除内层地平面

大的内层接地层可能非常适合热管理和 EMI控制,但是对于杂散电容来说并没有什么好处。

如果要减轻杂散电容,建议去除内层地平面。

6、避免金属过度平行布线

以上就是关于PCB 杂散电容以及减少 PCB 杂散电容技巧简单的介绍,希望能够对大家有用,欢迎大家多多指教。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论