缩小成电脑中各种不同频率控制总线。如果电脑32.768K晶振故障。一般会有如下问题产生。1.电脑不开机 2.电脑reset复位灯常亮 3.系统时间不准 4.开机进入系统慢5.用主板测试卡测试的时候一直乱码

2013-03-28 15:54:00

6748的PLL0中寄存器PLLCTL[CLKMODE]中,是不是有源晶振和无源晶振的区别?怎么选择,如果选错了会有什么影响?

2020-05-22 10:05:18

我发现PCB板上有很多32.768的插件晶振,PCB板上不是插件封装而是贴片封装,直接将插件晶振焊到PCB表面,为什么要这样设计?也有选择插到板子上的,但有很多板子是选择贴片封装,这样有什么好处?哪位大神解答一下,不胜感激

2016-07-23 10:40:05

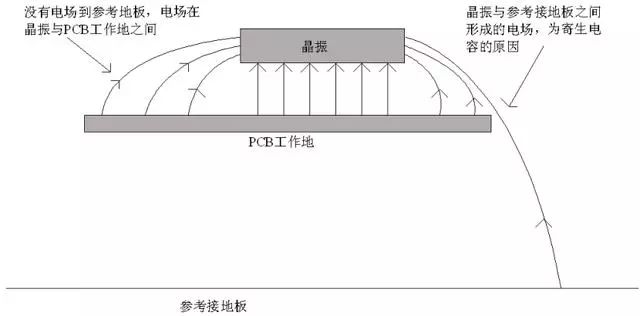

时电场分布如下:PCB 边缘的晶振与参考接地板之间的电场分布示意图PCB 中间的晶振与参考接地板之间的电场分布示意图从图中可以看出,当晶振布置在 PCB 中间,或离 PCB 边缘较远时,由于 PCB

2020-04-21 07:00:00

PCB PDN design guidelines (PCB电源完整性设计指导) ------组件选择和放置准则1.所有连接器应位于板的一个边缘或一个角。在大多数设计中,连接电缆的连接器可以构成

2021-12-28 06:08:02

的边缘具有不同的阻抗特性,并且存在较高的电磁干扰(EMI)机会。最重要的是,连接 PCB 的连接器会辐射 EMI。鉴于这些因素,将敏感的高速器件放置在靠近板中心的位置以减少 EMI 的影响将是一个很好

2023-04-11 17:22:23

在PCB布线时,为什么和芯片连接的晶振要和芯片挨一起呢?

2023-04-10 16:32:17

晶振选择和电路板设计 晶振的选择和PCB板布局会对VCXO CLK发生器的性能参数产生一定的影响。选择晶体时,除了频率、封装、精度和工作温度范围,在VCXO应用中还应注意等效串联电阻和负载电容

2018-09-13 16:09:28

晶振设计指导手册,ENHANCED GUIDELINES TO IMPLEMENT 19.2 MHZ CRYSTAL FOR SMALL PCB-HIGH THERMAL LAYOUTS。通过晶振 PCB 设计初步了解 高频信号的设计基础。

2023-09-20 06:37:54

margin < 5, 你别无选择, 再重新挑选另外一个晶振吧。然后重新回到第一步。7. 关于PCB 的提示1. 外部杂散电容和电感要控制在一个尽可能小的范围内, 从而避免晶振进入非正常工作模式或

2022-04-14 14:32:45

` 晶振是石英晶体振荡器的简称,用于产生时钟频率。晶振的档次由其精度决定。在声卡设计当中,不管是娱乐用、还是音乐欣赏用、还是纯数字输出声卡上,都能找到晶振的使用。 其实晶振是无源晶振和有源晶振的合称

2016-07-16 14:59:37

等协议,将模块从一端发送到另一端,或者是通过手机控制。一般来说,智能硬件产品都需要进行数据传输,少不了无线传输模块,而晶振,在无线模块里面是非常核心的元件。将晶振放置在模块里,应用在实际产品中,这些

2017-07-07 11:43:22

电脑主板一般都会有2-3个石英晶振,主板上面的晶振到底是起到啥作用?简略的说电脑主板的晶振是用来控制时间等运用的,计算机都有个计时电路,把它们称为计时器。晶振和时钟芯片共同组成主板的时钟发生器,主板

2017-07-13 15:02:58

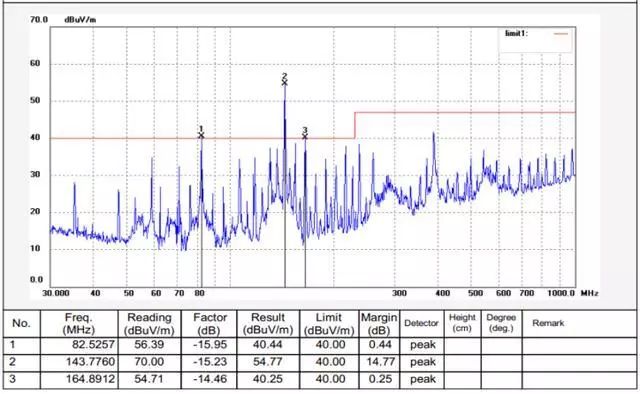

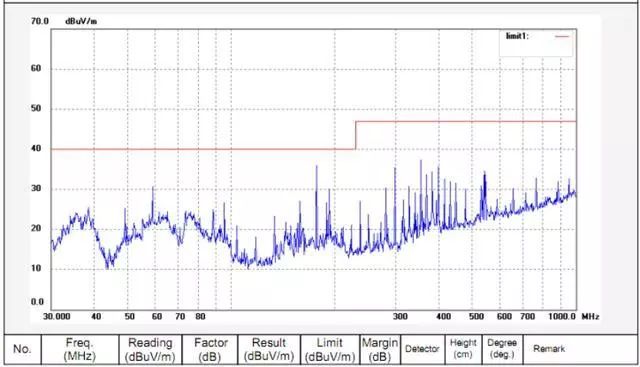

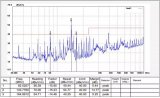

某行车记录仪,测试的时候要加一个外接适配器,在机器上电运行测试时发现超标,具体频点是84MHZ、144MH、168MHZ,需要分析其辐射超标产生的原因,并给出相应的对策。

2020-10-22 10:22:45

,你很容易鉴别是否为良品。(3) 排除晶振为停振品的可能性,因为你不会只试了一二个晶振。(4) 试着改换晶体两端的电容,也许晶振就能起振了,电容的大小请参考晶振的使用说明。(5) 在PCB布线时晶振电路

2012-06-10 19:56:26

陶瓷封装制品,如果电路上EMC较大,则尽量选用金属封装制品。另外晶振下面不要走信号线,避免带来干扰。10、其他问题导致晶振不起振晶振设计、过程中的建议1、在PCB布线时,晶振电路的走线尽可能的短直,并尽可能

2019-07-16 04:20:09

什么是晶振晶振与单片机周期单片机晶振的作用指令周期晶振与晶体的区别

2021-03-04 07:00:10

问题;(2)杜绝高dU/dt的印制线或器件放置在PCB的边缘,如果设计中由于其他原因一定要布置在PCB边缘,那么可以在晶振印制线边上再布一根工作地(GND)线,并注意一定要在包地线上间隔一段距离就打过孔,把

2020-12-25 15:02:07

的影响是晶振需要攻克的难题之一。对于老化问题,首先必须从晶体制作角度着手,为推迟晶体老化时间,封装时应检查好气密性;其次用户在选择晶振时要把老化部分考虑进去,这样就可以减少晶体对电路的影响。 电子产品轻薄

2017-06-29 14:26:49

晶振,电子元器件产品的一种,晶振体积超小型薄型,高性能,低耗电,是电子产品的最佳搭档。 通常电子工程师在设计PCB的时候,一般先是按照自己的想法来设计,到PCB板成型只差晶振时,才会叫采购

2013-11-14 15:49:03

振。所以成本也会高。按照市场价格测算,现在普通有源晶振大致参考价格在2元多左右,无源晶振2毛-8毛左右,压控晶振和温补晶振价格会比普通晶振高一些。影响晶振多少钱的因素-标准频率标准频率是指各行业通过

2017-06-08 15:21:07

电子产品中是有一点辐射的危害的,但是危害也及其较小。因为当晶振在工作的过程中会释放频率,输出信号。多多少少会有一点的影响。但是现在大部分晶体都是使用环保的材料。对人体危害是极小的。泰河工厂所有压电元器件均

2013-11-01 16:07:02

产生的交流信号频率容易变化),所以最常见的就是用晶振来解决,可以说只要有数字电路的地方就可以见到晶振。在振荡器中采用一个特殊的元件——石英晶体,可以产生高度稳定的信号,这种采用石英晶体的振荡器称为晶体振荡器。二、符号三、分类晶振的分类: 晶体振荡器也分为 无源晶振 和 有源晶振 两种类型。无源晶振

2022-02-14 06:11:34

请问:由于担心晶振数据不准确,想测试下晶振,请问用什么方法合适呢??晶振已经焊在电路板上了,估计8Mhz左右的,求用示波器的详细测量方法,谢谢!

2013-12-25 09:17:08

与CO为2pf,CPCB=4pF可以得出CL1为6.8pf.左右注意:CPCB,CS 在不同的芯片,不同的PCB布局当中是不同的,因此在计算当中我做了修改,在实际的运用当中,我们贴片式晶振中电容一般选

2021-08-12 08:27:58

本帖最后由 eehome 于 2013-1-5 09:57 编辑

晶振专业知识介绍 一、术语解释 1、频率准确度:在规定条件下,晶振输出频率相对于标称频率的允许偏离值.常用其相对值表示. 2

2012-12-18 17:41:53

本帖最后由 eehome 于 2013-1-5 09:50 编辑

晶振是晶体振荡器的简称,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以

2012-12-18 17:38:43

` 本帖最后由 music_mc 于 2016-3-25 00:07 编辑

电路如下图,STC单片机,上电晶振不起振用线把晶振任意一脚跟GND短接就能起振,或者用手摸摸晶振引脚也能起振,但关掉重新上电,又不能了,真晕无源晶振 22.1184mhz`

2016-03-24 21:00:56

哪位大侠来讲讲数字电路中的晶振的作用,或者说在单片机系统中,晶振的作用,越详细越好啊??

2014-03-08 19:58:03

晶振,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低的频率是串联谐振,较高的频率是并联谐振。由于晶体自身的特性致使这两个频率

2014-12-25 15:12:28

) 时钟信号的走线应尽量短,线宽大一些,在布线长度和远离发热源上寻找平衡。 (5) 晶振不要放置在PCB板的边缘,在板卡设计时尤其注意该点。

2018-09-19 16:31:11

工作频率不稳定,自然容易出现问题.晶振是晶体振荡器的简称.它用一种能把电能和机械能相互转化的晶体在共振的状态下工作,以提供稳定,精确的单频振荡.在通常工作条件下,普通的晶振频率绝对精度可达百万分之五十

2016-08-12 20:34:53

不要走信号线,避免带来干扰。 10、其他问题导致晶振不起振 二、晶振设计、过程中的建议 1、在PCB布线时,晶振电路的走线尽可能的短直,并尽可能靠近MCU。尽量降低振荡电路中的杂散电容对晶振

2020-10-21 06:42:08

、温度范围、输出电压、功率、输出波形、封装尺寸和外形。PCB布线位置:晶振容易损坏,所以要原理板边,靠近MCU。耦合电容:耦合电容应尽量靠近晶振的电源引脚。如果多个电容耦合,要按照电流流入的方向,依次容值从大到小摆放。走线:高速时钟信号线优先级最高。一般在布线时,需要优先考虑主时钟信号线。时钟线信

2022-02-11 08:02:03

`晶振在电路中用“X”、“Y”或者“Z”来表示。通常分为有源晶振和无源晶振两个大类,无源晶振需要芯片内部有振荡器,而且晶振的信号电压是根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度

2012-10-16 13:26:21

:晶振的负载电容=[(Cd*Cg)/(Cd Cg)] Cic △C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容) △C(PCB上电容)一般为3至5pf. 所以我们在采购

2016-05-18 20:38:27

产品做EMC测试时辐射超标,44MHz和88MHz,应该是使用的22.1184MHz无源晶振辐射导致的,除了优化PCB外另外考虑晶振本身的辐射特性,不知道在相同条件下无源晶振辐射小 还是有源晶振辐射更小?望有类似经验的朋友不吝赐教。

2019-05-05 17:51:36

`` 不是所有的东西都完美无瑕疵,就像电子产品都会出现一定的误差一个道理。如题我们今天将要说的就是晶振误差的相关问题,晶振的误差是怎么回事呢?在什么情况下晶振会出现误差呢?晶振的误差如果太大会导致

2016-09-03 14:16:32

测试晶格:指晶圆表面具有电路元件及特殊装置的晶格,在晶圆制造期间,这些测试晶格需要通过电流测试,才能被切割下来 4 边缘晶格:晶圆制造完成后,其边缘会产生部分尺寸不完整的晶格,此即为边缘晶格,这些

2011-12-01 15:30:07

我在使用AD7768的过程中,clk_sel拉高,使用外部晶振或者LVDS,使用LVDS的时候采样正常,但是用无源晶振的时候晶振无法起振,是不是除了clk_sel拉高之外还需要什么设置才会使用外部晶振

2023-12-11 08:22:54

晶振与晶体的区别是什么?MEMS硅晶振与石英晶振区别是什么?晶振与晶体的参数有哪些?

2021-06-08 07:03:42

在学习设计过程中,有一些地方不怎么明白,网上搜到的答案不满意,希望有经验的人给予指导。在STM32F103C8T6的数据手册中,低速外部时钟32.678khz的晶振。手册上写到:CL1和CL2,建议

2017-06-05 15:02:25

项目都没有外部晶振,是使用内部晶振,虽然精度相对来说没有外部的高,但是项目也没有使用到很精确时钟的地方。下面来分析一下怎么在正点原子官方Demo的基础上修改成内部晶振。首先要明确的是内部晶振精度相...

2021-08-10 06:25:22

AD2S1210需采用同一个晶振,有源晶振与无源晶振会有影响吗?2、两片ad2s1210(粗机与精机)数据读取是先后对于数值的正确有影响吗?3、就是下面这个电路(附件中)通过SPI总线读取数据的接法正确吗?谢谢!附件ad2s1210.doc78.0 KB

2019-03-08 15:51:02

在遇到事情是要以一分为二,对于晶振也不例外,应从内外因不同的角度来分析晶振停振。下面我们以内外因来分析晶振停振。 有许多工程师在遇到,晶振在电路板,一会儿起振,一会儿不起振,或用电吹风吹一下又可

2018-03-17 20:45:39

陶瓷封装制品,如果电路上EMC较大,则尽量选用金属封装制品。另外晶振下面不要走信号线,避免带来干扰。10、其他问题导致晶振不起振晶振设计、过程中的建议1、在PCB布线时,晶振电路的走线尽可能的短直,并尽可能

2017-10-25 15:09:17

为什么51单片机爱用11.0592MHZ晶振?在设计51单片机系统PCB时,晶振为何被要求紧挨着单片机?单片机电路晶振不起振的原因有哪些?单片机晶振电路中两个微调电容不对称会怎样?

2021-04-19 09:27:36

不会有很大的变化。晶振有一个重要的参数,那就是负载电容值,选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。 一般的晶振振荡电路都是在一个反相放大器(注意是放大器不是反相器)的两端接入晶振

2012-12-10 14:02:58

`晶振是晶体振荡器的简称,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络。电工学上这个网络有两个谐振点,以频率的高低分,其中较低的频率是串联谐振;较高的频率是并联谐振。由于晶体

2017-06-23 14:26:15

可由两个极限温度的频差可算出最小温度频飘可以做到20PPM,这个数值越小,相对的该产品质量也越好,当然在成本上也是高了很多的。工业级晶振与普通民用级晶振比有什么区别呢? 与民用级晶振相比,工业级晶振在

2016-08-04 15:15:00

高端处理器,温补晶振(TCXO)可以确保系统在不同环境下都能正常工作。

三、晶体的布局布线指南

1、晶体布局:

优先考虑紧凑布局,将元件优先放置在TOP层,尽量靠近IC管脚。

为降低寄生电容,当放置

2024-01-04 11:54:47

) 试着改换晶体两端的电容,也许晶振就能起振了,电容的大小请参考晶振的使用说明。(5) 在PCB布线时晶振电路的走线应尽量短且尽可能靠近IC,杜绝在晶振两脚间走线。

2019-09-25 08:27:35

1、单片机晶振不起振原因分析遇到单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?(1) PCB板布线错误;(2) 单片机质量有问题;(3) 晶振质量有问题;(4) 负载电容或匹配

2021-11-25 09:04:03

AD2S1210需采用同一个晶振,有源晶振与无源晶振会有影响吗?

2、两片ad2s1210(粗机与精机)数据读取是先后对于数值的正确有影响吗?

3、就是下面这个电路(附件中)通过SPI总线读取数据的接法正确吗?

谢谢!

2023-12-22 06:23:59

请教因为晶振旁边连接2个电容来谐振,所以我判断是无源晶振靠谱吗?还有怎么判断这个晶振的好坏,我只有万用表和一个还不会用的示波器。(晶振在PCB上,不拆下来的前提下)多谢指点。

2018-11-19 14:17:56

的大小请参考晶振的使用说明。(5) 在PCB布线时晶振电路的走线应尽量短且尽可能靠近IC,杜绝在晶振两脚间走线。使用注意事项:另引起晶振频率偏差的原因有:温度、老化等。在做产品时,不仅需要

2018-02-07 10:55:51

为什么晶振会有三脚和两脚,分别起到的作用又是什么呢?今天松季电子为大家介绍常见的晶振的“脚”的作用。 大家都知道,常见的晶振基本上都是二只脚,三脚的晶振其实是一种集晶振和电容为一体的复合元件

2013-10-28 15:43:01

电容值不正确。

3. PCB Layout 分析

**·**检查布局:使用电路设计软件或手动检查PCB Layout,确保晶振电路与单片机或芯片引脚的布局尽可能靠近,以减少信号传输的干扰和损耗

2024-03-06 17:22:17

` 本帖最后由 gk320830 于 2015-3-9 15:28 编辑

做了个5M石英晶振电路,用示波器看有0.1%频率误差,我看资料晶体振荡电路一般能达到几十ppm的精度,但我怎么调其他参数也达不到这个水平,会不会是受限无源晶振本身的精度,或者说有些无源晶振可能稳定性差?`

2011-12-07 17:38:09

偶尔会有晶振失效的现象。最后用有源晶振代替了无源晶振,低温环境下无论是恒温测试还是升温测试,都没有出现问题。求教无源晶振低温下,尤其是在升温过程中失效的原因?顺带着有解决办法是最好的啦~

2014-12-17 12:56:05

本帖最后由 anshengji 于 2016-1-22 20:37 编辑

直接用示波器测量输出与地之间的波形,波形频率域晶振频率相符,说明起振。无源晶振起振时,两个引脚上均会有震荡波形,用

2016-01-18 18:31:49

为什么51单片机爱用11.0592MHZ晶振?在设计51单片机系统PCB时,晶振为何被要求紧挨着单片机?单片机电路晶振不起振原因是什么?51单片机时钟电路用12MHZ的晶振时那电容的值是怎样得出

2021-09-23 07:22:06

借助外部电路起振,有人分析说,当有源晶振取代无源晶振在电路中使用,成本将会提高60%。如下表格所示晶振电路元件价格(RMB)晶振总价有源晶振电路有源晶振4元4.0无源晶振电路无源晶振0.81.4无缘冲

2015-01-30 11:06:01

比较常用的晶振PCB封装

2017-12-13 09:32:26

除了内部晶片较薄以外,再就是自身有加一个振荡片。那么基频晶振和泛音晶振在使用上又会有什么不用了。他们在使用上肯定是有区别的,泛音晶振是需要电感和电容配合使用才可振出泛音频率,否则就只能振出基频了,而基频的晶体,就只需要接入适当的电容就可以工作了。

2016-06-07 10:57:30

深圳回收晶振 收购晶振深圳回收晶振 收购晶振,优势回收◆◆ 我司专业收购晶振,回收有源晶振,收购无源晶振,帝欧电子长年专业收购壹:回收日本晶振品牌如下:爱普生Epson、日本电波NDK、京瓷

2021-01-04 17:11:46

温度变化产生的振荡频率变化量削减的一种石英晶体振荡器。 2、凡是需要提供电源电压的都是有源晶振,它大致包括普通晶振、压控晶振、温补晶振、恒温晶振。 3、温补晶振属于有源晶振,它是在普通晶振的基础上

2013-08-14 16:03:58

就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越大,晶体在PCB边缘与在PCB中间时电场分布如下:PCB边缘的晶振与参考接地板之间

2020-06-09 15:44:58

晶振有两脚和三脚之分,这是晶振电路符号 这是晶振在PCB板电路上正面图 这是晶振内部结构和电路符号 这是石英晶体的压电效应示意图 这是晶振等效电路和实验电路 这是恒温晶体振荡器原理框图 这是MCXO数字温补晶振原理框图

2017-04-10 11:10:06

陶瓷封装制品,如果电路上EMC较大,则尽量选用金属封装制品。另外晶振下面不要走信号线,避免带来干扰。10、其他问题导致晶振不起振晶振设计、过程中的建议1、在PCB布线时,晶振电路的走线尽可能的短直,并

2017-11-07 15:21:22

陶瓷封装制品,如果电路上EMC较大,则尽量选用金属封装制品。另外晶振下面不要走信号线,避免带来干扰。10、其他问题导致晶振不起振晶振设计、过程中的建议 1、在PCB布线时,晶振电路的走线尽可能的短直,并

2017-10-25 14:35:47

的地方呢,很郁闷呢!没事,听完松季电子的介绍,相信你定会有一种柳暗花明的感觉!走吧...... 一、针对MHZ的晶振,我们需要清楚的知道晶振的型号(或者是体积)。如若在只知道体积的情况,我们还需要

2014-03-27 16:12:23

CPU是STM32F103,在晶振两脚之间走了一些线,这对电路性能会有影响吗?影响多大?可以忽略吗?

2019-05-13 04:34:13

在画PCB的时候,8M晶振底下是不是不能走线? 晶振到STM32输入的两个引脚不能经过过孔对吗?

2019-03-18 06:35:52

很多电子元器件封装都可以大致分为贴片式和直插式,同理,晶振种类也可以分为贴片晶振和插件晶振,今天松季电子为大家介绍贴片晶振与插件晶振的运用: 一、如果是基于同一个频率、同种类型晶振,那么在

2013-11-04 16:54:20

本帖最后由 maskmyself 于 2016-7-11 09:01 编辑

晶振的使用范围广,种类分很多种,从焊接方式有分为插件式和表贴式晶振。从使用性能上分为有源晶振和无源晶振,这些我们在

2016-07-07 10:56:09

在PCBA生产加工中会遇到很多问题,有些在PCB板子设计时就可以规避,今天众焱电子就要带大家了解下晶振为什么不能放置在PCB边缘。 1、问题描述 某行车记录仪,测试的时候要加一个外接适配器,在机器

2021-03-18 17:50:46 3329

3329 电瓶修复技术-电池化成没有完成放置会有什么后果?

2021-11-10 11:42:51 542

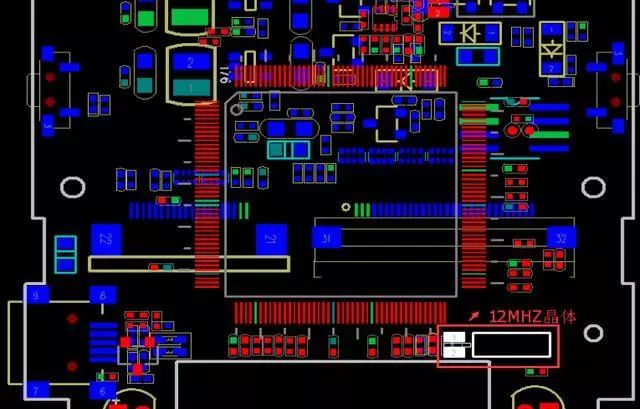

542 从PCB布局可以看出,12MHz的晶体正好布置在了PCB边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与实验室中参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强。

2022-10-17 15:52:58 754

754 晶振在布局时,一般是不能放置在PCB边缘的,今天以一个实际案例讲解。

2023-05-16 17:04:07 745

745

,晶振在工作时需要保持稳定的振荡频率。晶振的运行稳定性对于整个电子设备的正常工作至关重要。放置在PCB边缘,晶振更容易受到外部干扰。例如,边缘可能会有电磁辐射等干扰源,这些干扰源可能会使晶振受到干扰,进而影响振荡频率的稳定性。

2023-11-29 16:07:34 645

645 时钟(Clock)在一般SoC电路上是必不可少的,精准的时钟通常由晶振提供,晶振很难集成到芯片中去,而是作为分立元件设计在PCB上

2022-06-23 08:47:30

电子发烧友App

电子发烧友App

评论