Best practices for preparing a library for Capture-Allegro PCB Editor

flow

Limit part and pin names to 31 characters

Use upper case characters for part/symbol names, part references

designators, and pin names

Do not use special characters to assign part names, references

designators, and pin names

Do not use duplicate pin names for pins other than power pins

For multiple power pins with the same pin names, do not make some

pins visible and other invisible

Do not use "0" as a pin number

Best practices for Capture design for Allegro PCB Editor

While defining a net list alias or a net name

• Keep the maximum length of a net name or alias up to 31

characters

• Do not use lower case or special characters in a net name

Avoid using "Power Pins Visible" property at design level

Use net to connect pins

• Leave room for assigning a net name. Pin-to-pin connection

changes the net name when a user moves a component

Run the Capture DRC command before generating Allegro PCB Editor

netlist

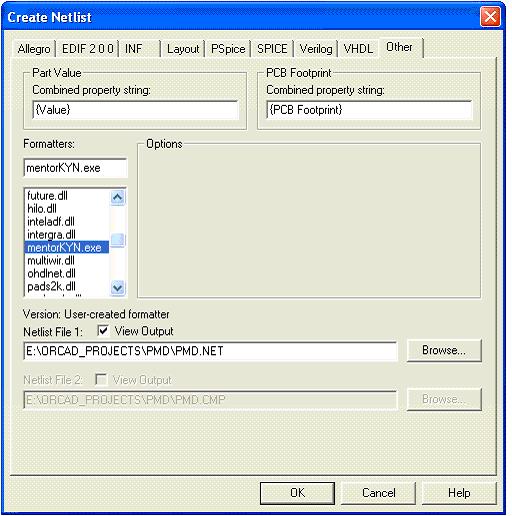

Set path for Allegro PCB Editor footprint before running Netrev

Best practices for smooth back annotation

Do not change design name, hierarchical block names, or reference

designators in Capture after board files creation

Do not edit a part from schematic in Capture after board file

creation

Do not replace cache as it changes the Source library name and part

name, in capture

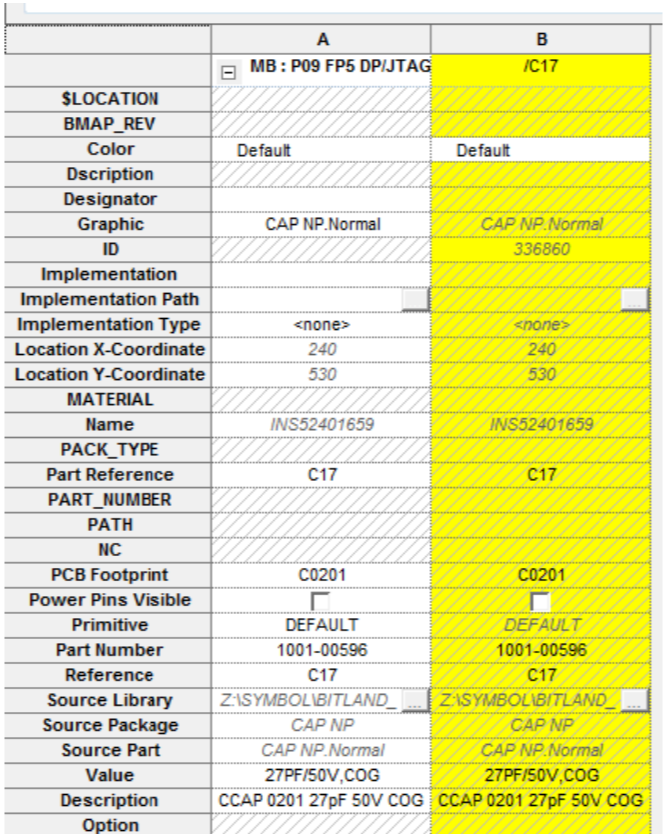

Do not change the values of component definition properties in

capture after board files creation

Do not change Design file/root schematic/hierarchical block names

in Capture after board file creation

Do not add or delete components to or from the schematic design

immediately after the board file creation. Add or delete components

after finishing the back annotation process

Do not add any additional components in Allegro PCB Editor. Instead,

add components in Capture and take them to Allegro PCB Editor

Do not add, rename, or delete a net in Allegro PCB Editor

Do not change the format for reference designators for parts in

Allegro PCB Editor as

>

Run Allegro PCB Editor Dbdoctor before running Back annotation by

selecting the Database Check command from the Tools menu in Allegro

PCB Editor

Make backups of the original design before updating the design with

the swap information in Capture

Back annotate the design immediately after making the board file.

Though it does not a mandatory step, back annotating the design

before placing components helps avoid problems in back-annotation

at a later stage.

If back annotation at this stage generates an empty swap file, you

can proceed with placing and routing the board file. In case any

problems are detected, you must correct them in the design file and

generate the board file again until an empty swap file is generated.

- Best(7230)

- egro(6414)

相关推荐

orcad capture转换到mentor的方法

3170

3170

Capture CIS数据库配置问题

capture原理图怎么导入altuim 9中

capture和PADS2007

Cal all channels错误消息

DM8168图像Capture + Display,Display不对是为什么?

ORCAD CAPTURE 怎么产生这种微波波形??

ORCAD capture 打开DSN文件的问题

Quad Flat No-Lead QFN应用笔记和最佳实践

SJ50系列II回流焊后软件算法手册

SJ50系列II预回流软件算法手册

Virtex-5中的Microblaze和Capture-Restore过程出现问题

dm368 capture

ieee.std_logic_signed.all和ieee.std_logic_unsigned.all同时用出现报错怎么解决?

orcad capture pspice不能用

orcad capture无法复制原理图

为什么orcad9.2版本在capture里画好电路图,生成layout,为什么在capture里改电阻阻值,layout里没有及时更新?

在示波器上怎么捕获和保存多个通道

打开capture后出现d:\cadence\SPB_16.3\Tools\capture was not found

无法找到Intuilink Data Capture的Add In

是德科技过程分析

最新的Capture SDK和DLL的头文件不匹配

有什么方法可以使用SEM和CAPTURE原语吗?

模拟电路世界级设计 经典模电教程

组合逻辑设计实践- Combinational logic design practices-(数字设计原理与实践)

请问data capture功能怎么使用

orcad/capture cis 9实用教程

0

0宁波BEST贝斯特滤芯

基于Quick Capture 技术的摄像头驱动方案

16

16一种有效的 N-Best 算法及其在中文语音识别中的应用

25

25Cisco Wireless LAN Security

5

5思科无线局域网安全

48

48OrCAD Capture CIS 9 实用教程 (pdf格

0

0Memory Interfaces Data Capture

12

12Capture to Allegro Interface

0

0印刷电路板设计的最佳实践 Best Practices in

1090

1090力科产品荣膺09年度“Best in Test”奖项

460

460什么是AOWC (All-Optical Wavelengt

447

447什么是AON (All-Optical Network)

970

970什么是Best Effort

1263

1263How do I Choose the Best FireW

1038

1038Cadence ORCAD CAPTURE元件库介绍

0

0XAPP105 - CPLD VHDL介绍

17

17AN2394_CapSense™ Best Practices

11

11PCIe、NVMe协议分析仪

52

52PCBArtistTutorial

0

0Orcad Capture® Quick Reference

0

0使用2×4 MIMO-OFDM系统模型下的K-Best算法设计的K-Best检测器

3374

3374区块链:All In需要具备哪些能力?

409

409用OpenMP和SIMD并行加速应用程序的性能

3137

3137Android开发的最佳实践

1192

1192闻泰科技荣获LG电子“Best Quality Award”

3692

3692OrCAD Capture的使用培训教程免费下载

0

0测试实验,带你快速了解Matterport Capture

3326

3326AD7380/AD7381: What oversampling method is best for an application?

5

5基于24 Channel Video Capture CardField-Programmable Gate Array的参考设计

10

10Javascript-best-practice

6

6Capture-Screen-On-Mac Mac OS X下的截屏实现

0

0OrCAD Capture CIS instance和occurrences概念解析

7051

7051

合宙Air系列开发板官方demo学习(二):camera-摄像头:(1)-capture

722

722

孟晚舟称将打造中国算力底座 华为All Intelligence启动

665

665 电子发烧友App

电子发烧友App

评论