您是否知道音箱之所以有这么出色的低音高音的音质效果完全得力于一个音箱设备中的音响分频器,如果没有这个小小的音箱分频器,音箱根本就不可能有出色的音质效果。本文主要带领大家来了解一下分频器的计算和调整,首先来了解一下分频器原理及是分频点,其次详细了解分频器计算的顺序以及调整方法。

分频器简介

分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放。在高质量声音重放时,需要进行电子分频处理。

分频器是音箱内的一种电路装置,用以将输入的模拟音频信号分离成高音、中音、低音等不同部分,然后分别送入相应的高、中、低音喇叭单元中重放。之所以这样做,是因为任何单一的喇叭都不可能完美的将声音的各个频段完整的重放出来。

分频器是音箱中的“大脑”,对音质的好坏至关重要。功放输出的音乐讯号必须经过分频器中的过滤波元件处理,让各单元特定频率的讯号通过。要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍、明朗、舒适、宽广、自然的音质效果。

在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频器是音箱中的“大脑”,分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。尤其在中、高频部分,分频电路所起到的作用就更为明显。

分频器原理

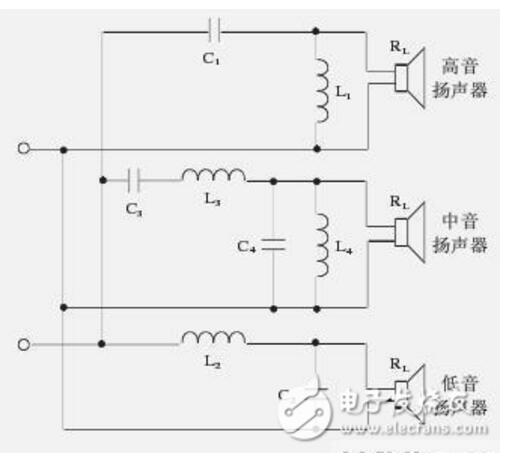

从电路结构来看,分频器本质上是由电容器和电感线圈构成的LC滤波网络,高音通道是高通滤波器,它只让高频信号通过而阻止低频信号;低音通道正好相反,它只让低音通过而阻止高频信号;中音通道则是一个带通滤波器,除了一低一高两个分频点之间的频率可以通过,高频成份和低频成份都将被阻止。在实际的分频器中,有时为了平衡高、低音单元之间的灵敏度差异,还要加入衰减电阻;另外,有些分频器中还加入了由电阻、电容构成的阻抗补偿网络,其目的是使音箱的阻抗曲线心理平坦一些,以便于功放驱动。

由于现在的音箱几乎都采用多单元分频段重放的设计方式,所以必须有一种装置,能够将功放送来的全频带音乐信号按需要划分为高音、低音输出或者高音、中音、低音输出,才能跟相应的喇叭单元连接,分频器就是这样的装置。如果把全频带信号不加分配地直接送入高、中、低音单元中去,在单元频响范围之外的那部分 “多余信号”会对正常频带内的信号还原产生不利影响,甚至可能使高音、中音单元损坏。

分频点介绍

分频点指分频器高通、带通和低通滤波器之间的分界点,常用频率来表示,单位为赫兹。高低音两分频音箱只有一个分频点,高、中、低三分频音箱有两个分频点,分频点应根据各频段扬声器单元或音箱的频率特性和功率分配来具体确定。

分频点通常定义为两个分频器的响应(一般由一个LPF和一个HPF组成)互相交叉处的频率,可能是两个电子分频器(从动或主动式)电学特性上的分频点,或者是两个声学滤波器上的分频点。任何喇叭单元实质上都是一个滤波器,每一个都有他们内部所固有的高通和低通滤波器,以及固有的截止频率,斜率,网络类型。

一个系统的总体声学分频点取决于这个系统中电子滤波器与喇叭单元频率响应的数学组合,当一个电子滤波器添加到一个声学滤波器系统时,他们的频率响应将叠加,形成一个全新的响应曲线。

两个不同单元之间的声级/灵敏度差异,及高频器件的相位滞后都是显而易见的。高频部分很可能被固定在一个长喉管的号筒上,因此产生相对于低频扬声器的延迟,为了更好地使系统重现信号,最新发展的分频器要求能够平滑频率响应曲线。

分频器的计算和调整方法

1、计算顺序

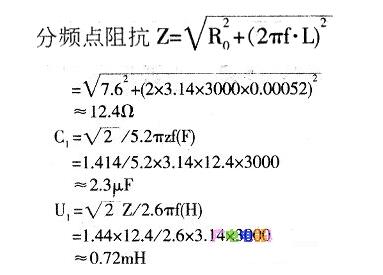

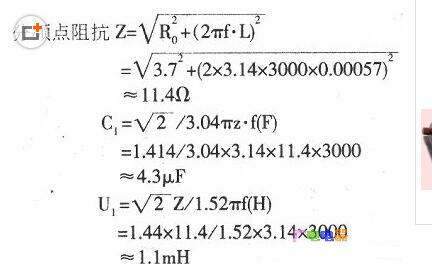

目前大部分资料介绍的计算方法是以扬声器额定阻抗为定值求得分频频率的LC值,然后在试音时调整参数。实践证明这种方法计算结果与最后的调整参数误差太大,因为其阻抗会随着频率的升高而增大。虽然在扬声器两端并联RC串联谐振回路可使其阻抗稳定在额定阻抗附近,但是在业余条件下无专用仪器,分频元件越多,相移越大,所以这两种方法不可取。事实说明以扬声器在分频点处的阻抗为定值,求得分频频率的LC值准确度较高。本文以常见的双中低音倒相箱为例,介绍采用12dB/oct-6dB降落点交叉的二分频网络的计算方法。根据高低音扬声器的参数,分频点取3kHz。

用数字万用表测得高音直流电阻Ro=7.6Ω,电感量L=0.52mH。

用数字万用表测得双中低音并联直流电阻Ro=3.7Ω,并联电感量L=0.57mH,

2、调整方法

将扬声器装入音箱,选用大4P接线盒和双线分音法。把扬声器和接线盒内接线焊好。分频器采用外接搭焊方式,这样调整方便。

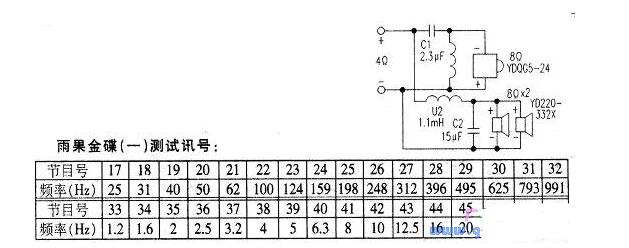

附表所列是用数字频率表测得的《雨果金碟(一)》

17—45段的讯号频率。虽然有一定的误差,但是作为调整分频器使用已经足够。

在正常听音音量状态下,播放测试讯号时,发现分频苣2.5kHz~4kHz处声压较高。把其中一只音箱高音同相连接,用合并功放的平衡旋钮反复比较分频点及其他各点声压,无明显差别。通过以往多次制作分频器的经验,说明这不是计算值偏差较大。其主要原因是在业务条件下无法得到扬声器的频响曲线图。分频点落在高低音的峰点上,包括扬声器装入箱体后对频响曲线的影响。郡么现在该调整高音的分频网络还是低音的分频网络呢?

根据扬声器的参数得知,高音灵敏度为91dB,中低音为89dB。当两只中低音并联使用时,阻抗为4Ω,使高音灵敏度下降。另外,试听时距扬声器LOCm处可听到高音在2.5kHz处被衰减的声压,2kHz处已听不到。由于其频响低端达1.5kHz,说明分频网络正确。而中低频扬声器在4kHz处仍然有较高声压。以上两点说明应调整低通网络。

本着先易后难的原则,试着将C2逐渐换大容量。

当其容量为15μF时,已听不到中低频扬声器在4kHz上的频率信号。同时3.2kHz附近的声压也得到适当的衰减。分频器LC元件参数如附图所示。

3、相位问题

如果你注意的话,可发现在报刊上登载的二分频网络中,大部分高音是反相连接,少数是同相连接。按本文介绍的计算方法,该同相还是反相连接的鉴别处主要在高低音分频频率的交叉位置上。如果同相连接时,在交叉处的声压较小,而反相连接时交叉处的声压升高,则应反相连接。这样相位失真最小,如果合成的声压偏高可相应调整分频网络LC值,反之也一样。所以我们不能武断地认为高音就应该反相接线,而应以试听比较后下结论。对本文分频电路,经多次近听远听反复比较,因无明显差别,最后还是以常见的高音反相接法画出。

-

分频器

+关注

关注

43文章

433浏览量

49312 -

分频点

+关注

关注

5文章

7浏览量

7729

发布评论请先 登录

相关推荐

分频器的作用 分频器的功率是不是越大越好

CAN时钟分频器在CANbus模块上不执行任何操作的原因?

FPGA学习-分频器设计

Sigma-Delta小数分频PLL中的分频器该怎么做?

分频器的常见用途

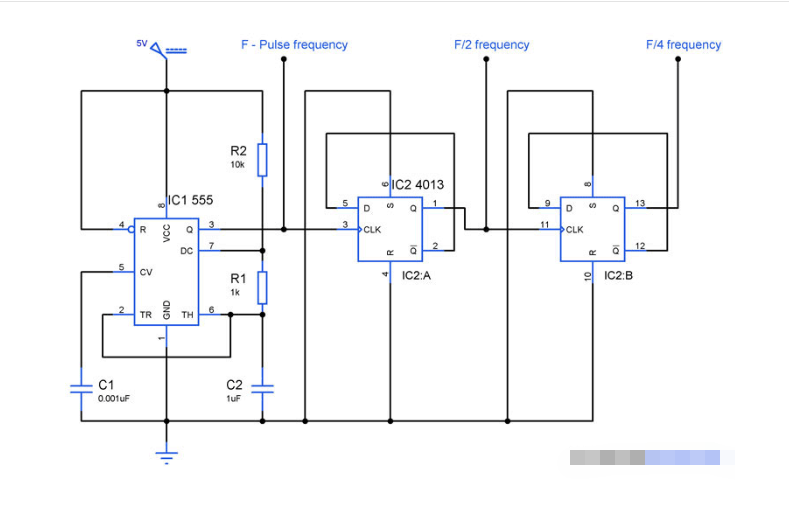

使用IC555和IC4013构建的分频器电路

029lan的pwm预分频器设置最少要为1吗,即2分频,设为0时没有输出是为什么?

一文详解分频器的计算和调整方法

一文详解分频器的计算和调整方法

评论