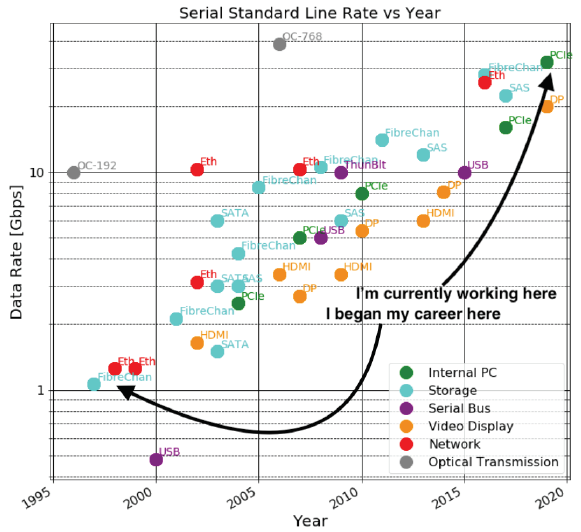

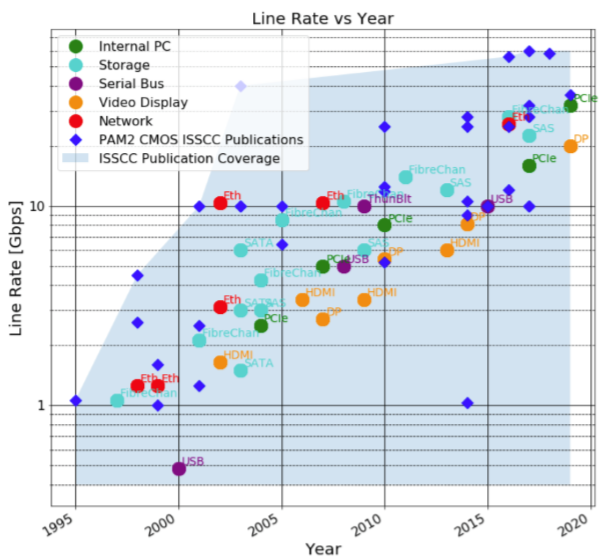

尽管SERDES(SERializer/DESerializer)拥有十分复杂的设计和验证过程,但已成为SoC中不可或缺的组成部分。成熟稳定的SERDESIP,降低了设计成本和风险,加快了产品SoC产品上市的速度。如今,PCIe、HDMI以及USB这样的高速接口已变得不可或缺,但20年前的情况并不是这样,过去的20年中,串行接口应用数量经历了爆炸性的增长。下图展示了从上世纪九十年代末开始,SERDES二十年的革命之路。本文将通过一些底层技术的简单介绍,尝试解释下为什么串行接口(以SERDES为代表)变得如此流行。

SERDES在1995-2020年间的演进(根据应用场景划分)

起源和演化

SERDES在光纤和同轴链路通信场景下广为使用,其原因显而易见,使用串行传输而非并行传输可以节约电缆数量!对于仅有的几条线缆,最大限度的提高其吞吐量显得尤为重要,这种情况下SERDES的面积和功耗则成了次要考虑的因素。在上世纪80年代中期,串口上的数据速率很大程度上是由电信需求决定的(同步光纤网络SONET)。在这段时期,若以今天的标准(51.84Mb/s,155.52Mb/s)看来,OC(光载OpticalCarrier)-1和OC-3的要求不算太高。OC-24要求单通道的传输速率要超过1Gb/s(1244.16Mb/s),它使用的是1990年左右最先进的双极(bipolar)和砷化镓(GaAs)工艺。上世纪90年代后期,是SERDES历史上的一个重要时期:OC-24(2488.32Mb/s)开始投入使用,同时速度大约为10Gb/s的OC-192也在规划之中。几年后(2000年代初),10Gb/s线速的以太网面世,与XAUI不同,XAUI使用4个通道合并从而达到10Gb/s(XAUI接口读作“Zowie”,其中的“AUI”部分指的是以太网连接单元接口(EthernetAttachmentUnitInterface);“X”代表罗马数字10,它意味着每秒万兆(10Gbps))。接下来,SERDES另一个重要的发展时期开始了——SERDES正越来越多地用于PCB底板上的片间通信,以取代并行接口。这个进步把SERDES从一个重要的长途通信电路变成了SoC上的关键模块。在这一点上也许PCIe是最好的例子,PCIe在2002年开始使用2.5Gbps的带宽,并在2000年代中期开始变得流行起来。各种串行数据标准的推出和SERDES研究的状态如图1所示。他们包括:

光纤传输:OC-192,OC-768,SONET

PC内部接口:PCIe1-5代

存储:光纤通道(FibreChannel),SATA,SAS

视频显示:显示接口(DisplayPort),HDMI

网络:SGMII,1-Gb以太网,10-Gb以太网,25/100-Gb以太网

注:SATA:一种串行数据传输总线,SATA是SerialATA的缩写,即串行ATA。它是一种电脑总线,主要功能是用作主板和大量存储设备(如硬盘及光盘驱动器)之间的数据传输。

SAS:用于外设数据传输。串行SCSI(SAS:SerialAttachedSmallComputerSystemInterface)是一种电脑集线的技术,其功能主要是做外设的数据传输,如:硬盘、CD-ROM等设备而设计的接口。SGMII:是一个普通高速串行信号,SGMII--SerialGigabitMediaIndependentInterface,用于MAC和PHY之间的传输。SGMII接口就是使用了SerDes技术的GMII接口。

自此以后,各类接口的速率开始毫无意外地以指数级增长,其中以光纤传输速率尤为明显。上面还都仅是使用NRZ(PAM2)标准的接口,PAM4标准则以50Gb/s的传输速度起步并脱颖而出。

为了让大家更好地理解电路级上的创新如何推动SERDES地发展进程,使用IEEE的Xplore数字图书馆查询了国际固态电路会议(ISSCC)的出版物,生成了ISSCC出版物列表,其中包括关键字“时钟和数据恢复”和“SERDES”。然后将数据集分解为一下4类:

工艺类型:CMOS和非CMOS(bipolar、biCMOS、HBT等)

工艺节点:65nm,40nm,7nm等。

信号传输标准:PAM2、PAM4

组织出版:工业、学术

注:HBT-heterojunctionbipolartransistor,异质结双极型晶体管,其原理是因为不同的半导体材质,其能带结构不一样,两者相处时的界面会因为能带(费米能级相同)形成独特的过渡层,因为多一个自由度,而能够提取出优异的(同质结所没有的)高速特性。

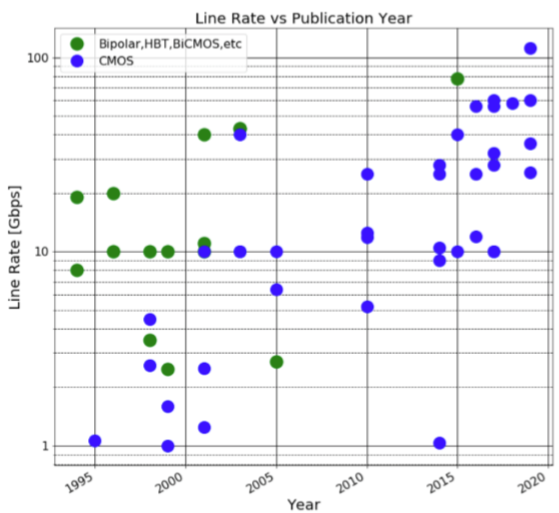

基于这些数据,以线速为纵轴,论文出版年份为横轴绘制出下图。据估计,电路设计完成时间大约在出版前一年,然而,新技术可能在出版几年后才会在工业应用上出现。

线速-出版文献年份分布情况(根据工艺类型划分)

这个图表明bipolar,biCMOS和HBT技术在2005年之前就已被大量研究,但是2005年以后就很少了。这些2005年前的论文描述了驱动光纤网络应用的技术,其中线速是最重要的,而功耗、外形、集成则是次要的考虑因素。

对于具有更大容量的SERDES应用案例,如PC、存储、视频显示和网络,线速不再是人们考虑的唯一因素,成本、功耗、形状以及和大规模数字处理器的集成都变成了必须要考虑的重要因素。

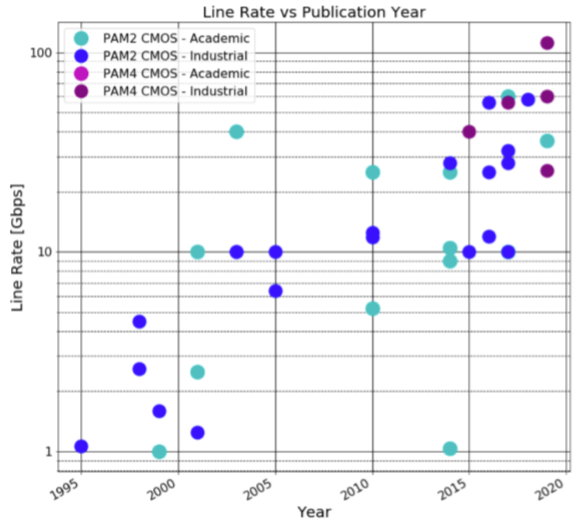

线速-出版文献年份分布情况(根据工业界/学术界以及PAM2/PAM4划分)

图3是按照学术界和工业界以及PAM2和PAM4划分的ISSCC数据情况。值得注意的一点是,PAM4和PAM2的论文大致以28Gb/s线速上下来划分。这与串行数据标准的未来预期大致吻合。

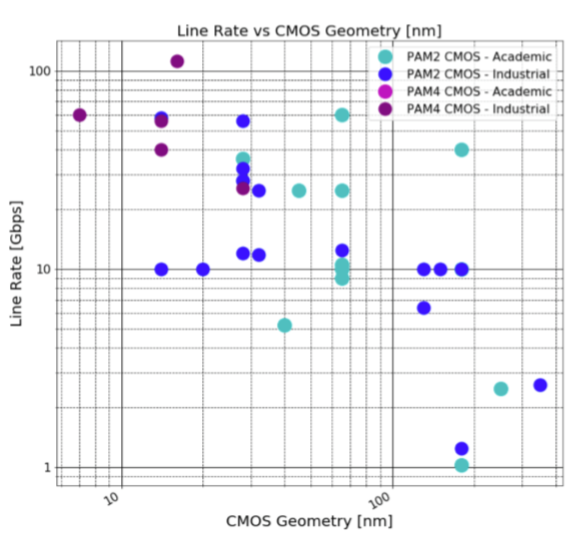

线速-工艺节点的出版分布情况(根据工业界/学术界以及PAM2/PAM4划分)图4展示了CMOS工艺节点和线速之间的关系:90nm以下的工艺节点的大部分线速都在10Gb/s以上。另外,PAM4由于通常需要和ADC/DSP高度集成并且对带宽有着非常高的要求(这是PAM2不具备的),因此通常在28nm工艺以下。从图4也可以很明显的看出,学术界关于PAM4的论文很少,这可能是由于设置了搜索条件引起的。学术界常常出版和PAM4“部件”相关的论文,但却很少出版论述“完整”PAM4收发器的文献。PAM4的系统太过庞大(包括ADCs,DACs,DSP,PLLs,CDRs等),并且先进的CMOS工艺(如7nm,14/16nm)的成本和获取途径对学术界并不友好。将串行链路发布和串行数据率标准的搜索结果结合在一起,可以得到图5中的信息,ISSCC的先进CMOS电路设计出版物在从网络到显示器的高容量串行数据标准方面领先了好几年。PAM2CMOS的研究已经让PCIe1到PCIe5(32Gb/s)、28Gb/s以太网线路速率等成果成为现实。

ISSCC出版物覆盖情况

原文标题:SerDes的好处在哪里(上)

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

存储

+关注

关注

12文章

3880浏览量

84757 -

电缆

+关注

关注

18文章

2454浏览量

53740 -

晶体管

+关注

关注

77文章

9091浏览量

135461 -

串行接口

+关注

关注

3文章

307浏览量

42289

发布评论请先 登录

相关推荐

串行音频接口(SAI)中slot是什么意思?

昂科烧录器支持XinCun芯存科技的串行外设接口NAND闪存 XCSP4AAPK-IT

SIMATIC S7-1500 PLC的通信及其应用—RS-485标准串行接口

AXI IIC总线接口介绍

SPI串行外设接口设计实现

为什么串行接口变得如此流行

为什么串行接口变得如此流行

评论