数字时代芯倡议:建立产业命运共同体

新思科技全球资深副总裁兼中国董事⻓葛群接受集微网访谈,通过数字化转型根技术提供者的视⻆,解读后摩尔时代的半导体行业变化。葛群强调,数字化带来的市场机会和技术挑战并存,半导体产业链可能会随时⾯临各种不确定因素,他提出“+新思”的说法来倡议建⽴芯⽚产业命运共同体,希望所有的合作伙伴和客户都能够拥有更多新技术、新的思想、新的思路,希望中国半导体产业⼤家庭在‘新思’的帮助下得到更⾼质量和更⾼速度的发展。

新思科技任命 Sassine Ghazi 为总裁兼首席运营官

新思科技近日宣布任命 Sassine Ghazi 为总裁兼首席运营官,自2021年11月1日起生效。Sassine Ghazi 于1998年加入新思科技,在芯片设计、应用工程、客户支持、销售和业务管理方面拥有数十年的经验。在被任命为首席运营官之前,Sassine Ghazi 担任新思科技设计事业部总经理,主导了诸多影响市场的新产品开发,极大程度推动了公司业务的发展。

新思科技收购Concertio,芯片全生命周期管理再度升级

新思科技收购AI驱动的性能优化软件领先企业 Concertio,将实时现场优化技术融入其芯片生命周期管理解决方案,本次收购强化了新思科技 SiliconMAX 芯片生命周期管理平台,实现边缘层的AI与云层的大数据分析之间的无缝安全集成,扩充了芯片在应用端和系统端的动态优化功能。

3DIC Compiler X 3DFabric,新思科技与台积公司联手提升系统集成至数千亿个晶体管

新思科技宣布扩大与台积公司的战略技术合作,提供更高水平的系统集成,以满足高性能计算(HPC)应用对更佳PPA(功耗、性能和面积)的需求。双方客户可通过新思科技的3DIC Compiler平台,高效访问基于台积公司的3DFabric设计方法,从而显著推进大容量3D系统的设计。

新思科技PrimeLib获三星5nm至3nm工艺认证,为高性能芯片设计提供5倍加速度

新思科技的PrimeLib统一库表征和验证解决方案获三星晶圆厂5nm、4nm和3nm工艺技术认证,可满足高性能计算、5G、汽车、超连接、以及人工智能芯片等下一代设计的高级计算需求。此次认证还包括对PrimeSim Continuum的验证,PrimeSim Continuum为新思科技Custom Design Platform和嵌入PrimeLib解决方案中的集成仿真器技术提供了基础,能够为开发者提供无缝仿真体验,协助其实现黄金质量签核。

新思科技数字和定制设计平台获得台积公司N3制程认证

新思科技数字定制设计平台已获台积公司N3制程技术认证,双方将共同优化下一代芯片的功耗、性能和面积(PPA)。基于多年的密切合作,本次经严格验证的认证是基于台积公司最新版本的设计规则手册(DRM)和制程设计套件(PDK)。此外,新思科技的数字和定制设计平台还通过了台积公司N4制程的认证。

N4P IP重磅发布!新思科技联合台积公司再放大招!

新思科技宣布与台积公司合作在其N4P工艺上开发广泛的DesignWare接口和基础IP核组合,提供高速且面积优化的低功耗嵌入式存储器、逻辑库、GPIO和TCAM,促进芯片创新,助力开发者高效设计出复杂的高性能计算(HPC)和移动SoC。基于这一合作,开发者可在台积公司的先进工艺上使用高质量IP核完成设计和项目进度,并在性能、功耗、面积、带宽和延迟等方面实现优化。

新思科技携手三星加快汽车SoC的ISO 26262合规进程

三星晶圆厂与新思科技就 VC 功能安全管理器解决方案开展合作,为汽车SoC的功能安全失效模式后果分析(FMEA)和失效模式后果诊断分析(FMEDA)提供关键自动化技术。三星与新思科技开展合作,将VC FSM作为新思科技统一功能安全解决方案的一部分加以推进,协助开发者在规划和实施阶段就可以确保其芯片安全架构能够达到汽车安全完整性水平(ASIL)目标。

第11年!新思科技再获台积公司年度合作伙伴奖,携手加速半导体创新

新思科技连续11年被评选为“台积公司OIP开放创新平台年度合作伙伴”,这也标志着双方将持续进行长期合作,共同推进下一代SoC和3DIC设计。今年台积公司授予新思科技的OIP年度合作伙伴奖项主要围绕Interface IP、4nm设计基础设施联合开发以及3DFabric设计解决方案联合开发。

新思科技携手GF推出业界首个22FDX汽车参考流程,加速云上创新

GlobalFoundries联合新思科技近日宣布,GF已在其22FDX工艺中认证了新思科技基于Amazon Web Services(AWS)的参考流程和汽车参考流程,双方共同推出的工艺设计套件和经认证参考流程可加速高性能汽车、边缘人工智能和5G SoC的开发

提前两月!新思科技功能安全验证解决方案助力RISC-V处理器IP通过ASIL D认证

凭借新思科技的Z01X功能安全验证解决方案,NSITEXE 的DR1000C并行处理器IP比预期提前两个月通过了ISO 26262汽车安全完整性等级(ASIL)D级认证,进一步佐证了新思科技在功能安全验证领域的领先地位。借助新思科技Z01X的速度和容量,NSITEXE现已推出业界首款通过ISO 26262 ASIL D级认证的矢量扩展RISC-V处理器,符合安全关键应用(如汽车)的最高功能安全标准。

原文标题:11月芯闻集锦,精彩别错过

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

处理器

+关注

关注

68文章

18269浏览量

222118 -

芯片

+关注

关注

447文章

47775浏览量

409080 -

新思科技

+关注

关注

5文章

716浏览量

50065

原文标题:11月芯闻集锦,精彩别错过

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Andes晶心科技与WITTENSTEIN合作建构RISC-V处理器安全解决方案

256核!赛昉发布全新RISC-V众核子系统IP平台

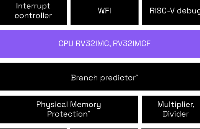

新思科技重磅发布全新RISC-V处理器系列扩大ARC IP组合

新思科技重磅发布全新RISC-V处理器系列,进一步扩大ARC处理器IP组合

思尔芯原型验证助力香山RISC-V处理器迭代加速

新思科技功能安全验证解决方案助力RISC-V处理器IP通过ASIL D认证

新思科技功能安全验证解决方案助力RISC-V处理器IP通过ASIL D认证

评论