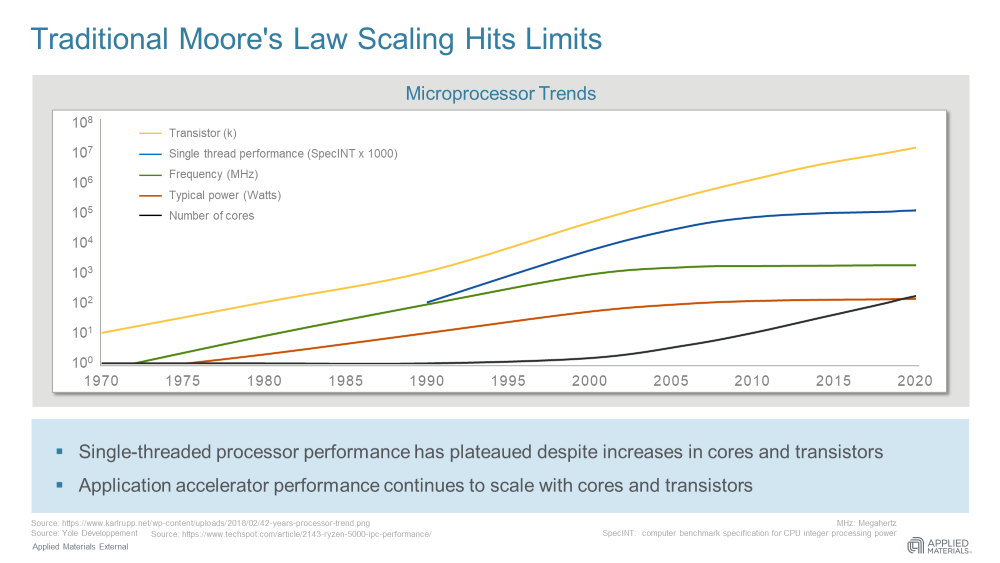

在摩尔定律奔向极限之际,IC制造大厂当前也仅存三家能玩上百亿美元的疯狂游戏,但当3纳米、1纳米终将成为物理极限,后摩尔定律时代(post-Moore‘s Law)降临,半导体业者不难发现,原来迷思于摩尔定律之中(Lost in Moore’s Law)仍有另一种解方,这个解方很可能存在于“小芯片”(Chiplet)之中。虽说“小”野心却不小,很可能带给从上游IC设计、EDA Tools、制造工艺、先进封测等各个产业链环节颠覆式的改变。

曾发起成立台积电后段封测部门的蒋尚义,如今来到武汉,率领武汉弘芯,他也看好此一方向,愿扮演推手角色,从这个小芯片系统变革出发,开展宏愿,从系统芯片打破芯片之间的籓篱,为摩尔定律之外寻找另一种解方。

话说“小芯片”撼动力“一点不小”

2017年美国国防部先进计划署(DARPA)推动的电子产业振兴计划(ERI)针对后摩尔定律(Post-Moore‘s-law)时代新材料、架构与设计流程,其中一个课题就是小芯片(Chiplet)。这也让小芯片的撼动力与影响力正式浮现在世人眼前,备受关注。

在美国早期的Chiplet项目中,有企业如英特尔、Northrop、Micorss等,还有模块芯片开发企业和高校如Ferric、Jariet、美光、Synopsys和密西根大学,以及EDA工具开发企业和高校如Candence和佐治亚理工等不同方参与。

简单来说,Chiplet小芯片,从系统端出发,先将复杂功能进行分解,然后开发出多种具有单一特定功能,可相互进行模块化组装的“小芯片”(Chiplet),如实现数据存储、计算、信号处理、数据流管理等功能,并最终以此为基础,建立一个“小芯片”的芯片网络(未来的电脑系统可能只包含一个CPU芯片和几个GPU,这些GPU都连接到这个Chiplet芯片上,形成芯片网络)。

做成Chiplet模式,需要构建一个生态系统,需要有一个丰富的模块芯片库(Die Bank或者KGD;known Good Die Bank)可供选择,集成者根据需求设计芯片架构,自由选择模块芯片并由制造商进行制造和封装。

这与传统IC制造流程不同的是,集成者不仅是购买IP,而是采购满足整体芯片架构的、即插即用的Die,这样的Die在工艺上不受其他模块的约束,工艺选择灵活,可以是逻辑的芯片,也可以是模拟芯片。

理论上讲,这种技术有助于IC制造客户的交货周期缩短,并以较低成本、较快周期实现芯片交付,但是生态环境能否成熟?以及芯片设计平台的完整与IP保护?以及后段封装测试等环节,皆需紧密配合到位。

而这个理念与实践做法,与当前武汉弘芯想做的系统芯片制造正好相契合。自7月初上任的弘芯CEO蒋尚义,向DIGITIMES谈到当前摩尔定律的发展逼近极限,与小芯片的“解方”这么分析,如今的晶圆制造精密度已经远远超过电路板100万倍以上,尽管10年前,硅片技术造就的芯片密度也好过电路板有10万倍。

也就是说,当一昧推进摩尔定律朝向物理极限发展,到达7纳米、5纳米、3纳米,尽管芯片密度不断提高,但是系统端仍滞后,“好也只限于好芯片”在电路板子上芯片与芯片间的传输速度与功率仍然受限于最宽松的传输标准,并没有发生全然性的改变。

这正如“水桶效应”,一只水桶能装多少水取决于它最短的那块木板。一只木桶想盛满水,必须每块木板都一样平齐且无破损,如果这只桶的木板中有一块不齐或者某块木板下面有破洞,这只桶就无法盛满水。如今从系统端,必须解决从芯片与芯片之间解决补好系统整合的“短板”,而非单只是单一芯片追求极限工艺的推进而已。

通过先进封装,能将小芯片统合到一起,这或许,可以解决当前分散在电路板上各芯片单元各自为政,通过一个界面标准以较低的功耗与功率进行芯片单元间的传输沟通,形成一个系统“小宇宙”。

而这也特别适用在物联网等多元与低功耗的应用领域,也是弘芯所最看好的应用市场。

蒋尚义对DIGITIMES表示,如今的电路板线宽约近50微米,从晶圆制造的角度来说,标准非常宽松,传输之间所耗的功耗与性能的提升空间还非常大,不论从性能还是功耗的角度来说大大影响了I/O传输效率,这方面,需要小芯片有机会重新制定一个更加严谨的I/O标准,而非传统在电路板上的宽泛标准。这也将是小芯片的竞争力之源,将标准制定下来,将功耗与能效最佳化,尽管看似很容易,系统小芯片统合难度非常高,“小归小,难度大”复杂度远超过行业内的想象。

蒋尚义指出,美国DARPA推动的电子产业振兴计划(ERI)推动小芯片,开始启动主导标准,也建议国内建立本土一套自己的标准,促进中国实现自己的标准,也是他现在正乐意推动的事。

武汉弘芯愿扮推手 推动Chiplet制定国内标准

蒋尚义分析,IoT物联网应用领域多元,小芯片内能够涵盖的芯片也相对地广,从A2D、D2A等能将不同芯片利用先进封装整合到一起,他自十年前就看到摩尔定律将逼近物理极限,看准先进封装将会是“解方”之一。他当时向当时台积电董事长张忠谋建议发展先进封装,并由底下关键人物余振华,带领“整合连结与封装”部门。

蒋尚义回忆,当时向张忠谋提案,发展先进封装说未来先进封测,张忠谋考虑仅一个小时,慨然答应,承诺增加400名研发团队成员,投资了1亿美元,“张大帅听了我报告后,仅用了一个小时考虑,决策还是非常果决!”蒋尚义对DIGITIMES回忆道。

经过一年研发投入,当时台积电自研先进封装的量仍相当少,客户接受度也不并不很高,蒋尚义说当时险些“成了一个笑话”,于是他亲自拜访客户寻找问题点所在。

一位客户告诉他,如果台积电能做到芯片在一平方厘米内售价1美分以下甚至价钱更低就可以接受,原来当时台积电做出的成本是7美分,已超过客户售价,客户承担不起,蒋尚义说,“从客户口中,我上了宝贵的一课,即使你做出的芯片再好,但要价钱更低,即便性能维持不变,客户也才会想要!”

如今,台积电的先进封装从CoWos发力已走到InFo再到SoIC,台积电封装芯片历经十年余,已成为年营收上30亿美元的大生意。

而眼见下一步chiplet将带动的产业变革,仍存在许多未知,chiplet在后摩尔定律时代将牵动IC设计、EDA Tools、IC制造与封测业何种变革?乃至于基板材料的改变?都将牵动行业变化的神经。蒋尚义说,过去他参与台积从CoWos发力走到InFo,下一个阶段是什么?正是他现正着手的进行式。

Chiplet带动的行业变革

近日在一场由芯联芯主办的圆桌讨论会议上,来自IP、设计服务与IC制造业大咖同台探讨了Chiplet对行业产生的变革与影响,并邀DIGITIMES与会。

从武汉弘芯蒋尚义的分析之中,他认为,从传统晶圆制造角度,如今已走到7纳米工艺,IC投片的成本至少5亿美元,出片时间长达4-5个月,这代表芯片业者至少需要卖20亿美元金额,卖到终端市场4亿颗芯片以上才有可能回收高昂的设计成本。放眼除了,智能手机芯片此一巨量市场,并非所有芯片玩家都能进入门槛。

反观IoT市场百花齐放,应用多元,不必盲目追求摩尔定律微缩,靠着小芯片die Bank选取需要的芯片组合与IP硅智财。以一家传感器IC公司只需要核心20位研发工程师为例,不必增加额外的30名工程师处理A2D, D2A与存储器等芯片架构的问题,这就足以走向Design-Lite轻简化。

一家公司可节省30名人力,不需要等待4-5个月繁复的制造过程,通过先进封装,很可能一周至一个月就能交付,节省设计时间资源成本,加快了交期与芯片进入市场的时间,简单直白“Time is Money”。

芯联芯首席运营官(COO)石克强则也认为,摩尔定律已走到尽头之际,Chiplet发展或许连摩尔仍在世,也是他意料不到的,这另一途径可说更好、更快、更便宜的让芯片不再受制于线宽与传输速度。

从设计服务的环节来讲,如何建立起当中的生态环境与伙伴关系,扩大Die Bank并且建立标准这也都是至关重要的事。

Wave Computing首席执行官Art Swift也认为,IP将为Chiplet小芯片添砖加瓦(building block),扮演重要的构成要素。

而从系统层面来说,每颗Die都需要确认良品率也就是KGD(Known Good Die),因为只要有任何一个Die有瑕疵整个系统等同于报废,损失将非常巨大。芯联芯首席执行官(CEO)何薇玲也强调,所谓的“GIGO”规则,就是“Garbage in, Garbage out”千万不要无用地输出输入,在系统芯片中,一方面必须慎选IP智财,同时确保IP智财没有专利侵权问题,确保拥有完整的IP保护,否则后果不堪设想,产品能否顺利问世将打问号。

芯联芯目前拥有MIPS架构全球销售权、中国与港澳地区独家经营权,从IP的观点切入,何薇玲对DIGITIMES表示,成熟CPU架构正是Chiplet的核心,能让系统运作得更稳当规律、更省能耗,IP成熟度与来源正当性往往是影响产品能否顺利上市,能不能最终打下市场的关键。

她说“天下没有免费的餐,免费的往往才是最贵的”在IP领域,现在各界都在谈“开源”,尤其中国市场“开源的春天来了”,但是,开源并不见得全然是免费,只是从营运模式与收费模式上形式有所不同,而这更需要生态共同的认可与携手推进。目前芯联芯落地是100%中资,以市场领先的价格优势,持续推进新、老客户在CPU 发展道路上前行。

或许,正当红的Chiplet小芯片,芯片连芯片,也是芯联芯期待一波绝佳机会的到来。

-

芯片

+关注

关注

447文章

47781浏览量

409086 -

半导体

+关注

关注

328文章

24501浏览量

202083 -

摩尔定律

+关注

关注

4文章

622浏览量

78520

原文标题:“Chiplet”小芯片大效应 牵动IC行业质量变 武汉弘芯愿扮标准制定推手

文章出处:【微信号:DIGITIMES,微信公众号:DIGITIMES】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔CEO基辛格:摩尔定律仍具生命力,且仍在推动创新

后摩尔定律时代,Chiplet落地进展和重点企业布局

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

超越摩尔定律,下一代芯片如何创新?

半导体行业产生深远影响的定律:摩尔定律!

什么是摩尔定律?

从系统芯片打破芯片之间的籓篱,为摩尔定律之外寻找另一种解方

从系统芯片打破芯片之间的籓篱,为摩尔定律之外寻找另一种解方

评论