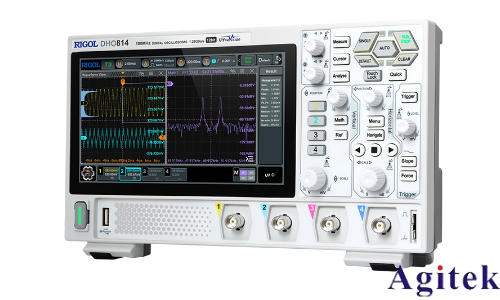

在电子测量领域,示波器作为信号分析的核心工具,其输入阻抗的合理设置直接影响测量结果的准确性。普源DHO824示波器凭借其高精度与多功能性,成为工程师调试复杂电路的首选设备。本文将深入解析该型号示波器的输入阻抗设置方法、应用场景及注意事项,帮助用户在高频信号测量与精密电路调试中实现最佳性能。

2026-01-04 17:33:41 349

349

74SSTUB32868A:28位到56位寄存器缓冲器的技术剖析 在DDR2内存模块的设计中,一款合适的寄存器缓冲器至关重要。今天,我们就来深入探讨德州仪器(Texas Instruments

2025-12-29 17:15:03 414

414 1.7 - 1.9V VDD电压运行的25位1:1或14位1:2可配置寄存器缓冲器。它的时钟和数据输入与JEDEC标准的SSTL_18兼容,控制输入为LVCMOS,输出则是经过优化的1.8V CMOS驱动器

2025-12-24 16:30:09 124

124 :1或14位1:2可配置的寄存器缓冲器,专为1.7 - 1.9V的VDD操作而设计。其所有时钟和数据输入都与JEDEC标准的SSTL_18兼容,控制输入为LVCMOS,输出则是经过优化的1.8V CMOS驱动器

2025-12-23 15:55:06 168

168 优化快速脉冲响应能力。示波器输入阻抗的选型直接决定三大核心指标,是保障测试有效性的关键前提: 测量精度保障 :传感器铭牌标注的灵敏度参数(如411型号0.1V/A),仅在示波器高阻抗输入(1MΩ+20pF并联)模式下有效;若接入50Ω负载,输出信号幅

2025-12-22 13:54:19 124

124

产品唯一身份标识(UID)寄存器(80bit)

UID寄存器存储了芯片的唯一身份标识符,UID在芯片生产时写入,用户无法修改。UID 寄存器支持以单字节 / 半字 / 全字等方式读取,然后使用自定义

2025-12-05 06:28:37

nRF54L15使用UICR寄存器保存数据 本文章主要是讲解如何使用nRF54L15的UICR寄存器保存一些基础数据 一、UICR寄存器的说明 UICR(用户信息配置寄存器)**是非易失性存储器

2025-11-27 17:09:27 1267

1267 NVIC_ICER 的32 个禁止位。将使能位置1,允许中断;将禁止位置1,禁止中断。

上文中NVIC 中断使能仅针对处理器NVIC 而言,外设的中断是否使能,还受相应外设的中断控制寄存器控制

2025-11-27 07:23:20

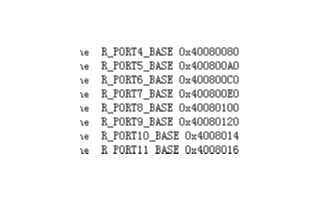

数据寄存器地址

define PIN_55

// 置位PA5引脚(输出高)GPIOA_ODR |= (1 << PIN_5);2、使用宏定义

使用宏定义可以提高代码

2025-11-24 07:22:24

学习汇编语言,首先必须了解两个知识点:寄存器和内存模型。

先来看寄存器。CPU 本身只负责运算,不负责储存数据。数据一般都储存在内存之中,CPU 要用的时候就去内存读写数据。

但是,CPU

2025-11-20 06:45:06

嵌入式开发看起来很复杂,但很多操作其实都离不开寄存器。寄存器就是MCU内部的存储单元,它们控制着处理器和外设的行为。熟悉这些寄存器,你就能更精确地操作硬件,提高开发效率,减少调试时间。今天,我们整理

2025-11-14 10:28:17 787

787

外围器件的通讯,这四条线是:串行时钟线(SCL)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线(CS)。当SPI工作时,在移位寄存器中的数据逐位从

2025-10-28 07:21:14

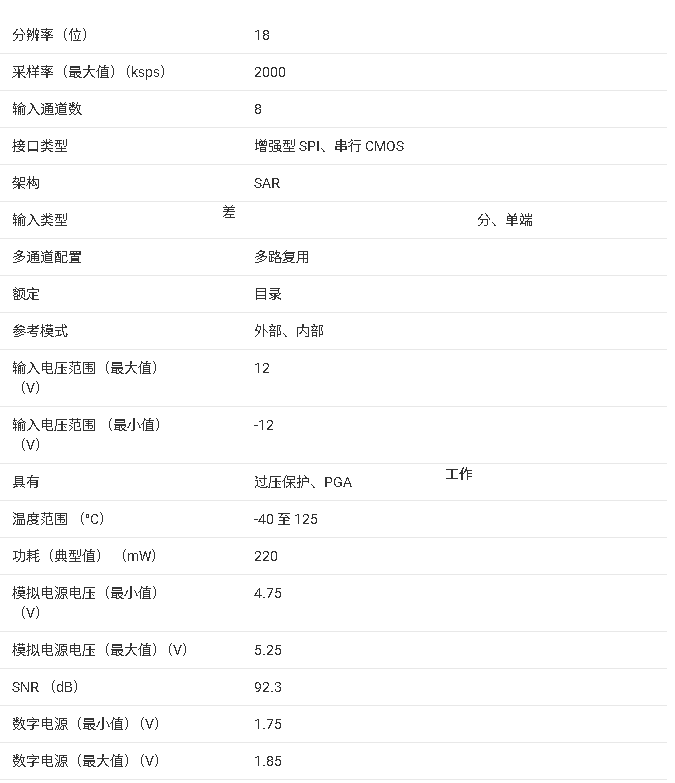

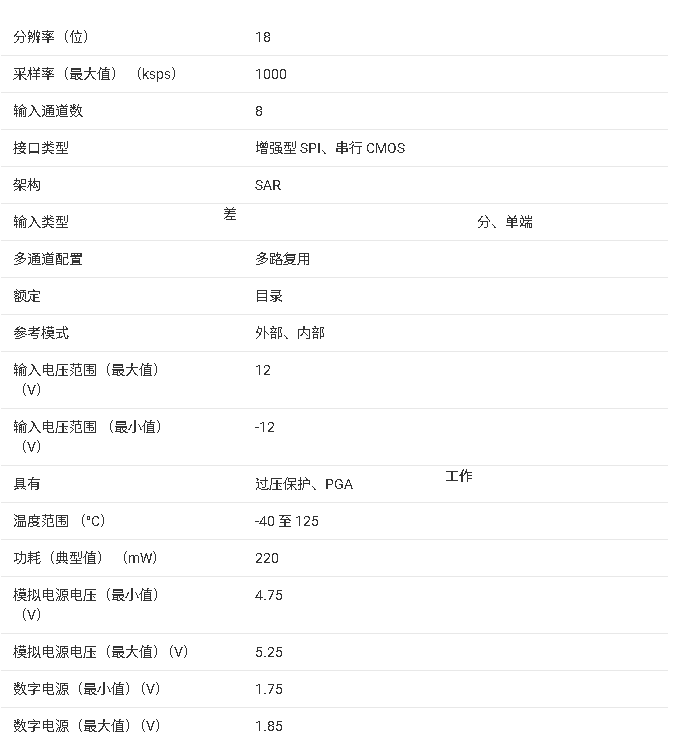

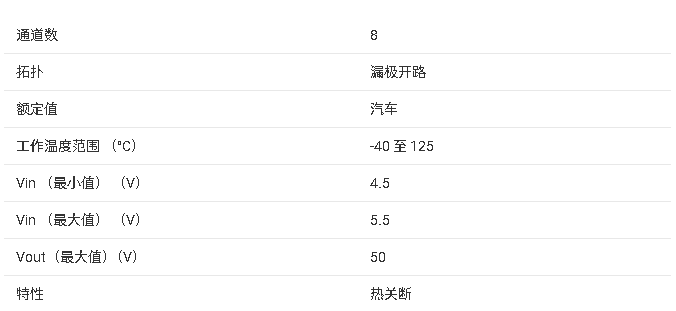

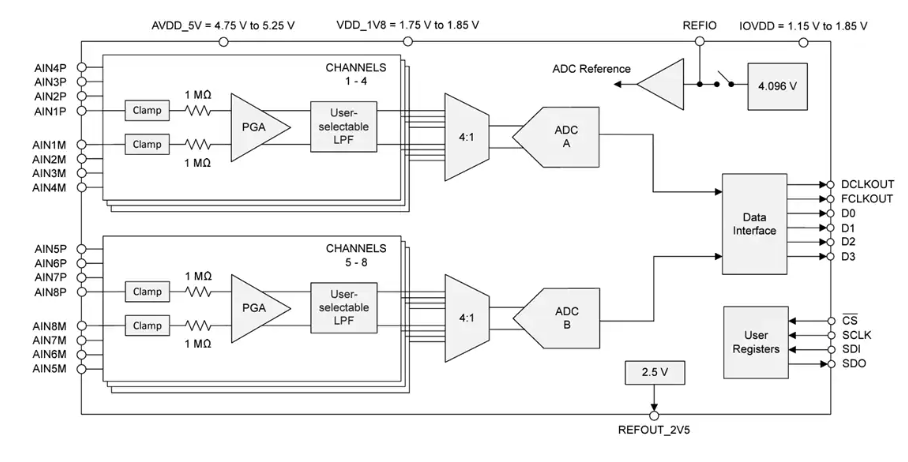

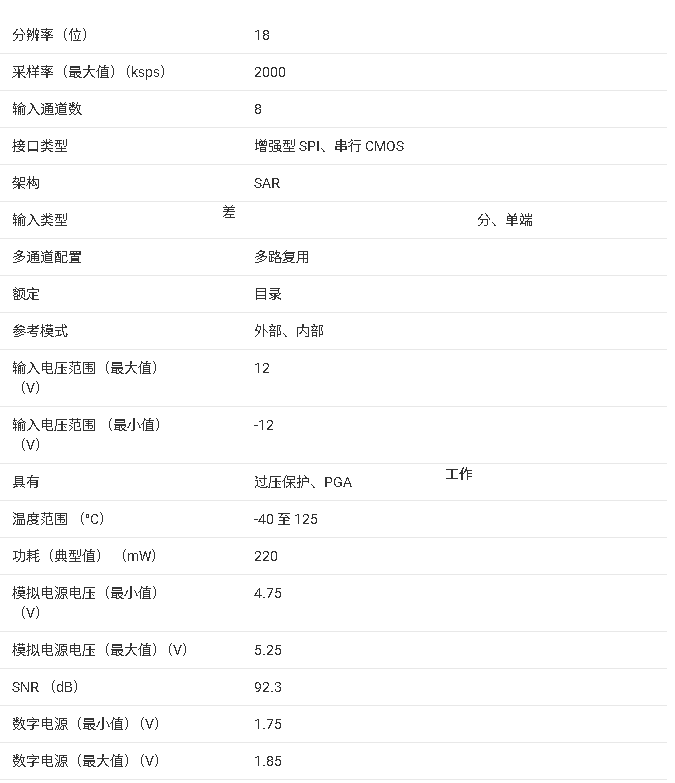

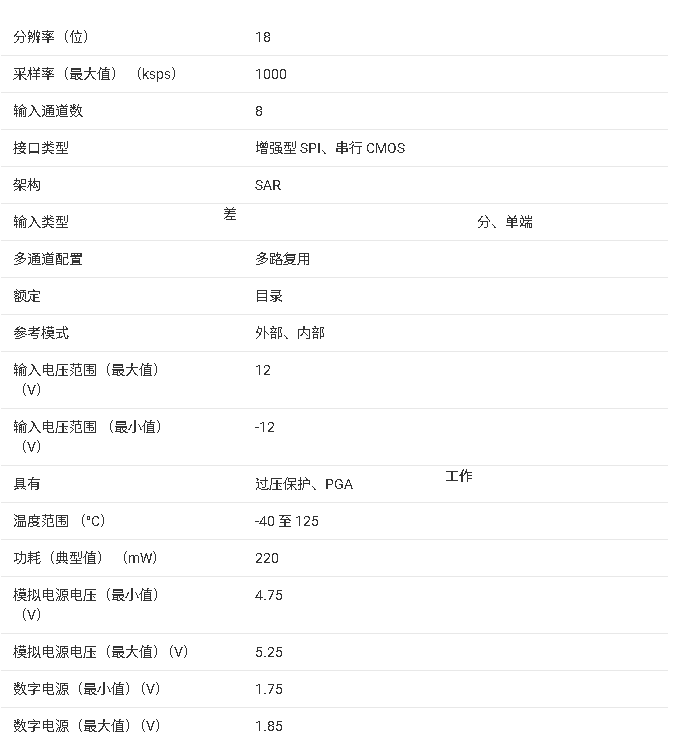

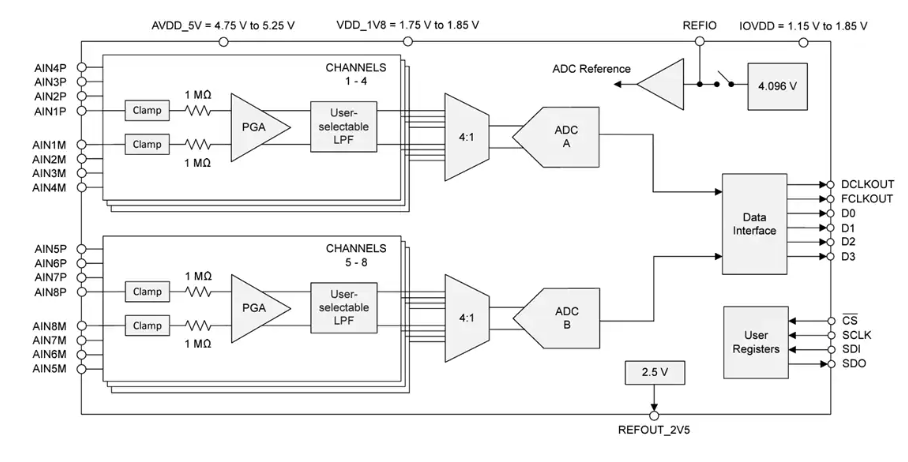

ADS981x是一款8通道数据采集(DAQ)系统,基于双通道、同步采样、18位逐次逼近寄存器(SAR)模数转换器(ADC)。ADS981x为每个通道提供完整的模拟前端,具有输入箝位保护电路、1M

2025-10-27 14:25:04 476

476

在写入信号输入的下一个时钟周期改写寄存器。

对于问题(4):从问题(3)的回答中可以知道,读信号和写信号是不会在同一个周期出现的,因此不需要考虑读写冲突的问题。

2. E203的 CSR 寄存器(控制状态

2025-10-24 13:25:02

ADS981x是一款8通道数据采集(DAQ)系统,基于双通道、同步采样、18位逐次逼近寄存器(SAR)模数转换器(ADC)。ADS981x为每个通道提供完整的模拟前端,具有输入箝位保护电路、1M

2025-10-24 10:06:00 566

566

寄存器)等。输出包括csr_ena(CSR读写请求是否有效)、csr_wr_en(CSR写入使能)、csr_rd_en(CSR读取使能)、csr_idx(CSR索引)等。

除此之外,该模块还实现了特殊

2025-10-24 10:01:56

:DMA寄存器的配置、读写模块和fifo。

这里主要分享对DMA寄存器配置的分析讨论。

寄存器配置

在开始传输前,DMA控制器接收CPU对于源地址,目的地址,搬运数据长度的配置信息,当这些寄存器信息更新后

2025-10-24 08:46:48

整数型寄存器,代码和注释如下:

// 定义 e203_exu_regfile 模块module e203_exu_regfile(// 定义读端口src1和src2的索引和数据输出端口input

2025-10-24 08:22:33

整数型寄存器,代码和注释如下:

// 定义 e203_exu_regfile 模块module e203_exu_regfile(// 定义读端口src1和src2的索引和数据输出端口input

2025-10-24 06:53:12

具体代码位于:

概述

CSR是RISC-V中的控制状态寄存器(Control and Status Registers),用于控制处理器的行为和状态。CSR类指令是RISC-V中的一类指令,用于

2025-10-24 06:08:16

,value2,…,value120)vtype:数据类型addr:变量起始地址,最大可以写120个连续寄存器value1:寄存器1的值value2:寄存器2的值……valu

2025-10-17 00:00:00 1222

1222

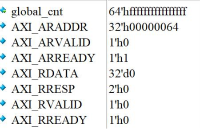

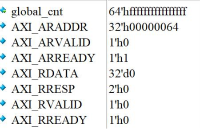

寄存器最大值为 64’hFFFFFFFFFFFFFFFF,到达最大值后一个时钟周期后翻转回 0, 在随机时刻使用 force 将寄存器赋值临近最大值, 当寄存器达到最大值后, 翻转回到 0, 读取数值为 0, 仿真行为符合设计预期.

2025-10-14 17:06:25 564

564

在待测设计中, 系统控制模块中的寄存器通过 AXI4-Lite 接口访问, 该接口与axi4_lite_agent 对应, 因此可以直接在测试用例中实现寄存器的读写操作。 对寄存器的测试需要考虑到

2025-09-30 10:01:20

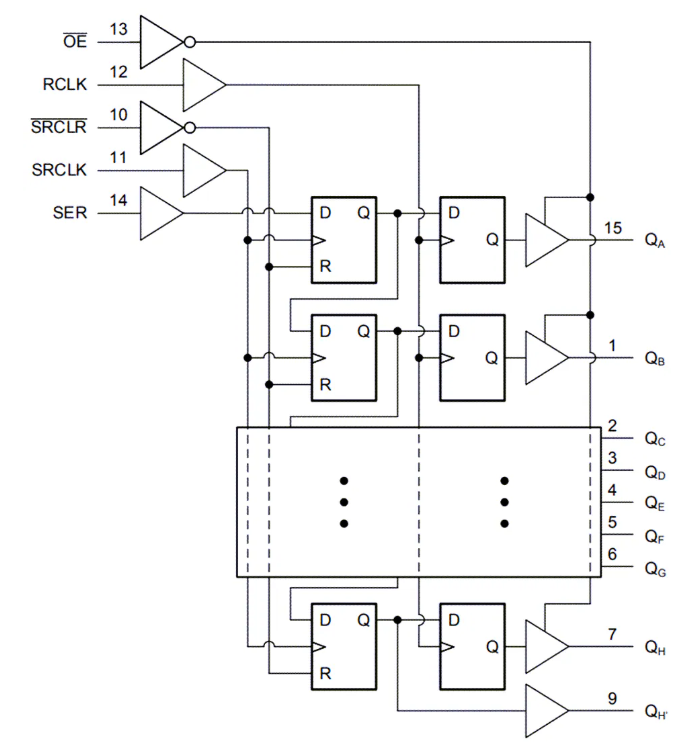

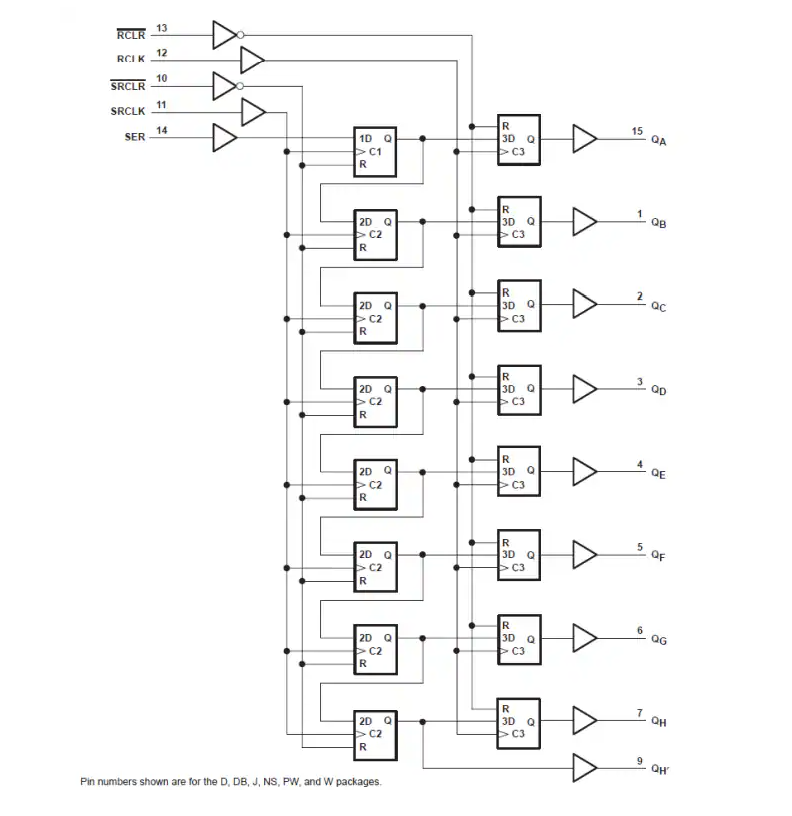

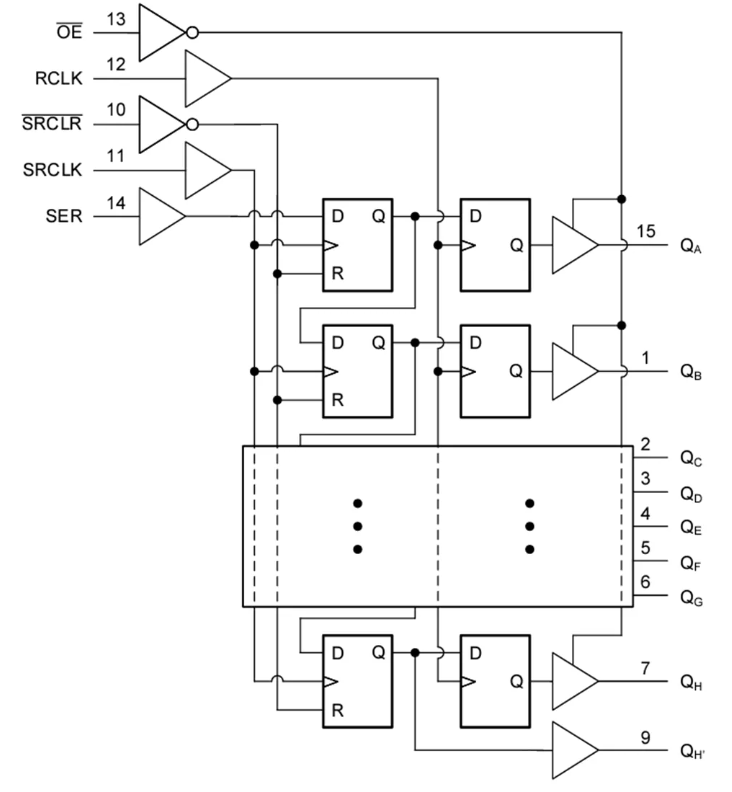

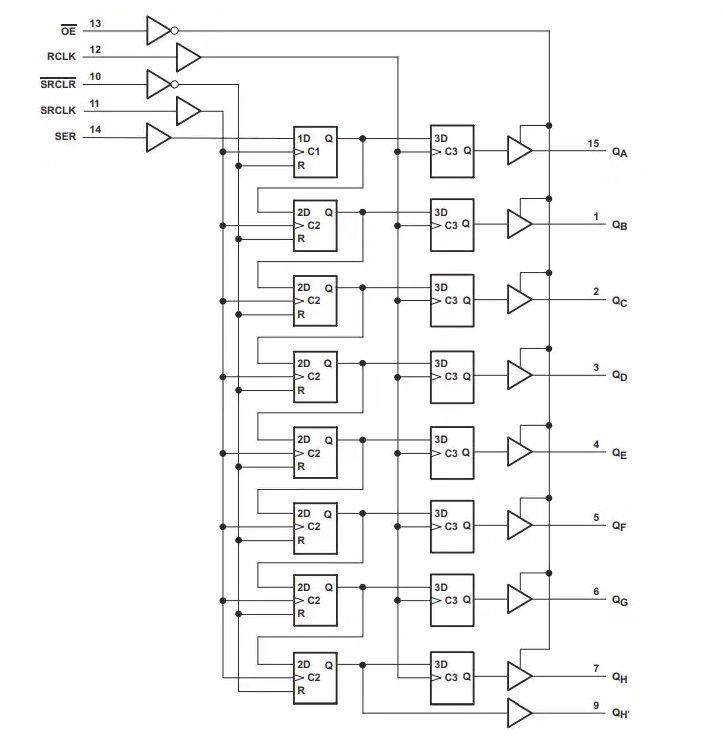

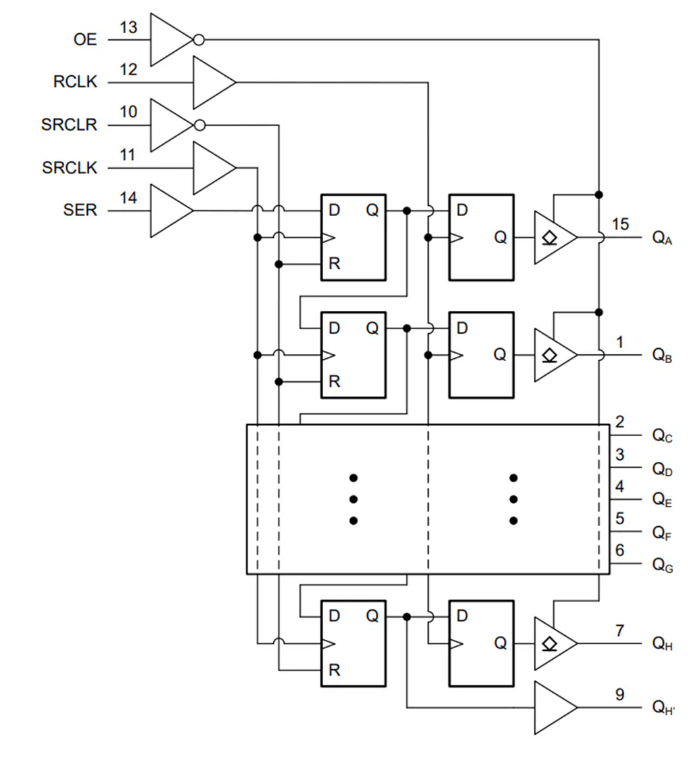

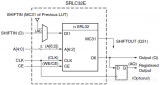

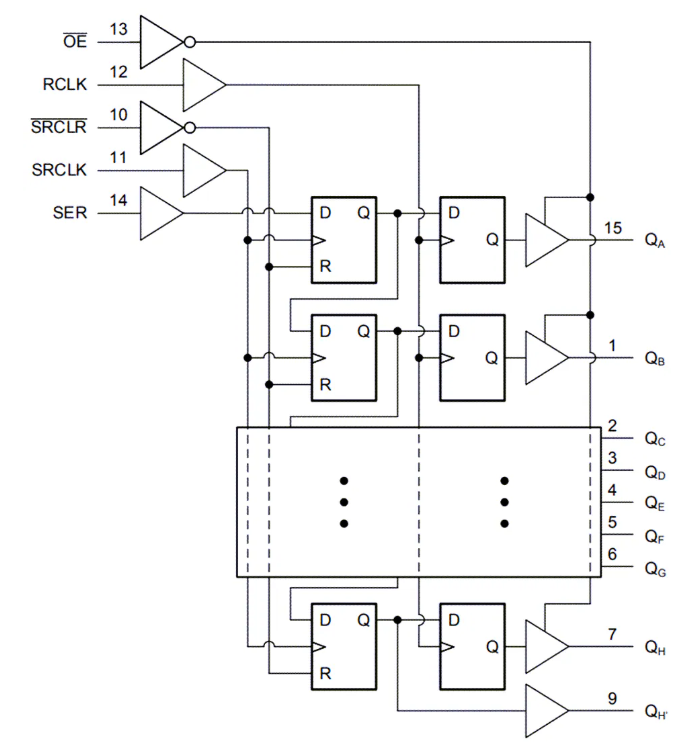

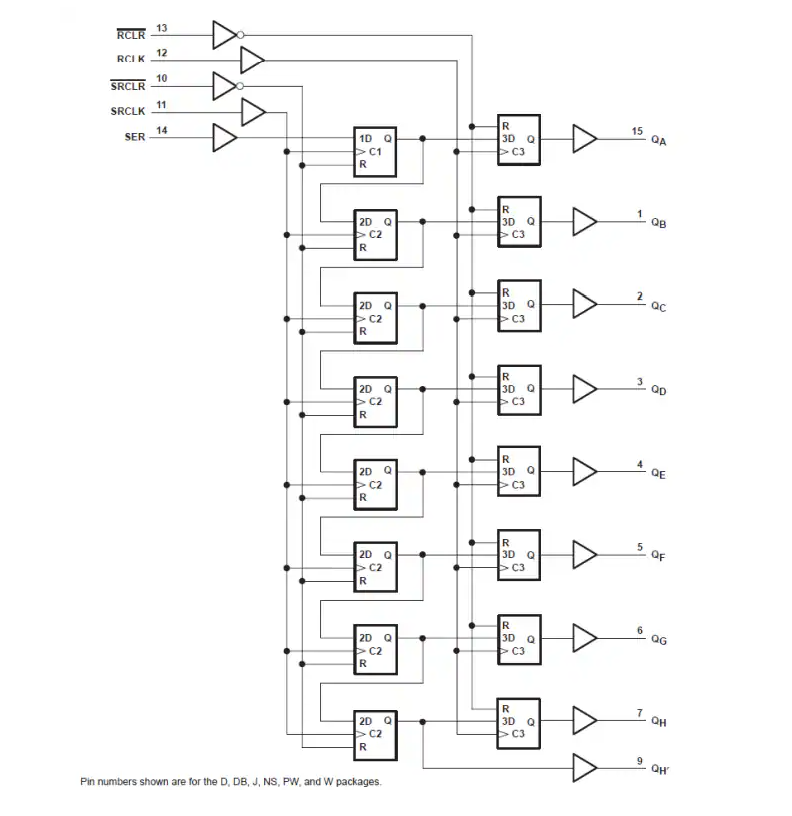

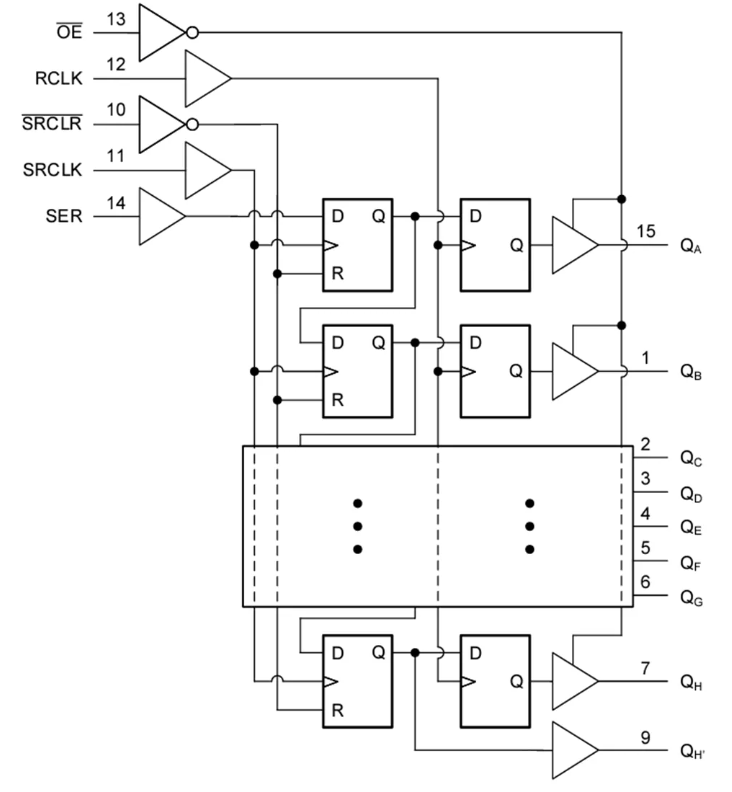

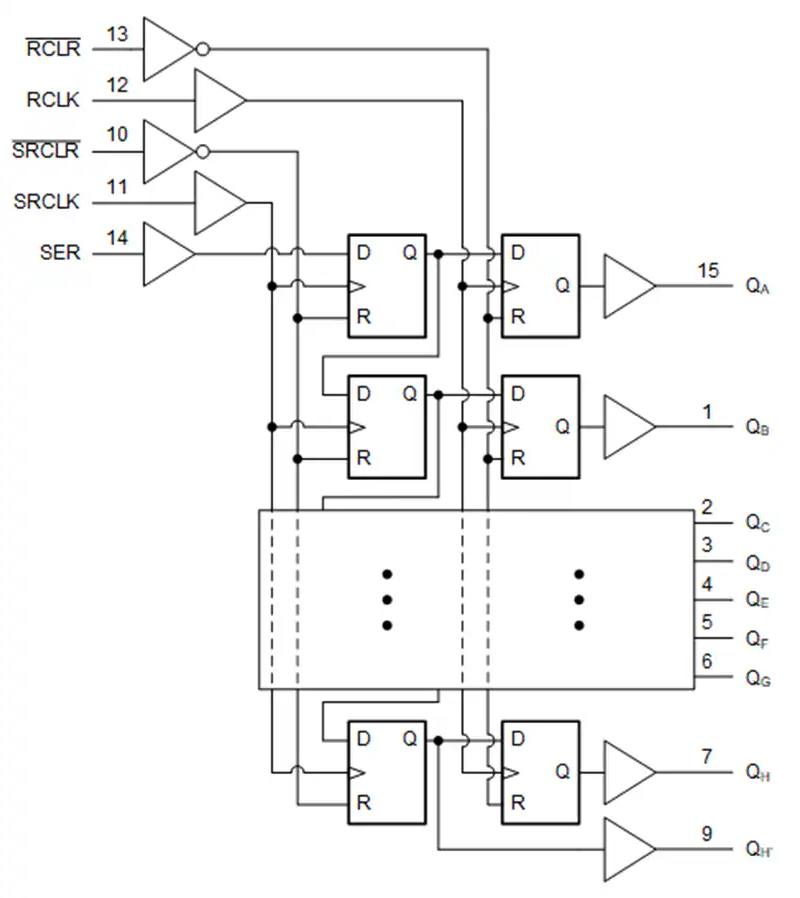

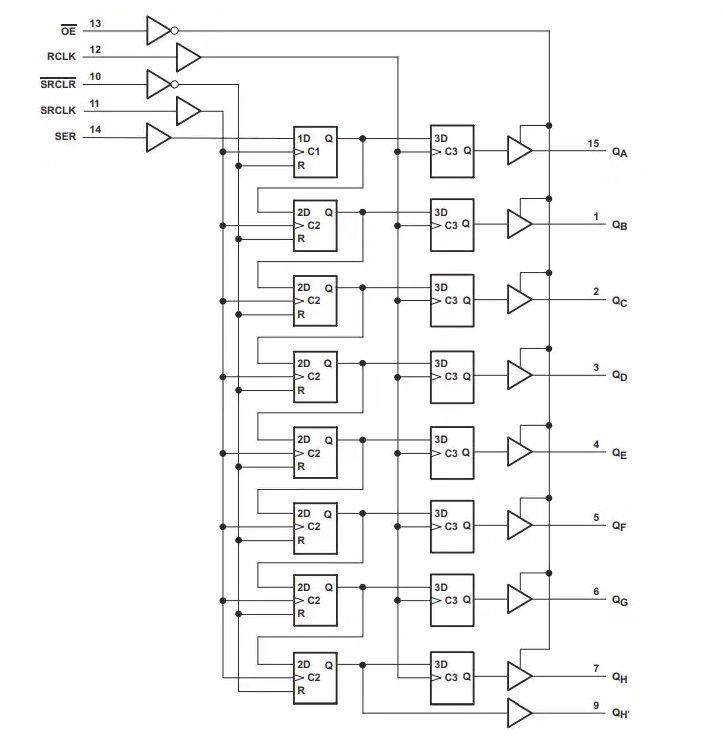

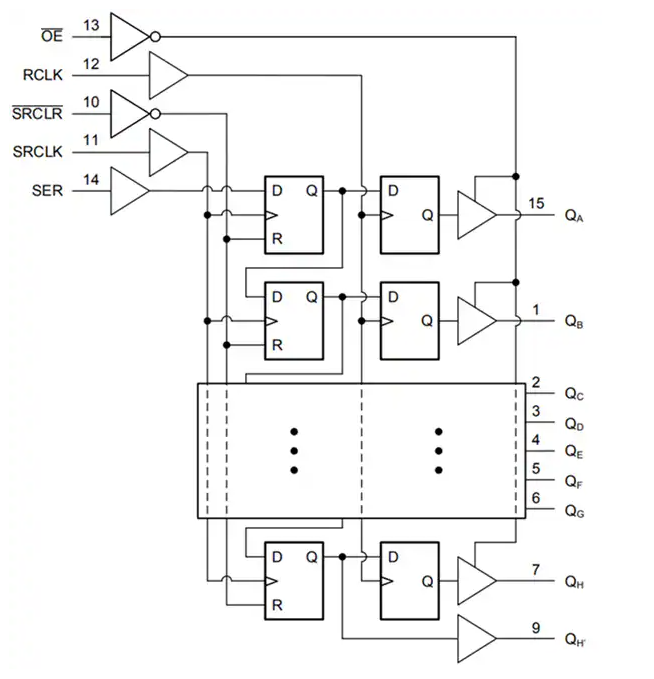

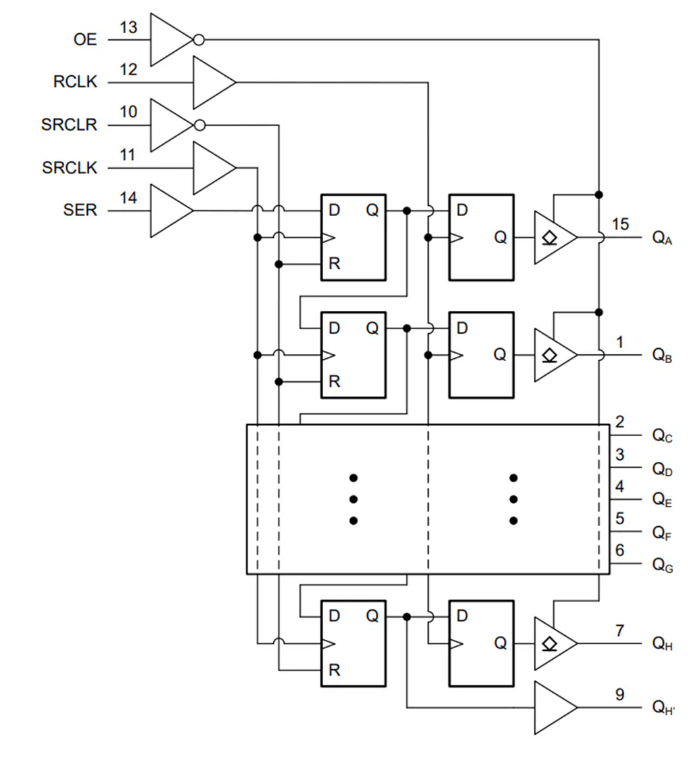

SN74LVC595A器件包含一个8位串行输入、并联输出移位寄存器,该寄存器为8位D型存储寄存器供电。存储寄存器具有并行的 3 态输出。为移位寄存器和存储寄存器提供了单独的时钟。移位寄存器具有直接

2025-09-28 15:09:48 1194

1194

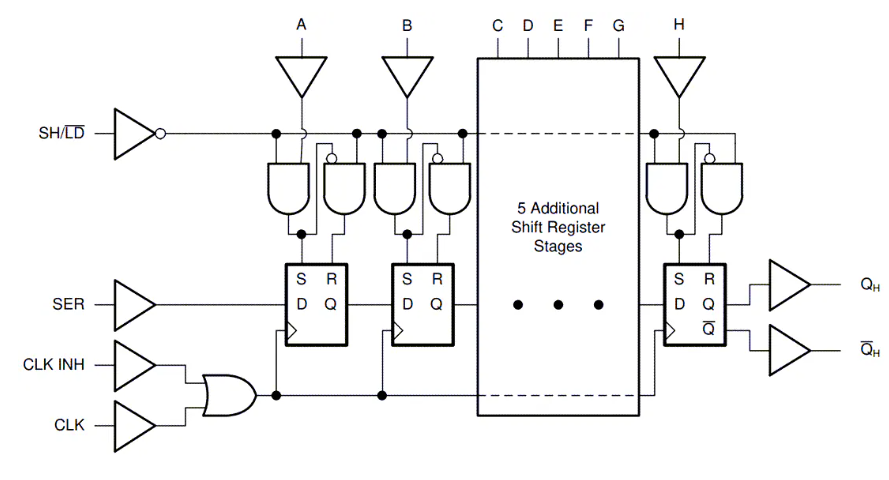

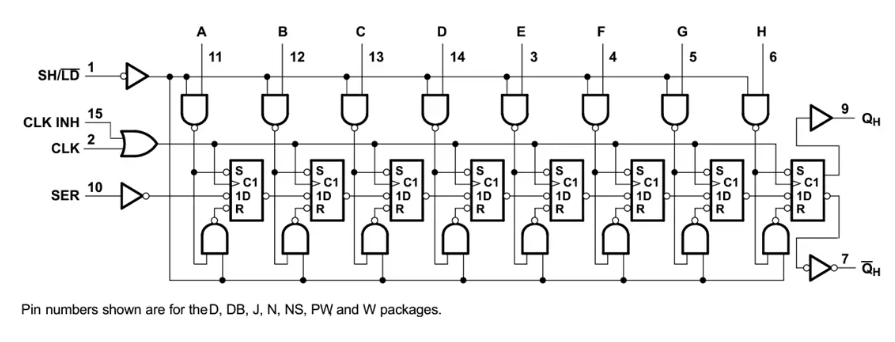

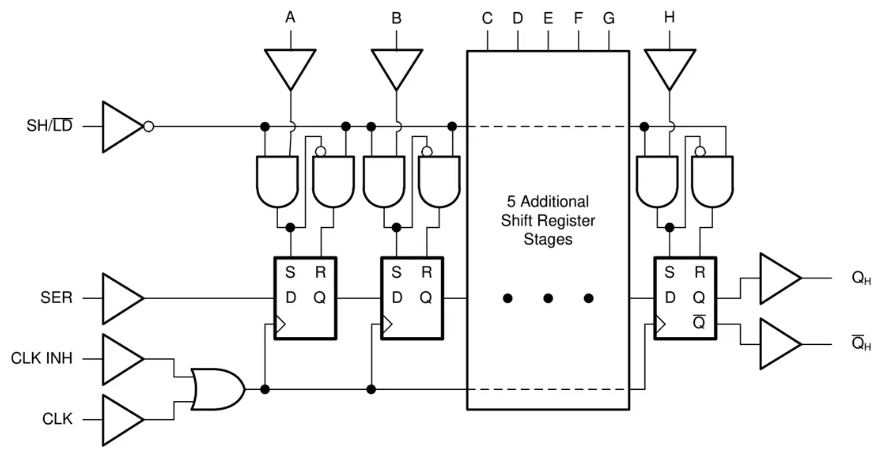

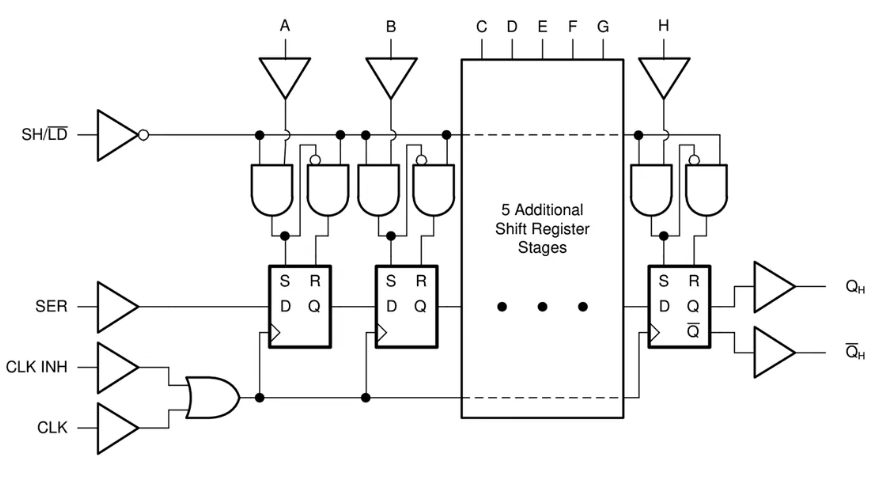

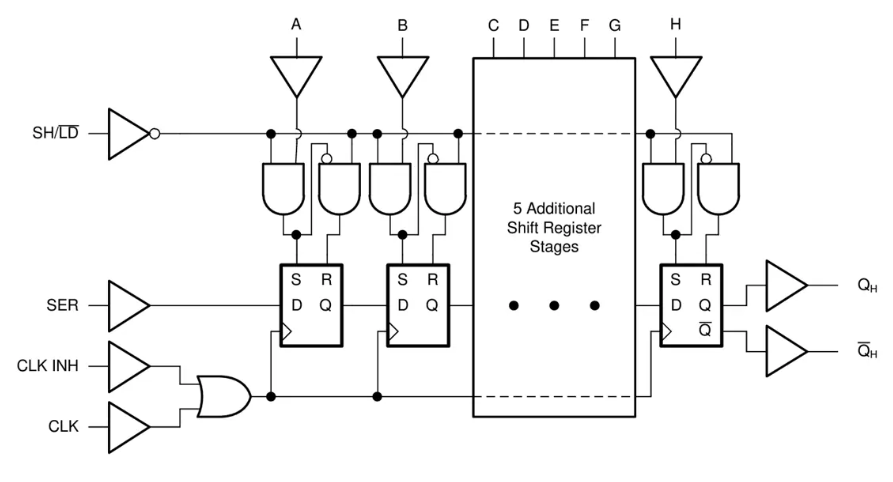

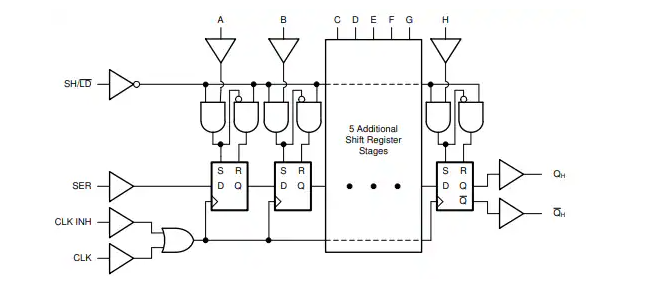

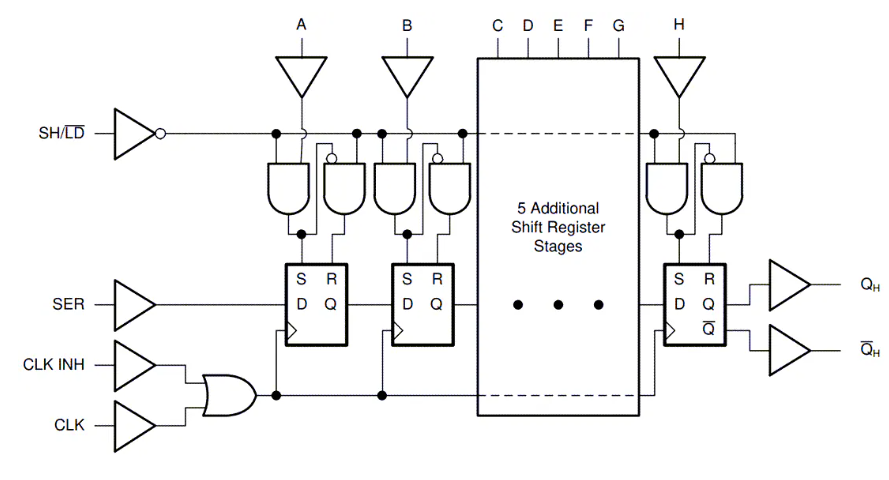

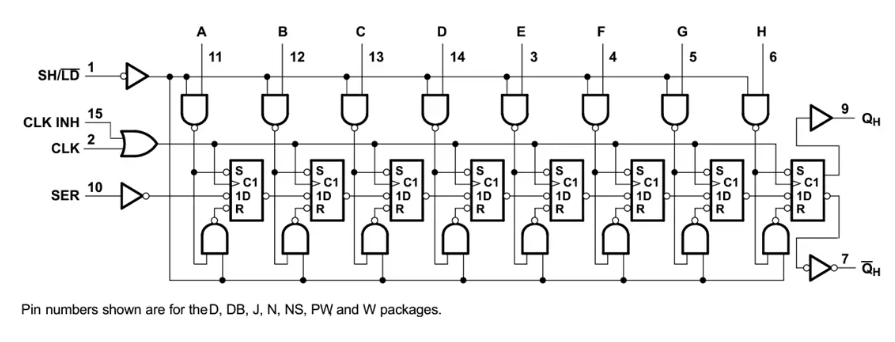

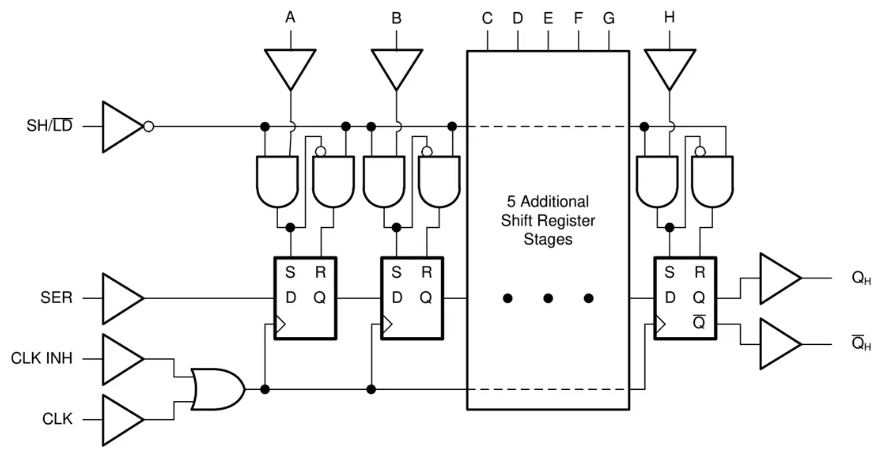

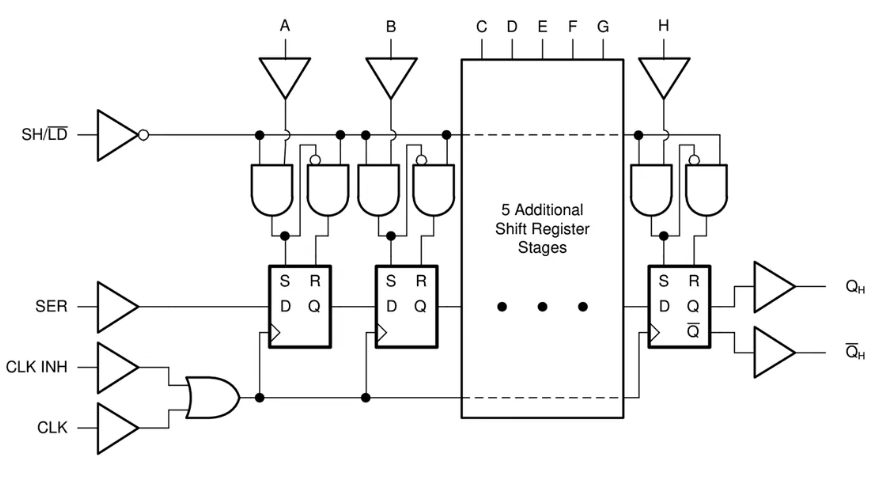

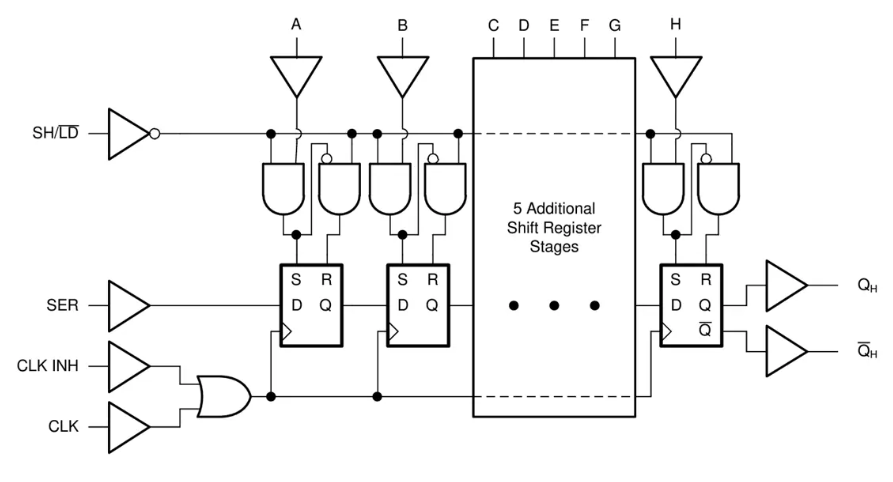

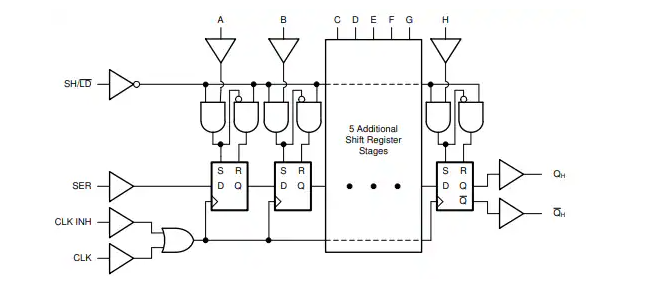

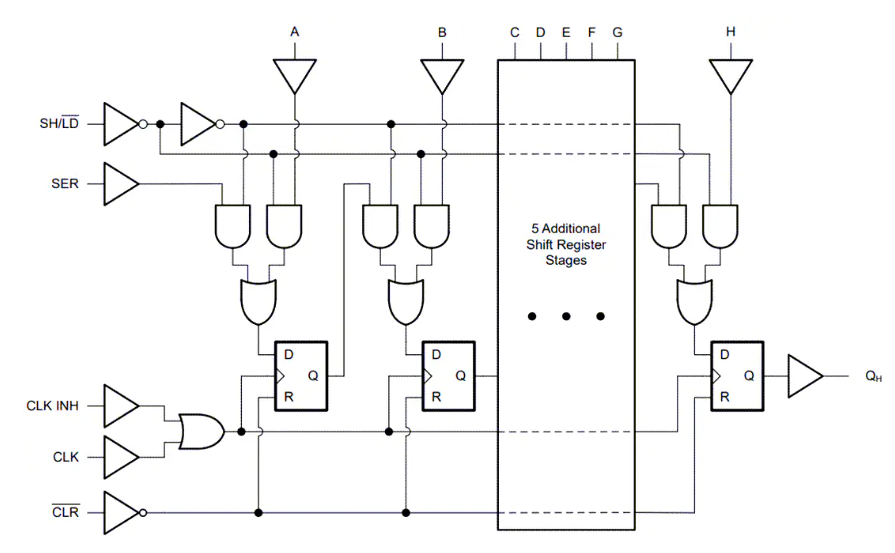

Texas Instruments SN74HCT165/SN74HCT165-Q1并联负载移位寄存器是一款并联或串联输入、串联输出8位移位寄存器。借助八个独立的直接数据 (A-H) 输入并行访问

2025-09-19 14:39:13 687

687

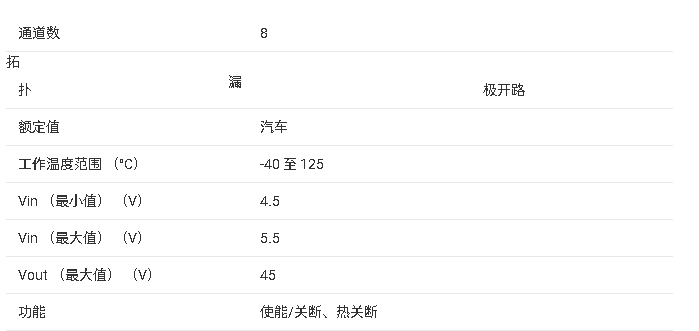

输出将置于高阻抗状态。内部寄存器数据和串行输出 (QH') 不受OE输入操作的影响。Texas Instruments SN74HCT595-Q1器件符合汽车应用类AEC-Q100认证。

2025-09-19 14:31:22 704

704

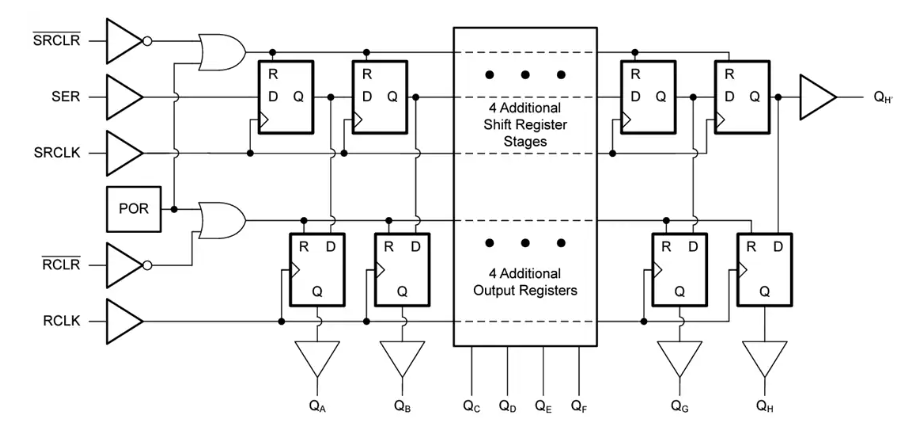

和存储寄存器传输。当移位寄存器清除 (SRCLR) 为高电平时,存储寄存器将数据传输到输出缓冲器。写入数据和读取数据仅在 RCK 较低时有效。当SRCLR为低电平时,输入移位寄存器被清除。

2025-09-09 11:10:07 787

787

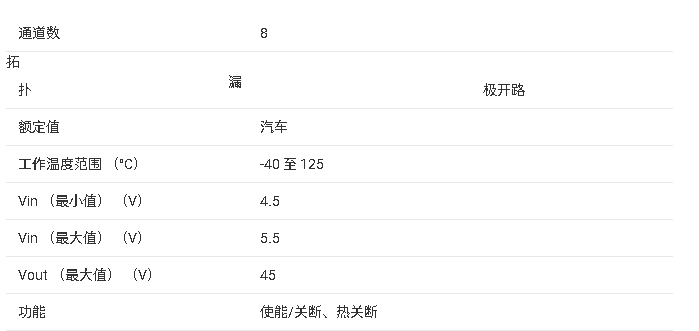

或高压负载。

该器件包含一个 8 位串行输入、并行输出移位寄存器,该寄存器为 8 位 D 型存储寄存器供电。数据分别通过移位寄存器时钟 (SRCK) 和寄存器时钟 (RCK) 上升沿的移位寄存器和存储寄存器传输。

2025-09-09 10:16:03 817

817

完整的模拟前端,并带有输入钳位保护电路。它还配有可编程增益放大器 (PGA)、1MΩ 输入阻抗和用户可选的带宽选项。高输入阻抗允许与变压器和传感器直接连接,从而无需外部驱动电路。ADS981x可接受最高达 ±12V共模电压的单极或双极输入。

2025-09-06 09:46:27 842

842

Texas Instruments SN74LV594A/SN74LV594A-Q1 8位并行输出串行移位寄存器设计采用2V至5.5V V~CC~ 运行。SN74LV594A-Q1符合汽车应用类

2025-09-02 09:42:58 710

710

如何设置高转换速率控制寄存器,将SPI频率提高到36 MHz而不引起波形失真?

2025-08-28 07:23:54

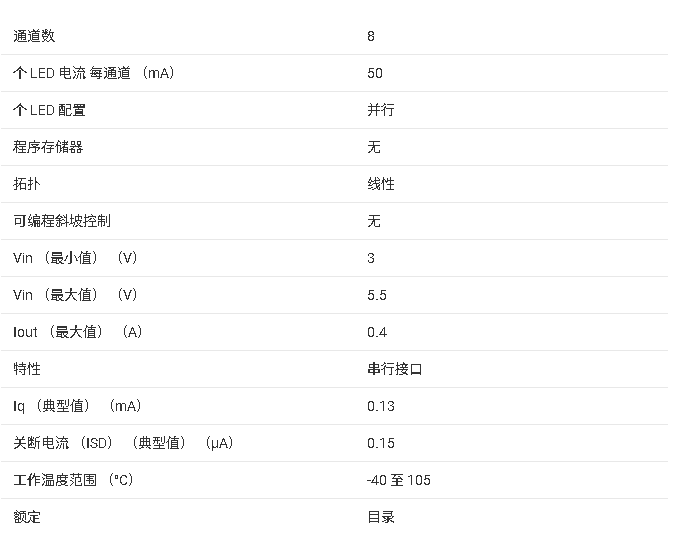

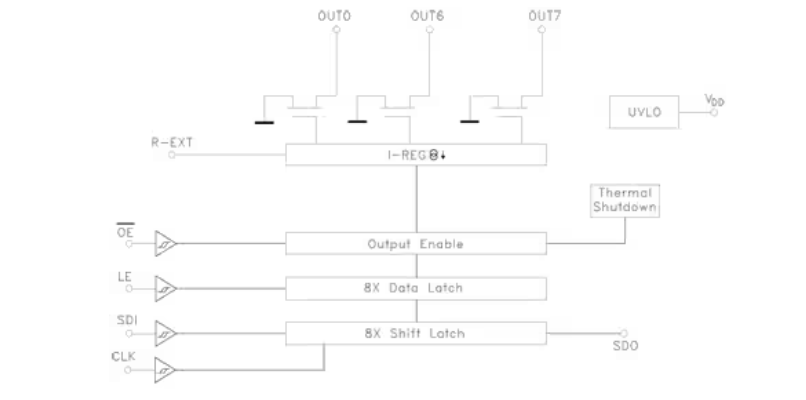

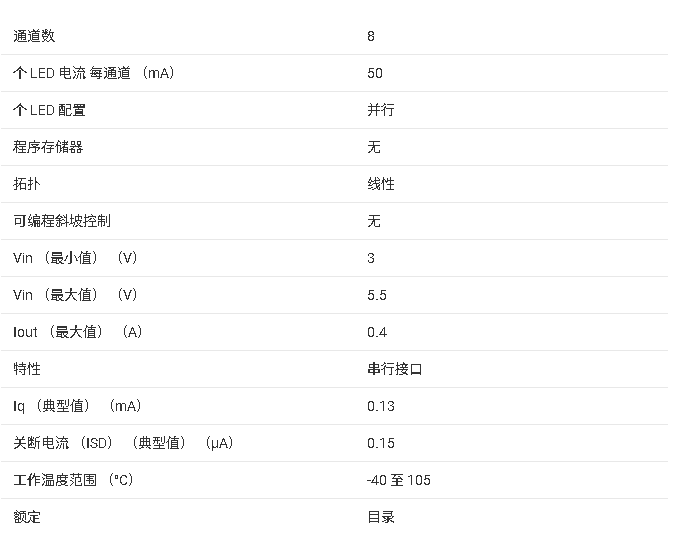

TLC6C598器件是单片、中压、低电流功率 8 位移位 寄存器设计用于需要相对中等负载功率的系统,例如 LED。

该器件包含一个 8 位串行输入并行输出移位寄存器,可为 8 位馈电 D型存储

2025-08-26 14:31:39 913

913

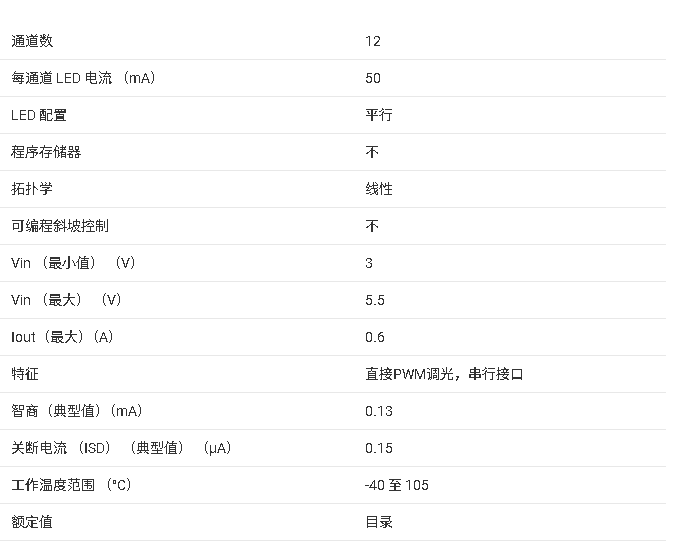

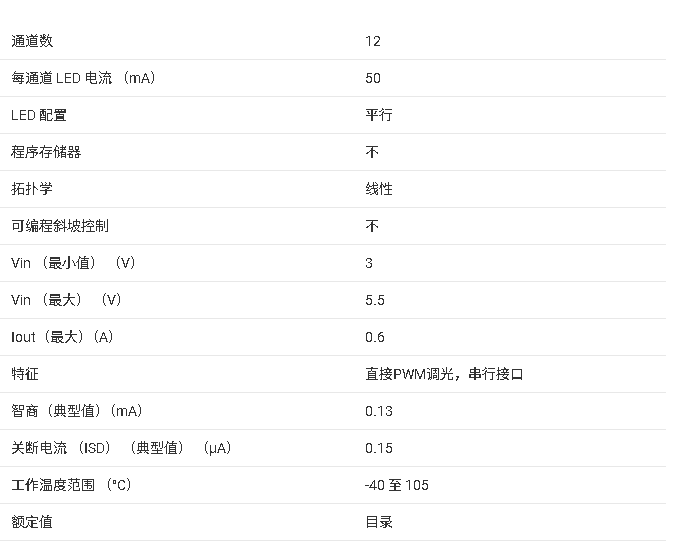

该TLC6C5912是一款单片、中压、低电流功率 12 位移位寄存器 设计用于需要相对中等负载功率的系统,例如 LED。

该器件包含一个 12 位串行输入并行输出移位寄存器,可为 12 位馈电

2025-08-26 14:16:16 867

867

如何设置高转换速率控制寄存器,将SPI频率提高到36 MHz而不引起波形失真

2025-08-21 07:33:01

移位寄存器和存储寄存器提供时钟。移位寄存器具有直接覆盖清除 (SRCLR) 输入、串行 (SER) 输入和用于级联的串行输出。当输出使能 (OE) 输入为高电平时,除Q~H~外,所有输出均处于高阻抗状态

2025-08-15 09:28:43 941

941

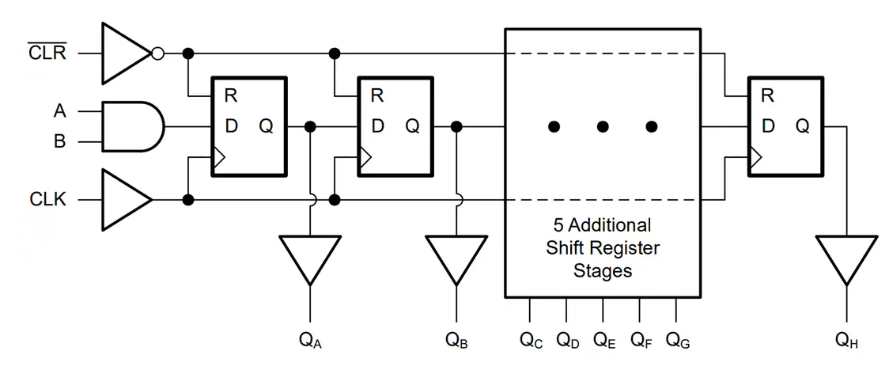

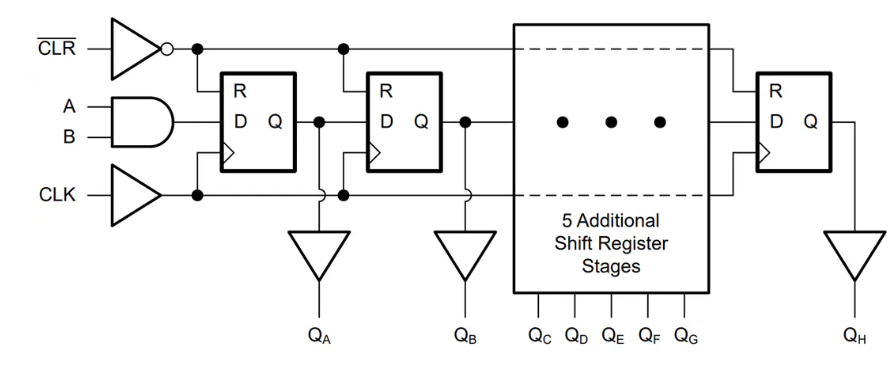

Texas Instruments SN74HC165/SN74HC165-Q1 8位并行负载移位寄存器是一种将数据移向串行( ~QH~ )输出的寄存器。通过八个单独的直接数据(A-H)输入提供

2025-08-12 14:24:20 973

973

Texas Instruments SN74AHC165/SN74AHC165-Q1串行输入/并行输出 (SIPO) 移位寄存器包含一个8位串行输入、并行输出移位寄存器。每个寄存器可将数据馈入一个8

2025-08-11 15:31:23 934

934

Texas Instruments SN74AHCT165/SN74AHCT165-Q1串行输入/并行输出 (SIPO) 移位寄存器包含一个8位串行输入、并行输出移位寄存器。每个寄存器可将数据馈入8

2025-08-11 14:55:14 938

938

Texas Instruments SN74LV8T165/SN74LV8T165-Q1并行加载8位移位寄存器是并行或串行输入、串行输出8位移位寄存器。这些器件有两种操作模式:加载数据和移位数据,由

2025-08-11 11:35:19 1363

1363

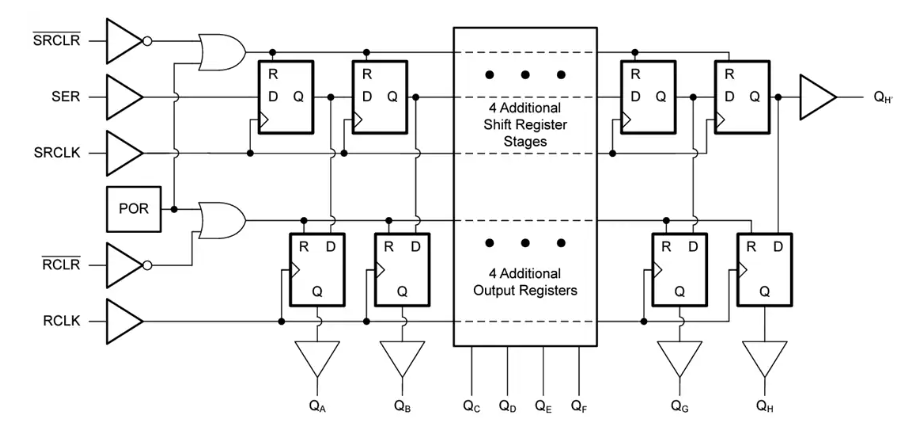

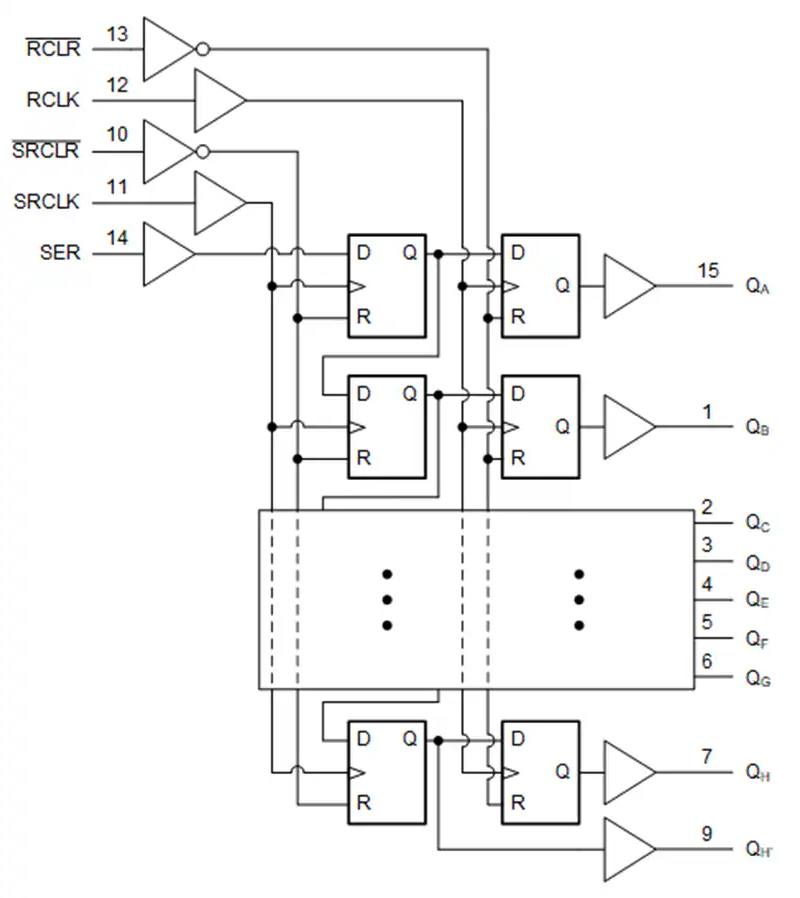

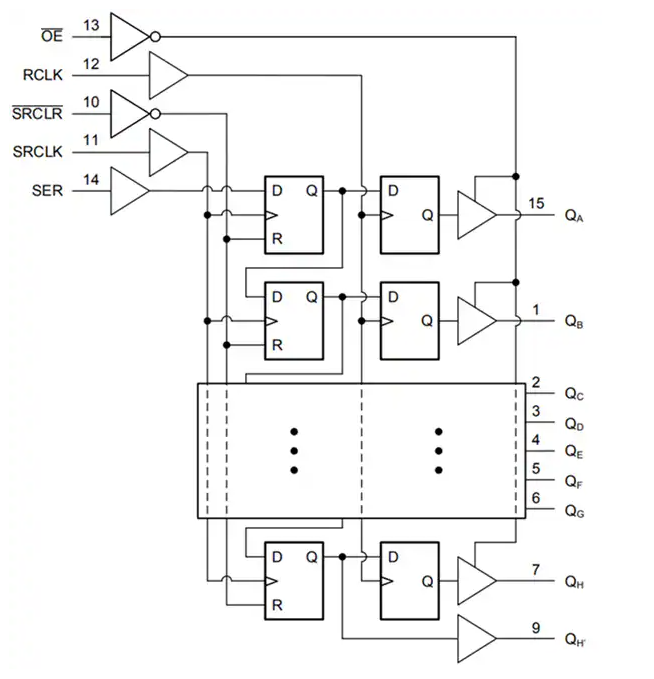

器件输出(QA至QH)。为移位寄存器和存储寄存器提供单独的时钟(SRCLK和RCLK)和直接覆盖清除(SRCLR和RCLR)输入,允许数据单独加载,而不会发送至输出。此外,内部移位寄存器的最后输出直接发送到输出QH &,提供了一种以菊花链形式连接多个移位寄存器的方法。

2025-08-03 10:56:37 876

876

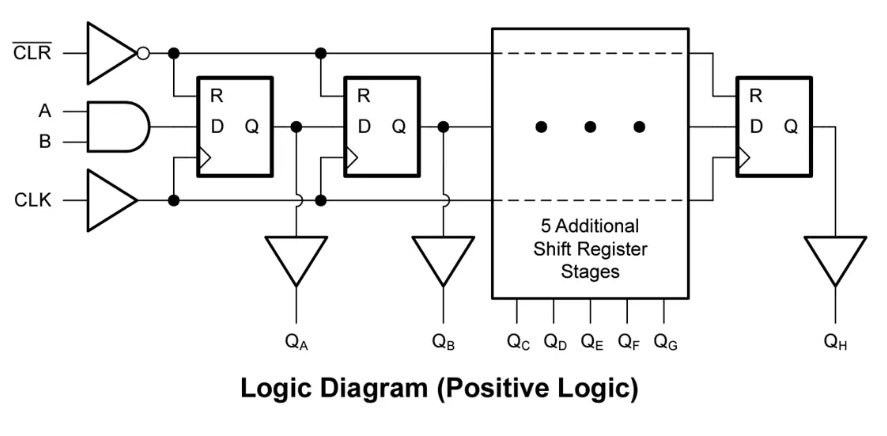

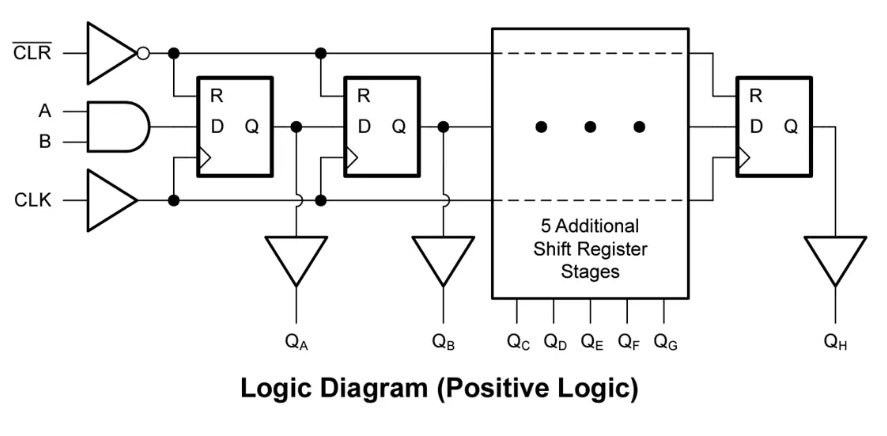

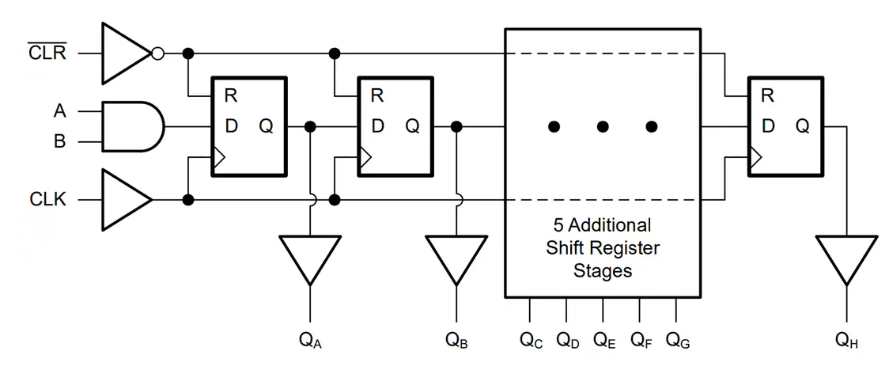

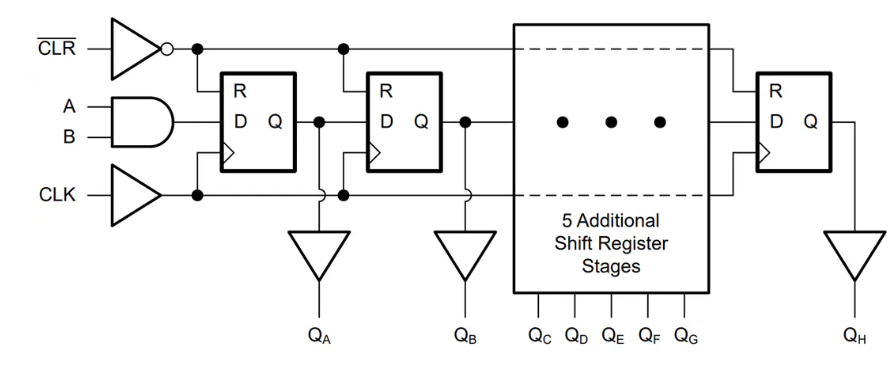

Texas Instruments SN74AHC164/SN74AHC164-Q1 8位移位寄存器具有AND门控串行输入和异步清零(CLR)输入。输出直接连接到内部移位寄存器,当数值移入寄存器

2025-08-01 15:33:34 847

847

Texas Instruments SN74AHCT594/SN74AHCT594-Q1 8位移位寄存器包含一个为8位D型存储寄存器提供数据的8位串行输入、并行输出移位寄存器。移位寄存器和存储寄存器

2025-08-01 15:16:13 1002

1002

Texas Instruments SN74AHC594/SN74AHC594-Q1 8位移位寄存器包含一个为8位D型存储寄存器提供数据的8位串行输入、并行输出(SIPO)移位寄存器。移位寄存器

2025-08-01 14:58:07 955

955 选择引脚将数据异步加载到设备。这些移位寄存器支持局部关断,具有反向驱动保护功能,3.3V时最大传播延迟时间为20ns。SN74LVC165A-Q1寄存器符合汽车应用类AEC-Q100认证。这些移位寄存器用于增加微控制器上的输入数量以及读板修改。

2025-07-29 10:58:32 569

569

Texas Instruments SN74AHC595/SN74AHC595-Q1计数器移位寄存器包含一个8位串行输入、并行输出移位寄存器,提供一个8位D类存储寄存器。存储寄存器具有并行3态输出

2025-07-28 16:51:48 676

676

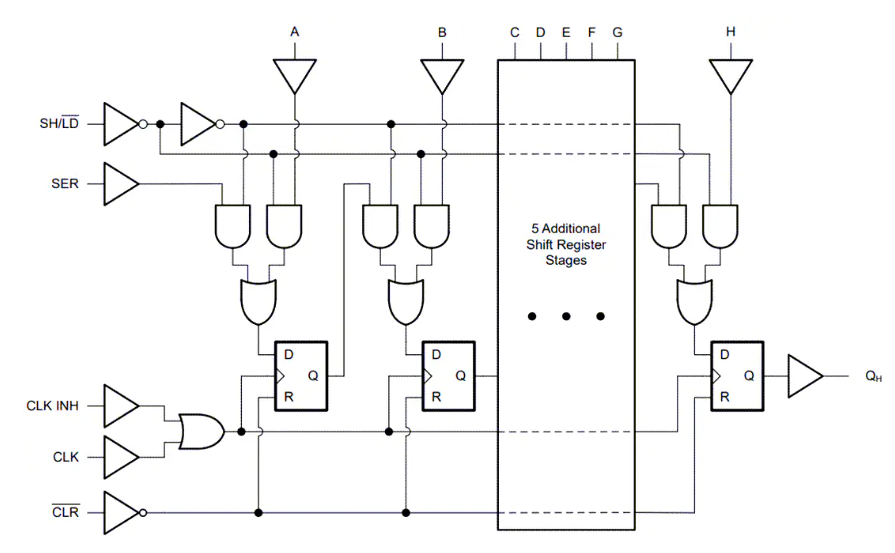

Texas Instruments SN74LVC166A 8位并行加载移位寄存器包含一个8位并行加载移位寄存器。数据通过移位或加载(SH/LD)选择和时钟(CLK)输入同步加载。Texas

2025-07-24 14:43:53 559

559

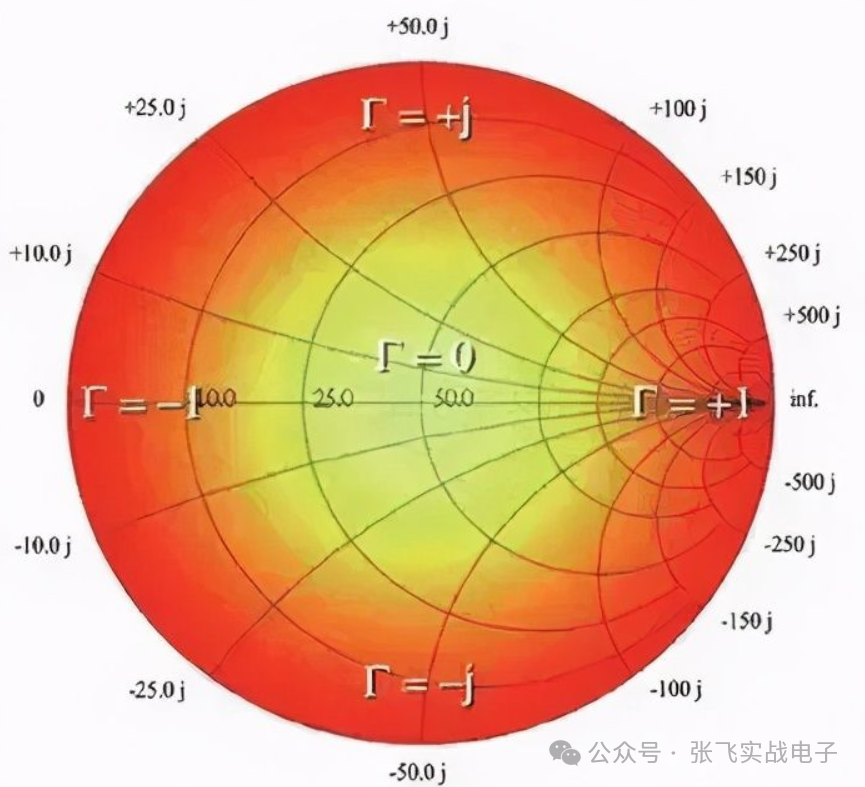

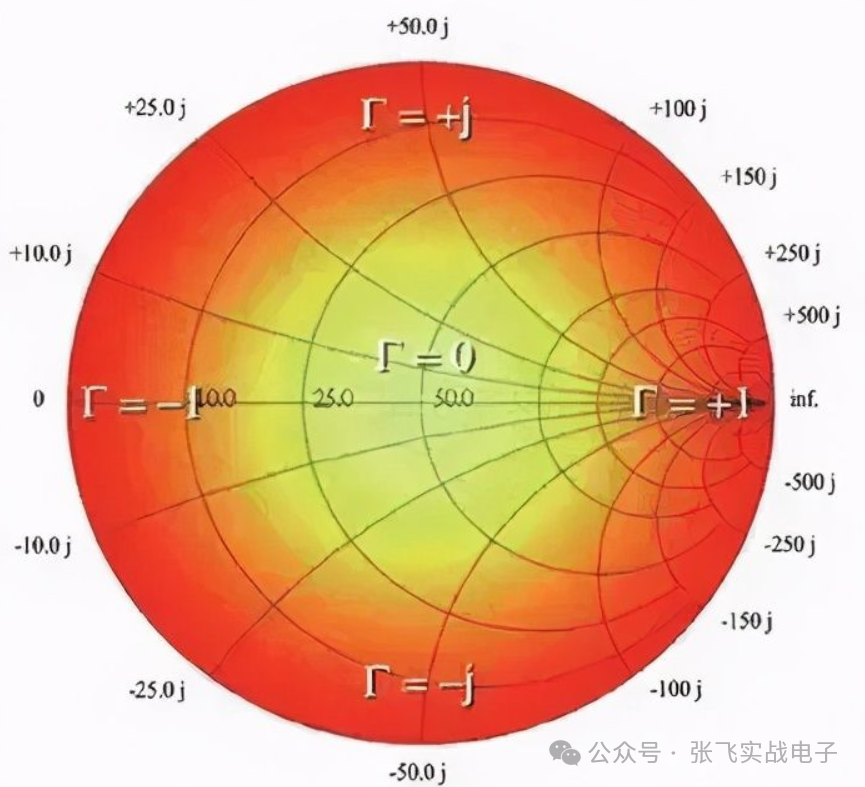

核心要点负阻抗变换器(NIC)是一种能在输入端模拟负阻抗的电路。负阻抗变换器应用广泛,涵盖模拟信号处理和控制系统等领域,可用于稳定或调整电路的输入阻抗。在将负阻抗变换器集成到印刷电路板(PCB

2025-07-18 18:20:58 1013

1013

今天给大家分享一下示波器1MΩ和50Ω输入阻抗使用问题。打开示波器通道,会发现这里有1MΩ和50Ω的选择。大家可能会疑惑,如果用无源探头接上它,是应该选择1MΩ还是50Ω?接下来带大家一起学习一下

2025-07-16 17:34:17 2635

2635

Texas Instruments SN74AC164-Q1 8位串行输入/并行输出(SIPO)移位寄存器包含一个8位移位寄存器,具有AND门控串行输入和异步清零(CLR)输入。门控串行(A和B

2025-07-16 15:28:05 516

516

Texas Instruments SN74ACT164-Q1 8位串行输入/并行输出 (SIPO) 移位寄存器包含一个8位移位寄存器,带有异步清零 (CLR) 输入和与门控制的串行输入。门控串行

2025-07-16 10:06:45 545

545

本文介绍100MΩ输入阻抗探头的技术优势、参数及选型要点,强调其对高阻抗电路和高压测量的精准性与可靠性。

2025-07-15 17:41:09 734

734 处于高阻抗状态。OE\输入的运行不会影响内部寄存器数据。Texas Instruments SN74ACT595-Q1设备符合汽车应用类AEC-Q100认证。

2025-07-07 15:27:27 640

640

阻抗状态。内部寄存器数据不受OE\输入操作的影响。Texas Instruments SN74AC596-Q1器件符合汽车应用类AEC-Q100认证。

2025-07-05 15:47:28 748

748

在电子测量领域,示波器作为信号分析的核心工具,其输入阻抗的合理设置直接影响测量结果的准确性。普源DHO824示波器凭借其高精度与多功能性,成为工程师调试复杂电路的首选设备。本文将深入解析该型号示波器

2025-05-29 10:12:45 1065

1065 学习本章时,配合以上芯片手册中的“19. I/O Ports”章节一起阅读,效果会更佳,特别是涉及到寄存器说明的部分。本章内容涉及到较多寄存器方面的深入内容,对于初学者而言这些内容丰富也较难理解,但非常有必要细读研究、夯实基础。

2025-05-28 17:37:09 1118

1118

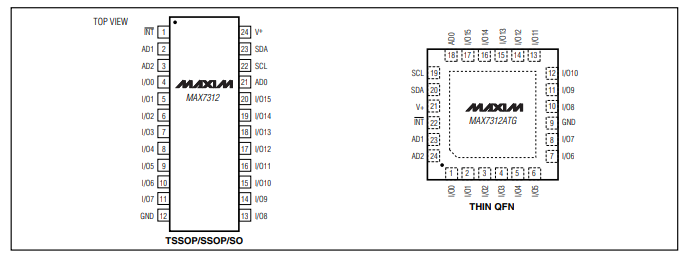

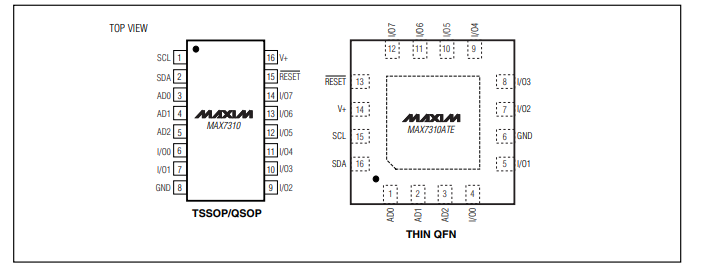

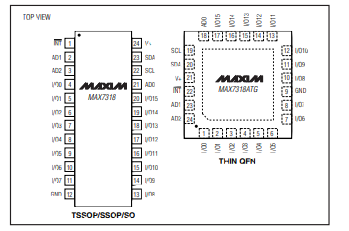

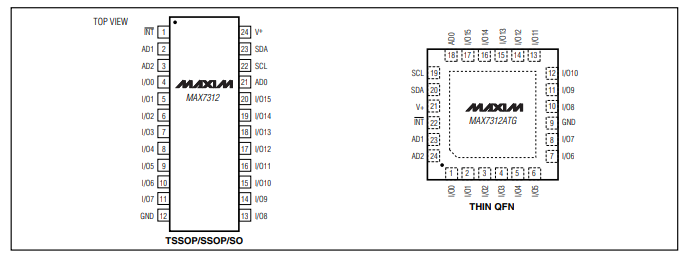

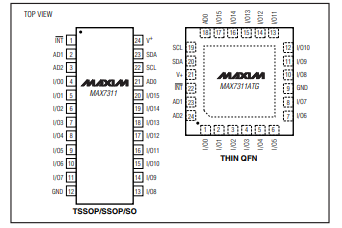

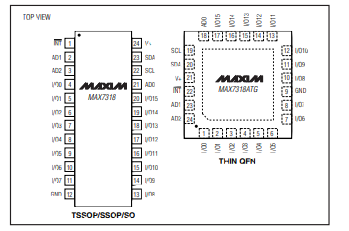

I²C兼容的串行接口逻辑,兼容于SMBus。系统主机可以通过写入高电平有效的极性反转寄存器反转MAX7312的输入数据。系统主机通过写入总线超时寄存器使能或禁用总线超时。

2025-05-26 15:41:31 778

778

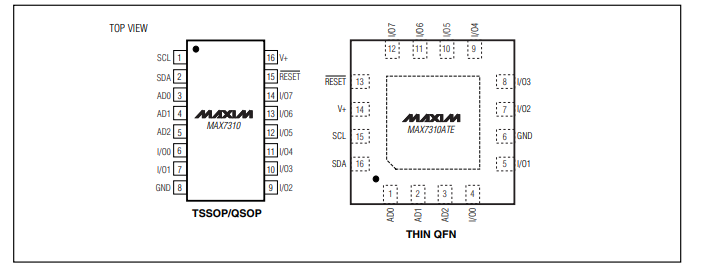

兼容的串行接口。系统主控制器向高有效的极性反转寄存器写入适当的数据,可以将MAX7310的输入数据反向。通过总线延时寄存器,系统主控制器可以使能或禁止总线延时。

2025-05-26 15:41:31 825

825

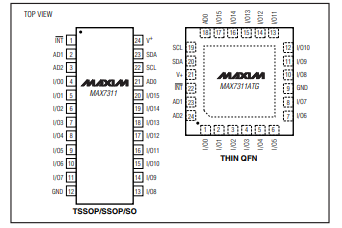

寄存器和一个SMBus/I²C兼容的串行接口。系统主控制器向高有效的极性反转寄存器写入适当的数据,可以将MAX7311的输入数据反向。通过总线延时寄存器,系统主控制器可以使能或禁止总线延时。

2025-05-26 11:33:37 678

678

I²C兼容的串行接口逻辑,它与SMBus兼容。系统主机可以通过写入高电平有效的极性反转寄存器反转MAX7318的输入数据。

2025-05-26 09:57:01 776

776

本篇文章我们讲解了寄存器的概念、地址映射和寄存器操作等内容,内容比较干,大家有个概念即可,不要求全部熟记掌握,有需要时可重复查阅观看。下一篇我们将开始进行实操内容,通过控制单片机的GPIO来点亮一颗LED,敬请期待!

2025-05-21 14:23:18 1254

1254

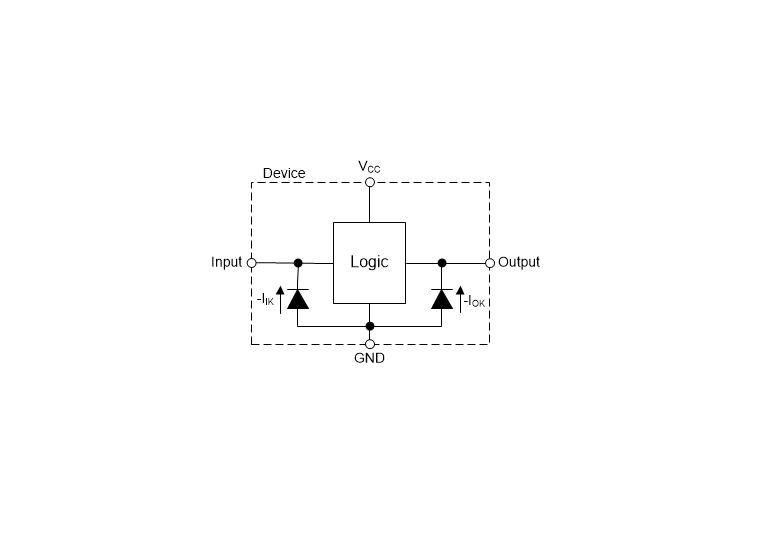

的电荷注入会引起电流尖峰,进而使施加于ADC输入端的电压产生方向不定(流入和/或流出)的下降或尖峰。压降与连接到ADC输入段的传感器的输出阻抗成比例。

平均电流值

一般而言,数据手册不会提供电流峰值

2025-05-08 14:47:52

时,表示队列为满;当Head指针等于Tail指针时,表示队列为空。该模块中的状态机用来实现门铃寄存器信息更新的流程控制工作。队列管理状态机的跳转图如图2所示。

图2 队列管理状态机跳转图

各状态说明如下

2025-05-03 20:19:16

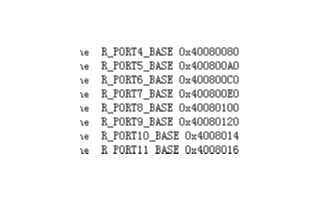

由于寄存器的数量是非常之多的,如果每个寄存器都用像*((uint32_t*)(0x40080000+0x0020*1))这样的方式去访问的话,会显得很繁琐、很麻烦。为了更方便地访问寄存器,我们会借助C语言结构体的特性去定义寄存器和寄存器位域,这是通用的做法。

2025-04-22 15:30:44 1787

1787

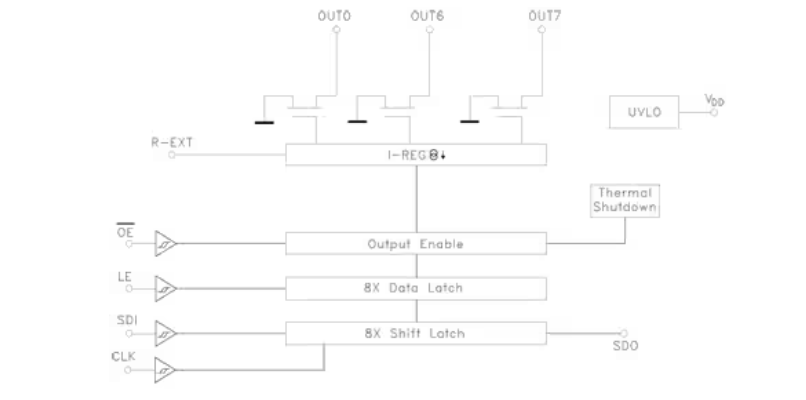

移位寄存器,用于馈送一个 8 位 D 型存储寄存器。在输出级,设计了 8 个稳压电流源,提供 5-100 mA 恒定电流来驱动 LED,输出电流设置时间为 11 ns(典型值),从而提高了系统性能。

2025-04-16 18:10:27 822

822

输入阻抗匹配是确保信号完整性和测量精度的关键。模拟示波器通常提供 1 MΩ ± x%(高阻)和 50 Ω 两种输入阻抗模式,需根据被测信号特性选择匹配模式。以下是确保匹配的详细步骤与注意事项:一

2025-04-08 15:25:44

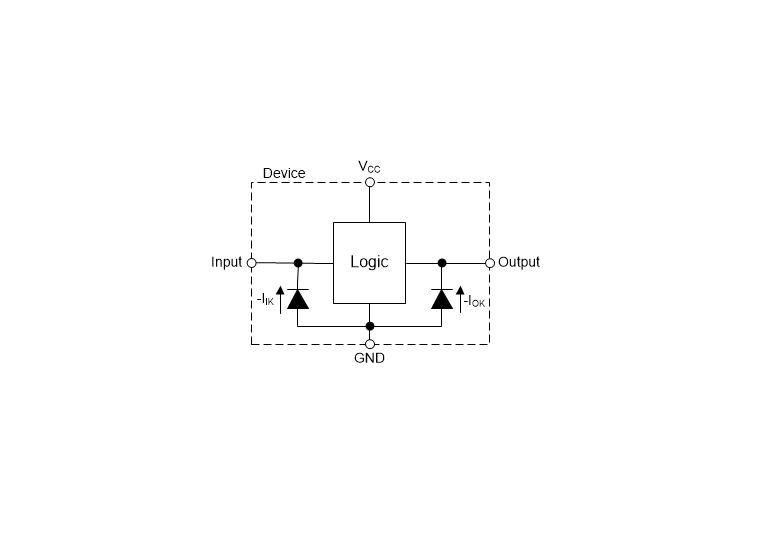

频率的改变而改变。一、输入阻抗输入阻抗是指一个电路输入端的等效阻抗。在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗Rin就是U/I。你可以把输入端想象成

2025-03-22 19:32:30 3085

3085

我需要在DLPC3478上使用DLPA2005下面这个寄存器,请告知DLPC3478寄存器的地址是多少,控制命令是什么?非常感谢!!!

下图是 DLPA2005的寄存器地址和值。

2025-02-21 07:35:48

电子发烧友网站提供《74LVT16543A寄存器收发器规格书.pdf》资料免费下载

2025-02-19 17:28:39 0

0 电子发烧友网站提供《74ALVCH16952 16位寄存器收发器规格书.pdf》资料免费下载

2025-02-19 16:39:24 0

0 电子发烧友网站提供《74ALVCH16646 16位总线收发器/寄存器规格书.pdf》资料免费下载

2025-02-19 15:44:51 0

0 电子发烧友网站提供《74HC165-Q100;74HCT165-Q100并行输入/串行输出移位寄存器规格书.pdf》资料免费下载

2025-02-14 16:12:39 0

0 电子发烧友网站提供《74HC165;74HCT165移位寄存器规格书.pdf》资料免费下载

2025-02-14 16:06:46 0

0 电子发烧友网站提供《74HC164;74HCT164 8位串行输入、并行输出移位寄存器规格书.pdf》资料免费下载

2025-02-14 15:14:06 0

0 电子发烧友网站提供《74HC164-Q100;74HCT164-Q100串行输入、并行输出移位寄存器规格书.pdf》资料免费下载

2025-02-14 15:09:05 0

0

对TVP7002和THS8200寄存器采用了:TVP7002+THS8200 720p60Hz 422 Embedded Sync Setup的寄存器设置,在PC机上采用1280×720分辨率输出到TVP7002后,THS8200不能输出图像。请问是不是我们输入源不对还是某些寄存器初始化不对?

2025-02-12 07:44:50

电子发烧友网站提供《74LV165A-Q100 8位并行输入/串行输出移位寄存器规格书.pdf》资料免费下载

2025-02-11 15:39:59 0

0 电子发烧友网站提供《74LV165A 8位并行输入/串行输出移位寄存器规格书.pdf》资料免费下载

2025-02-11 15:36:00 0

0

如题,ADS1234的输入阻抗怎么从手册上看出来,找了半天也没找到,有个阻抗5k左右的信号(硅压阻传感器),不加跟随器直接接到AD管脚行吗?如果不行会有什么影响?

2025-02-11 08:29:21

请问AFE5801在写寄存器的时候,可以使CS信号拉低48个周期,连续写两个寄存器吗?很急,求解释。

2025-02-11 06:53:57

想法:使用HC-SR04超声波模块检测距离,利用输入捕获计算模块高电平的时间与DMA传输输入捕获寄存器的数值。

配置描述:

将DMA设置为如下图:

故障描述:

如果使用DMA,则数据显示为0,如果是

2025-02-10 14:31:02

电子发烧友网站提供《74HC594-Q100;74HCT594-Q100带输出寄存器的8位移位寄存器规格书.pdf》资料免费下载

2025-02-09 15:19:54 0

0 电子发烧友网站提供《74HC594;74HCT594移位寄存器规格书.pdf》资料免费下载

2025-02-09 14:53:14 1

1 ;

EnableInterrupts;

//ADS1246_SCK_DATA=Low; //ʱÖÓµÍ

//ADS1246_SCK_DATA=High;

DelayUS(40);

ADS1246_CS2_DATA=High;//Ƭѡ¸ß

ADS1246_START_DATA=High;

附件为在读第一个寄存器(BCS)时的波形,在DOUT上没有发现读取数据的波形。

2025-02-07 07:09:14

,

为14555,根据公式计算后约为4.338mv,误差太大了。

请问各位,应该从哪些方面查找问题以及THS4521的输入阻抗如何计算呢?

2025-02-06 08:42:36

74HC595D是一颗高速寄存器 / 输出锁存器芯片,采用CMOS硅栅工艺,它包含一个8位串行输入与并行输出移位寄存器,并提供一个8位D型存储寄存器,具有8位3态输出,分别提供独立的时钟信号给移位寄存器和存储寄存器,移位寄存器具有直接清零功能和串行输入输出功能以及级联应用(采用标准引脚)

2025-02-05 17:21:56 969

969

我在写ADS1247驱动的时候,发现不能将值写入寄存器,能够读取寄存器中的值,但是一直是复位的值,而事先写的值并没有写进去。想请教下各位是怎么回事,以下是一段测试代码。

SPI_CS

2025-01-23 08:07:15

寄存器分为基本寄存器和移位寄存器两大类。基本寄存器只能并行送入数据,也只能并行输出。移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串

2025-01-22 17:25:06 1

1 基本寄存器和移位寄存器两大类。基本寄存器只能并行送入数据,也只能并行输出。移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,

2025-01-22 17:24:03 10

10

我用1118芯片读数据时出了问题,就是我不管改config寄存器值还是AIN输入,他的输出都为定值,经排查读DOUT端口出了偏差(红色字体处未执行),我用的单端输入(0x758A)AIN输入为一个

2025-01-17 07:45:19

一、移位寄存器 SLICEM函数发生器也可以配置为32位移位寄存器,而无需使用slice中可用的触发器。以这种方式使用,每个LUT可以将串行数据延迟1到32个时钟周期。 移入D(DI1 LUT引脚

2025-01-16 17:45:50 1552

1552

我在进行AD设计,SN74CBT3251芯片输出后给ADC10321输入,之间需要考虑阻抗匹配。请问SN74CBT3251的输出阻抗是多少?ADC10321的输入阻抗是多少?谢谢

2025-01-16 06:06:53

这些开关是由哪些寄存器控制的,我在手册里怎么没有找到,我想配置为单端输入,不知道都需要注意哪些寄存器,在线等答案,望各位大侠帮忙

2025-01-15 08:31:55

目前正在使用ADS7841,将输入信号反接,输入-2V电压信号,将ADC的输出转换成电压,大约有50mV,按理应该为0才正确啊。另外:

1、ADC的输入阻抗能达到多大,输入阻抗很大是否更容易受干扰

2025-01-14 07:56:51

想请问下ADS1258这款芯片的输入阻抗是多少,我在手册上看到差分输入阻抗是65KΩ,单端的没有看到。我用万用表测量了下单端输入和地之间的阻抗,大约25MΩ,这个就是单端的输入阻抗么?谢谢

2025-01-13 06:15:03

ADS1281应用在寄存器控制模式下,根据其PDF手册介绍其同步引脚SYNC上产生一个同步脉冲信号,其转换器内部会重置内部数据,那么其重置的是内部数据寄存器的数据,还是重置内部所有的寄存器的状态?

2025-01-10 06:34:59

我用ADS1299采集诱发脑电信号。查手册查不到芯片的输入阻抗为多少?只查到DC input impedance的数值。 烦请TI工程师告知ADS1299的输入阻抗数值和解释下DC input impedance!谢谢!!THANKS!

2025-01-06 06:00:01

电子发烧友App

电子发烧友App

评论