在学习嵌入式系统的过程中,定时器有关内容的学习是必不可少的一个环节。定时器定时功能的实现,最主要的还是靠其内部的计数器。那么,计数器是如何实现计数功能的呢?接下来就来简单介绍一下计数器的实现电路。

2023-09-25 14:18:48 238

238

什么是进位计数制

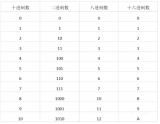

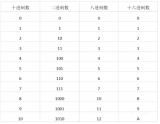

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原

则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2023-08-20 09:32:57 171

171

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。

2023-08-12 09:17:12 705

705 数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2023-07-04 11:06:26 273

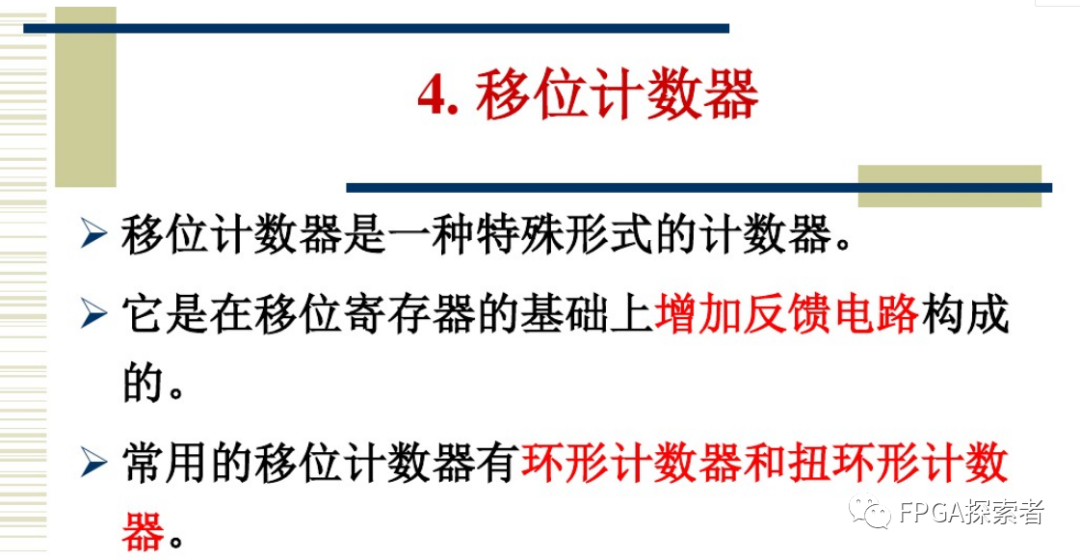

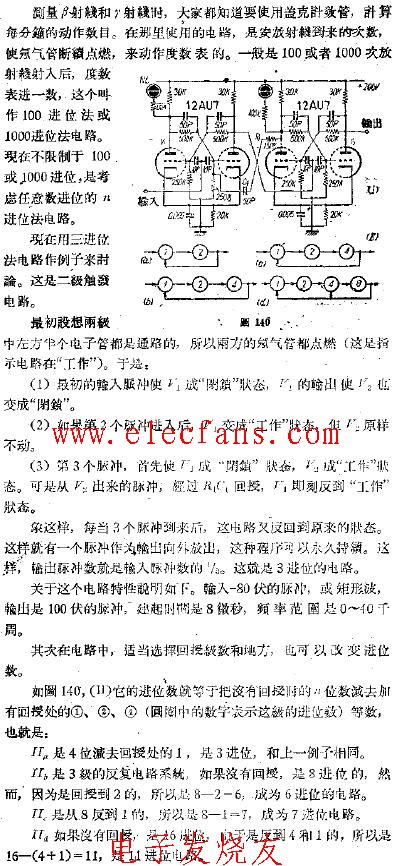

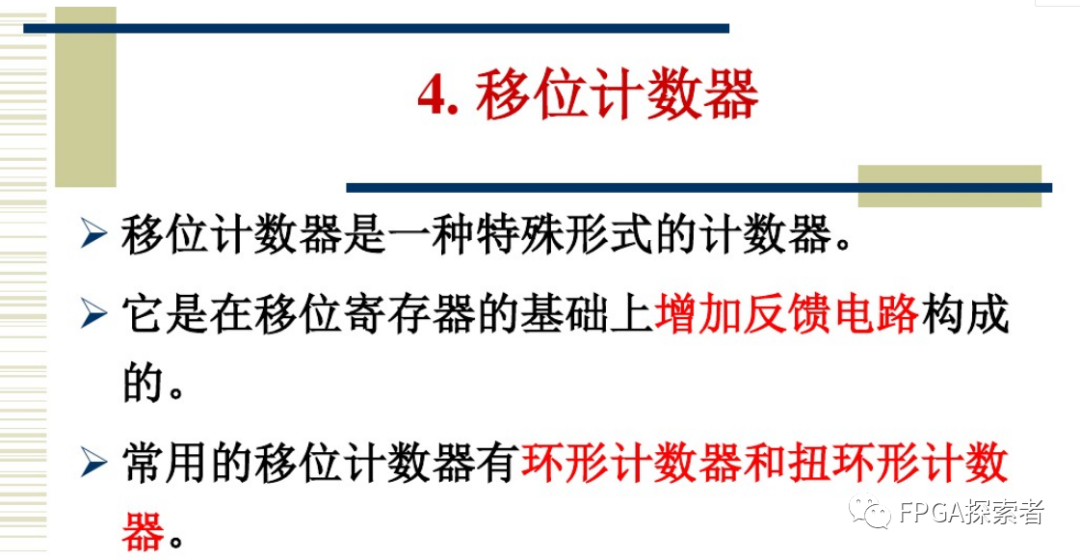

273 扭环形计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

2023-06-27 10:18:23 297

297

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。它按进位的原则进行计数的方法,称为进位计数制。

2023-04-27 11:32:59 1340

1340

进制也就是进位计数制,是人为定义的带进位的计数方法。对于任何一种进制---N进制,就表示每一位置上的数运算时都是逢N进一位。

2023-02-27 15:08:01 332

332 14 级纹波进位二进制计数器/除法器和振荡器-HEF4060B

2023-02-15 18:54:07 0

0 14 级纹波进位二进制计数器/除法器和振荡器-HEF4060B_Q100

2023-02-15 18:53:56 0

0 FX2N系列PLC的32位加减双向计数器(设定值-2147483648~2147483647)

Ø 通用加/减双向计数器:C200~C219(20点);

Ø 停电保持加/减双向计数器:C220~C234(15点);

2023-01-29 15:20:22 1124

1124 PLC闪烁电路计数停止

2022-11-03 11:14:51 874

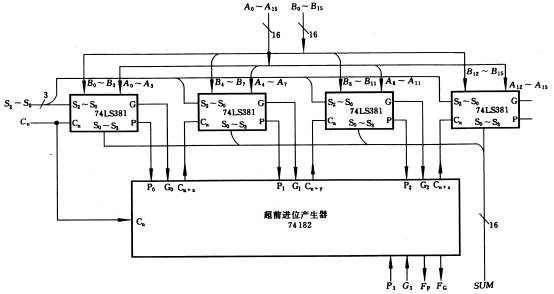

874 行波进位加法器和超前进位加法器都是加法器,都是在逻辑电路中用作两个数相加的电路。我们再来回顾一下行波进位加法器。

2022-08-05 16:45:00 639

639

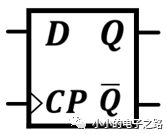

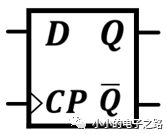

1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 15

15 扭环形计数器,约翰逊计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

2022-06-15 09:27:57 1630

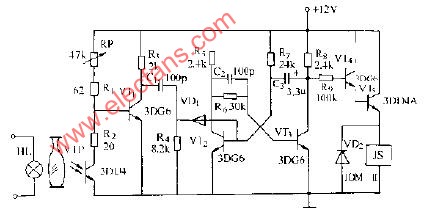

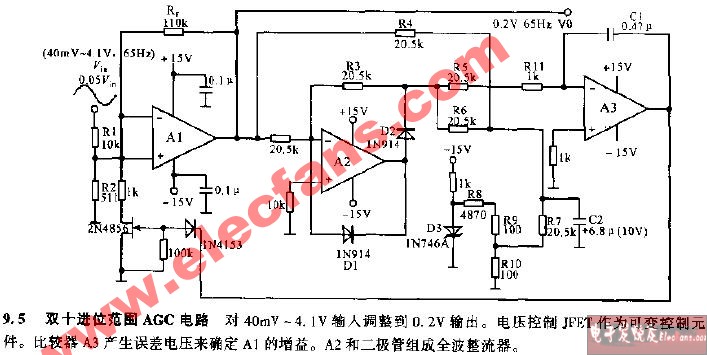

1630 双十进位范围AGC电路

2009-09-11 00:50:07

数字电子钟“时”计数电路的设计与仿真

2021-12-30 13:55:15 51

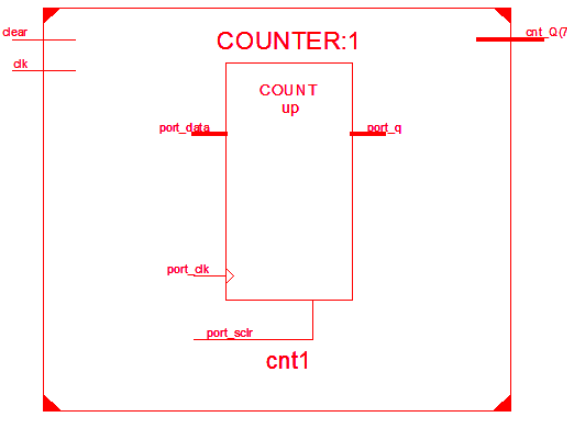

51 计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-11-25 18:06:07 32

32 ADSP-2116N EZ-KIT有限公司设计数据表(修订3.0)

2021-06-17 15:33:57 11

11 ADSP-2116N EZ-KIT有限公司设计数据表(修订3.0)

2021-04-13 12:21:32 1

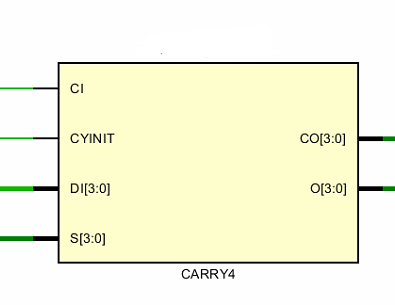

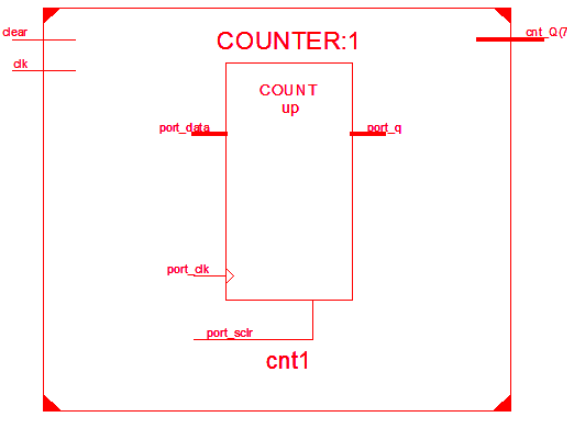

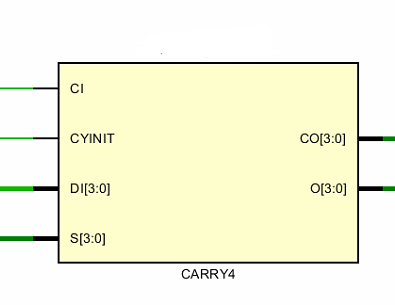

1 该计数器从0 计数到4294967295,然后回滚到0 并重新开始计数。它只需要FPGA 上一点点的资源就可以迅速完成计数,这都多亏了FPGA 中隐藏的进位链。让我们来看这种计数器的几种变体。

2020-12-11 17:26:55 12

12 在FPGA中我们写的最大的逻辑是什么?相信对大部分朋友来说应该是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到进位

2020-11-16 16:35:26 5466

5466

假设时钟分频是N,则设置一个计数器,计数长度是N(即从0计数到N-1),然后在计数器为计数到(N-1)/2的时候,翻转一下分频时钟信号。

2020-11-06 13:59:47 9216

9216

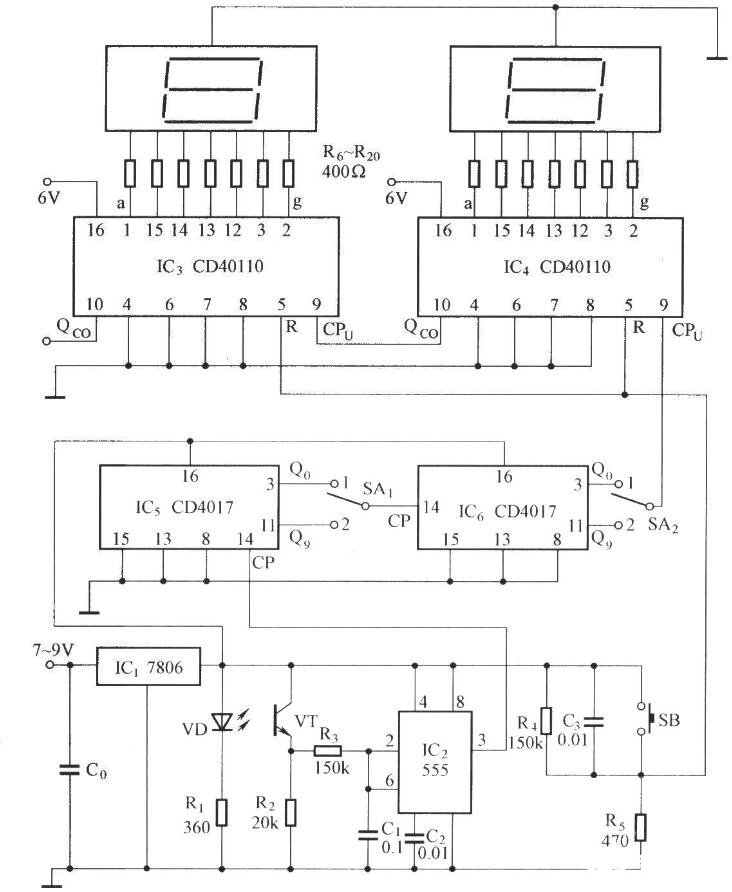

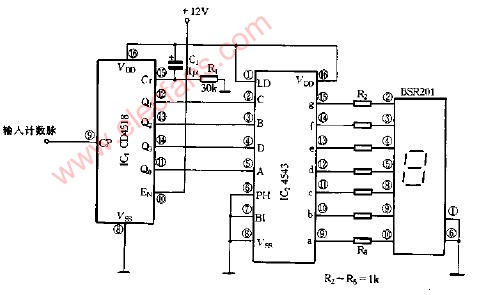

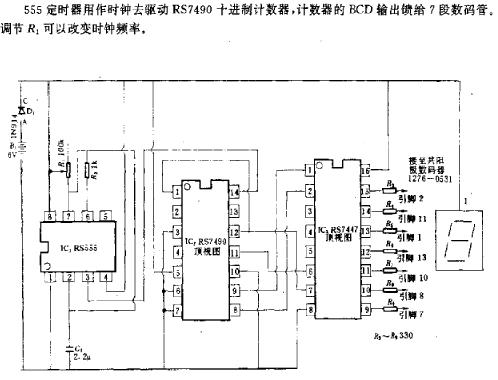

如下图所示,图a中采用十进制七段存储-译码-驱动单元74143,此单元对所有段都有恒流输出。在电压为5V时每段电流约为15~22mA.七段译码器的BCD数据可以由脚17~20上取出。脚22用于进位,即当计数值到9后就为低电平,其余为高电平。利用这个信号可以控制上一位计数器。

2020-01-29 16:40:00 3316

3316

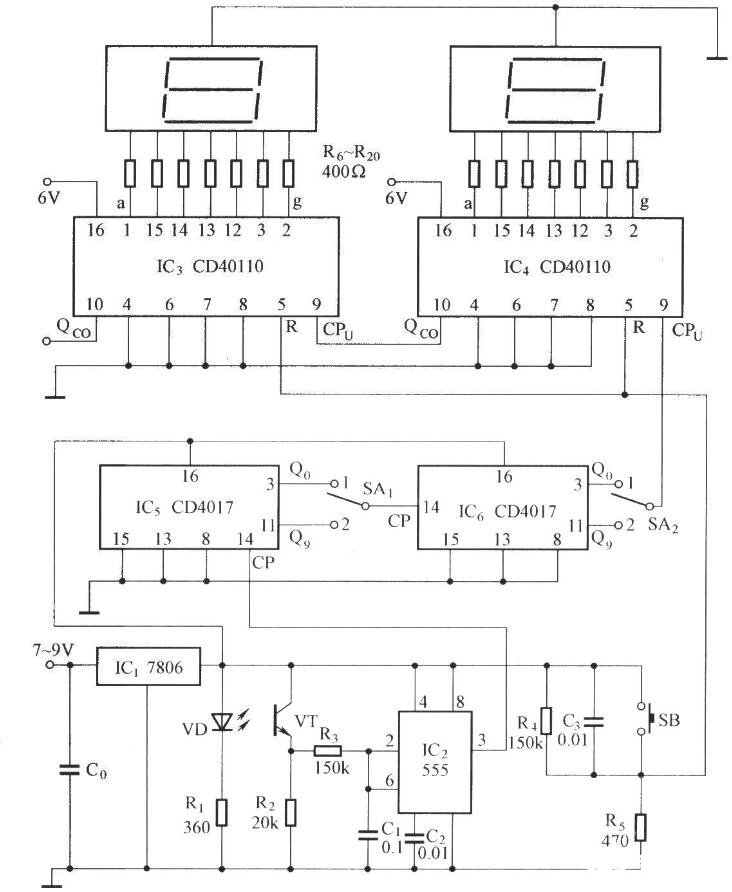

该电路由光电输入电路(VD,VT),计数脉冲形成电路(555),倍率调节电路(IC5,IC6)和计数与显示电路组成(CD40110)。

2020-01-14 16:01:44 2567

2567

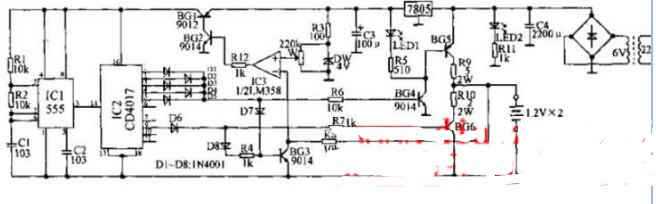

为了提高该电路的变换效率,PWM控制采用贵生动力专用研发的集成控制器件;脉冲产生电路采用了555时基电路与十进位计数器/分频电路。

2020-01-02 15:39:54 5562

5562

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2019-05-06 16:48:36 2923

2923 数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2019-02-14 09:13:52 2939

2939 数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2019-01-18 17:08:52 2859

2859

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2018-10-31 11:24:42 2654

2654 最近在做基于MIPS指令集的单周期CPU设计,其中的ALU模块需要用到加法器,但我们知道普通的加法器是串行执行的,也就是高位的运算要依赖低位的进位,所以当输入数据的位数较多时,会造成很大的延迟

2018-07-09 10:42:00 18610

18610

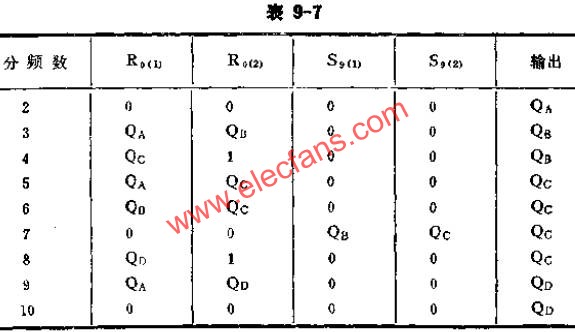

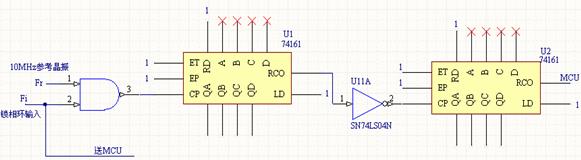

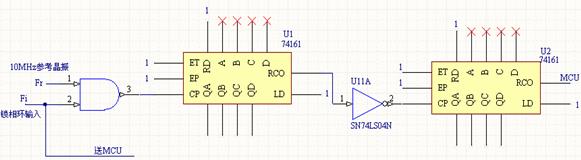

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数

2018-05-08 14:41:38 95799

95799

功能,并且具有进位信号输出,可串接计数使用。重点分析了构成N进制计数器、以74LS163为基础设计一个6分频电路等。

2018-05-08 14:27:23 51924

51924

、秒计数电路。采用两片74LS160按下图所示连接,可以构成作60分频计数,用于数字钟中的秒计数器。标准秒脉冲经过控制门进入秒计数器,并显示其计数值,当计数满60时得到一个进位“分”脉冲,同时秒计数

2018-05-08 09:11:33 61651

61651

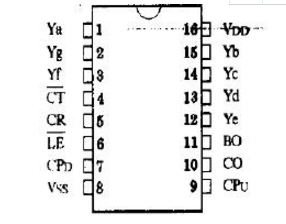

本文主要介绍了cd40110的工作原理详细(cd40110引脚图功能_如何计数及应用电路分享)。CD40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码

2018-03-04 11:34:35 96386

96386

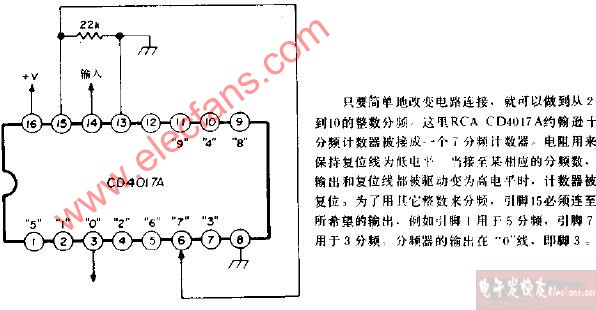

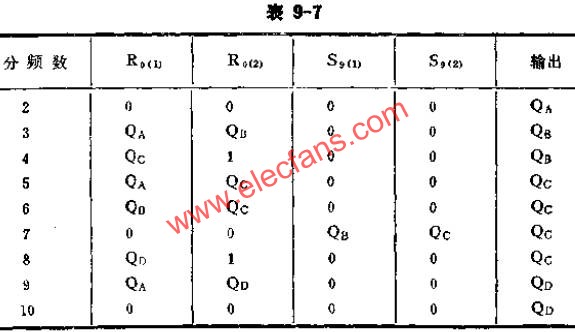

本文开始对CD4017功能与CD4017逻辑结构图进行了介绍,其次分别介绍了用CD4017和选择开关组成多进制计数器、CD4017组成的1/n计数器电路与用CD4017组成1~17进制计数器电路图。

2018-01-31 13:58:06 22819

22819

器的CLK端,电路在计数脉冲的作用下按二进制自然序依次递增1,当个位计数到9时,输出进位信号给十位充当使能信号进位。当计数到24,这显示器个位输出0010(也就是4),显示器十位输出0010也就是2),将十位的QC、个位的QB端接一个二输入与非门,与非门输出一路送入十位计数器的清零端。

2018-01-18 15:43:05 145644

145644

本文主要介绍了74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)。74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端

2018-01-18 10:56:39 324594

324594

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2017-12-25 11:39:12 5011

5011 计的电路进行仿真实验。仿真结果表明设计的计数器能实现所要求的N进制技术功能。最终得出采用反馈复零法可以实现进制计数器的结论。

2017-12-21 17:08:37 60783

60783

74LS160 芯片同步十进制计数器(直接清零) ·用于快速计数的内部超前进位 ·用于n 位级联的进位输出 ·同步可编程序 ·有置数控制线 ·二极管箝位输入 ·直接清零 ·同步计数 本电路是由4 个

2017-12-21 16:29:13 584471

584471

数制也称计数制,是指用一组固定的符号和统一的规则来表示数值的方法。按进位的原则进行计数的方法,称为进位计数制。比如,在十进位计数制中,是按照“逢十进一”的原则进行计数的。

2017-11-30 15:08:36 32541

32541 CD4059A_CMOS可编程1N计数器

2016-06-24 15:33:24 1

1 集成计数器实现N进制计数集成计数器实现N进制计数集成计数器实现N进制计数

2016-06-08 14:28:43 15

15 计数器是用来累计和寄存输入脉冲个数得时序逻辑部件,是数字系统中用途最广泛的基本部件。计数器不仅能用于时钟脉冲的计数,还可以用于分频,定时,产生节拍脉冲及进位数字运算等,是数字系统、计算机系统必不可缺少的部件。

2016-05-05 17:40:59 4

4 为了缩短加法电路运行时间,提高FPGA运行效率,利用选择进位算法和差额分组算法用硬件电路实现32位加法器,差额分组中的加法单元是利用一种改进的超前进位算法实现,选择进位算

2013-09-18 14:32:05 33

33 下图为:电压频率计数电路原理图 图 电压频率计数电路原理图

2012-05-28 09:46:07 2692

2692

计数器是一种重要的时序逻辑电路,广泛应用于各类数字系统中。介绍以集成计数器74LS161和74LS160为基础,用归零法设计N进制计数器的原理与步骤。用此方法设计了3种36进制计数器,并

2012-03-20 10:21:38 95

95 计数器是数字逻辑系统中的基本部件,它是数字系统中用得最多的时序逻辑电路,本文主要阐述了用中规模集成计数器设计任意进制同步加法计数器的设计思想,并对设计方法和步骤作

2012-02-28 11:41:43 6157

6157

异步计数器电路是指其构成的基本功能单元触发器的时钟输入信号不是与触发器在一起的,有的是外输入的脉冲信号,有的是其他触发器的输出。本文给出了N进制 异步计数器 设计方案

2011-10-24 15:39:38 3245

3245

C182可预置数1/N计数器基本上是一个减法计数器,均由四个"T"型触发器和附加控制门组成,具有级连N个计数器

2010-10-19 15:23:07 963

963

T210除了作为2-5-10进制计数器外,还可以接成9以内的N进制计数器,方法是在R0端上串接二个与非门电路,各级触发器

2010-10-19 12:55:17 1344

1344

提出了一种适合FPGA高效运算的专用进位链结构。基于应用范围方面的考虑,我们先对典型的行波进位做了一定的改进,目的是增强逻辑模块的功能实现能力和提高运算速度。提出进

2010-07-28 17:47:54 19

19 摘要:应用CMOS电路开关级设计技术对超前进位全加器进行了设计,并用PSPICE模拟进行了功能验证.与传统门级设计电路相比,本文设计的超前进位电路使用了较少的MOS管,并能保持

2010-05-28 08:18:20 25

25 数字电子技术基础(罗勇)

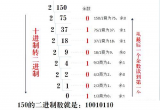

数制与数制转换“数制”是指进位计数制, 即用进位的方法来计数.数制包括计数符号(数码)和进位规则两个方面.

2010-05-24 16:12:14 263

263 可获得IP/十进位输出的对数转换电路

电路的功能

为了把大范围的信

2010-05-08 17:26:36 666

666

Multisim 2001电路仿真软件在计数器中的分析方法:摘 要:Multisim 2001软件是专门用于电子电路仿真与设计的EDA 工具软件,通过具体的实例分析Multisim 2001软件仿真设计实现N进制计数器产

2010-04-25 10:17:15 63

63 计数/译码显示电路: 计数译码显示在现代科学技术中应用非常广泛,它由计数器、译码器和显示器三部分组成,包含数字电子系统的组合逻辑电路和

2009-12-20 12:36:59 128

128 数制与进位记数法

在采用进位记数的数字系统中, 如果只用r个基本符号 (例如0,1,2,…r-1) 、通过排列起来的符号串表示数值,则称

2009-10-13 16:21:46 1527

1527 百进制计数器电路

将两块74LS290进行级联,组成的百进制计数器如图12.8所示。

2009-09-16 15:47:50 5541

5541

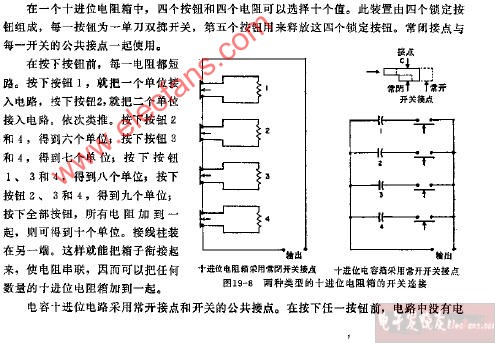

按钮十进位箱电路图

2009-07-03 13:33:00 393

393

图3是可逆、可预置计数器CD4029构成的任意N分频减法计数电路,U/D接“L”电平进行减法计数,B/D接“L”电平按BCD输出码进行计数,低位的Co进位到高位的CT输

2009-06-22 07:44:38 4593

4593

玻璃瓶计数电路图

2009-06-03 15:46:22 627

627

脉冲计数显示电路图

2009-05-08 14:36:00 2439

2439

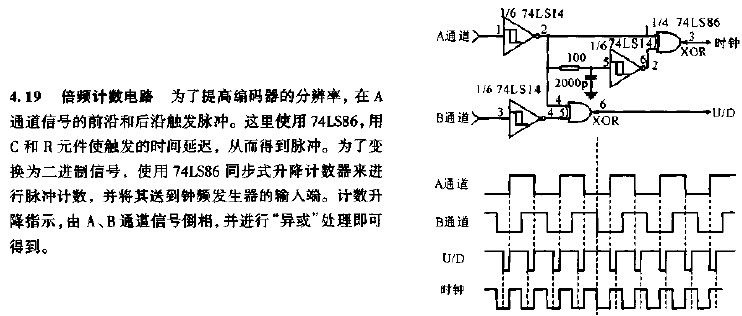

倍频计数电路

2009-04-24 21:39:51 900

900

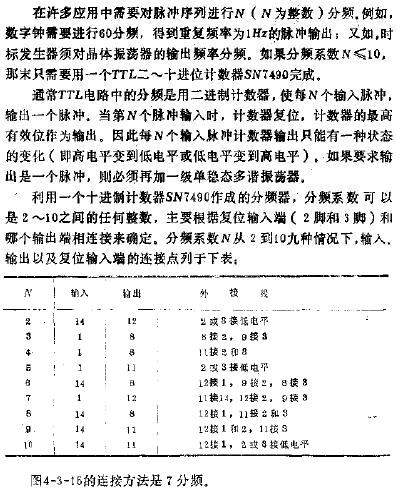

TTL十进位计数器构成的分频器

2009-04-11 10:14:57 1067

1067

十进位计数器

2009-04-10 10:25:20 661

661

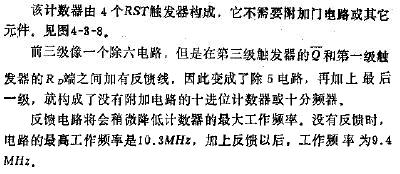

超前进位产生器74182

多位数的超前进位加法器的进位是并行产生的,大大提高了一算速度。但是随着位数的增加,超前进位逻辑电路越来越复杂。为了解决这一矛盾,设计

2009-04-07 10:37:14 14122

14122

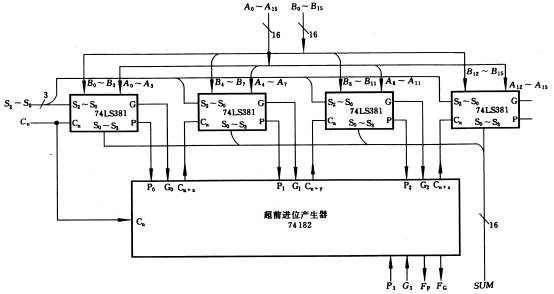

超前进位集成4位加法器74LS283

由于串行进位加法器的速度受到进位信号的限制,人们又设计了一种多位数超前进位

2009-04-07 10:36:35 26072

26072

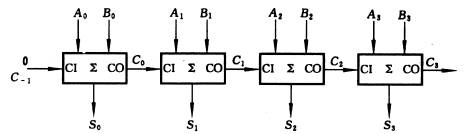

串行进位加法器

若有多位数相加,则可采用并行相加串行进位的方式来完成。例如,有两个4位二进制数A3A2A1A0和B3B2B

2009-04-07 10:35:30 15784

15784

双十进位范围AGC电路图

2009-04-01 21:39:31 557

557

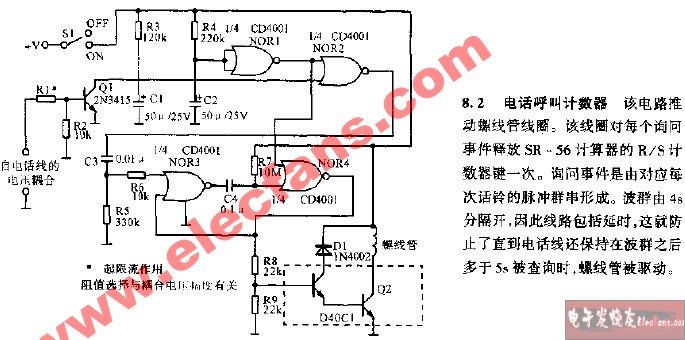

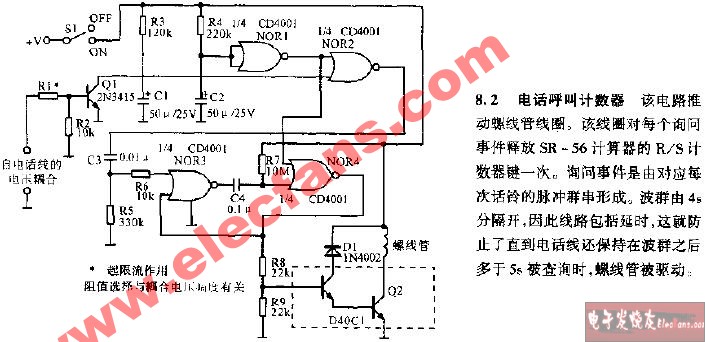

电话呼叫计数器电路

2009-03-29 18:29:30 595

595

CMOS可编程N分频计数器电路图

2009-03-29 09:55:36 738

738

电话呼叫计数器电路

2009-03-23 21:21:10 427

427

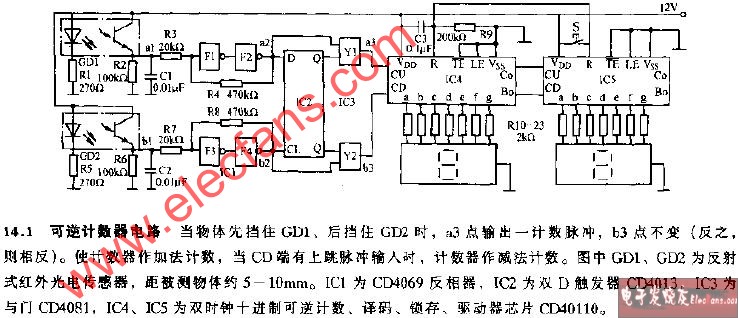

可逆计数器电路

2009-02-25 21:53:53 898

898

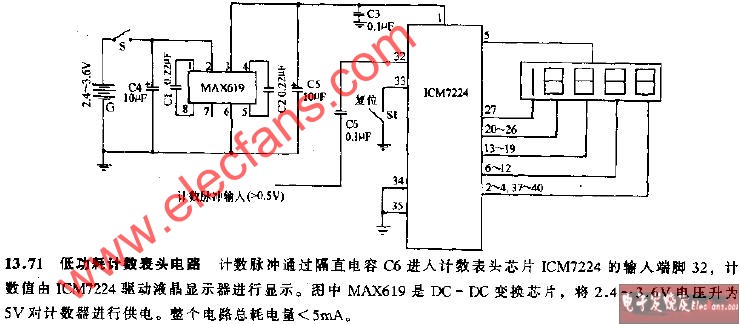

低功耗计数麦头电路

2009-02-25 21:46:58 351

351

低功耗计数麦头电路

2009-02-25 21:17:01 619

619

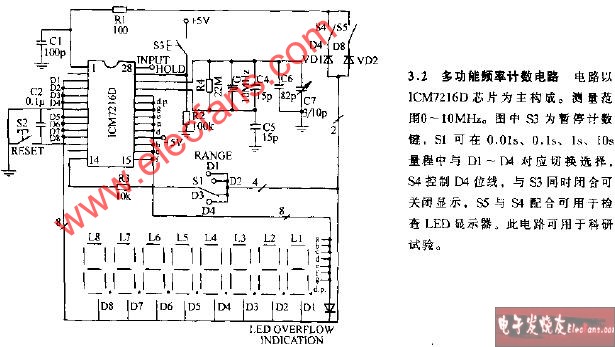

多功能频率计数电路

多功能频率计数

2009-02-09 16:10:13 675

675

电线自动成圈机计数电路

2009-02-06 10:14:02 589

589

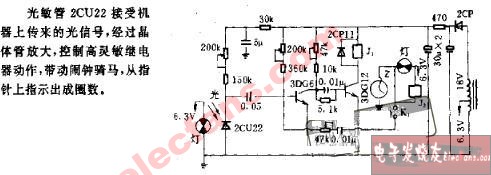

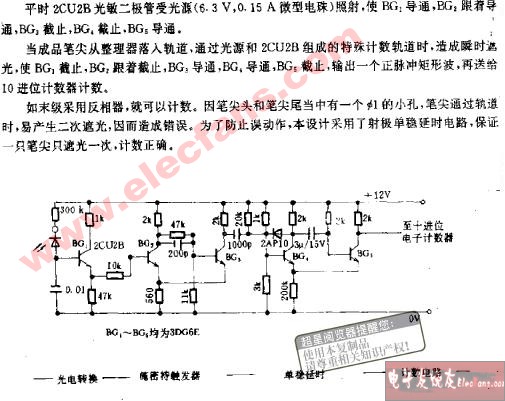

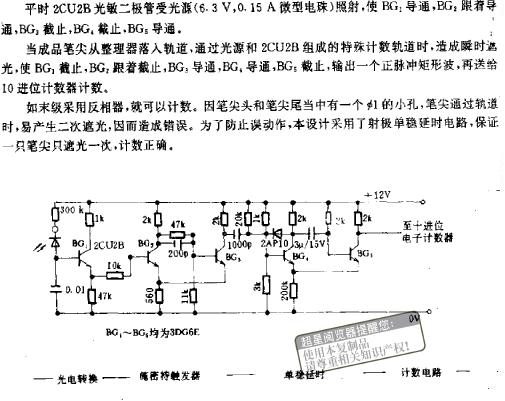

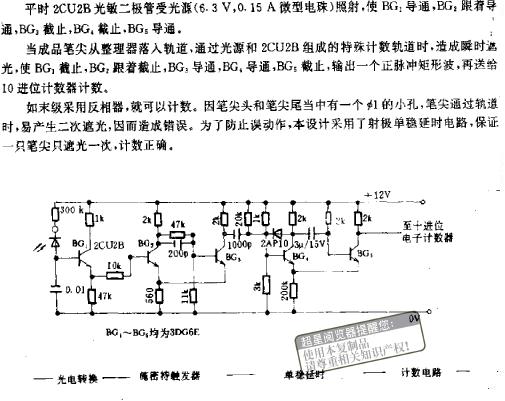

成品笔尖计数电路

2009-02-06 10:07:57 637

637

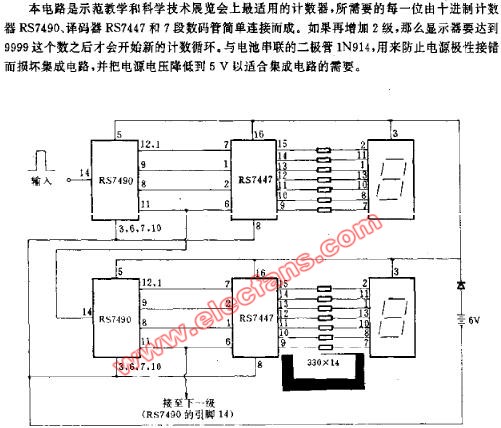

数字计数演示电路图

成

2009-02-05 15:54:13 885

885

数字计数演示电路

2009-02-05 15:53:11 528

528

成品笔尖计数电路

2009-02-05 15:52:50 600

600

表演用的多位计数电路

2009-02-04 23:57:25 536

536

倒计时计数电路倒计时计数电路主要由计数器构成,它在整个系统设计中的作用是实现计时计数,在此我们选用减法计数器,因为本设计说明计时

2008-12-01 16:06:50 6986

6986 计数译码显示在现代科学技术中应用非常广泛,它由计数器、译码器和显示器三部分组成,包含数字电子系统的组合逻辑电路和时序逻辑电路,因此本实验是一个综合性的实

2008-10-09 18:19:54 115

115 脉冲计数器电路图,本计数器包括降整流电路,光控脉冲发生器,计数电路,译码,显示电路。

2008-04-03 13:37:11 3295

3295

相位角测量采用硬件计数方式,而不使用单片机直接计数,因为用硬件计数可以把精度提得更高。这里我们使用两片74HC161串联组成256进制的串行进位计数方式。外部参考频率选用1

2008-04-03 13:21:48 5924

5924

电子发烧友App

电子发烧友App

硬声App

硬声App

238

238

171

171

705

705 273

273 297

297

332

332 1124

1124 15

15 1630

1630 32

32 12

12 5466

5466

9216

9216

3316

3316

2567

2567

2923

2923 2939

2939 2859

2859

2654

2654 18610

18610

95799

95799

51924

51924

61651

61651

96386

96386

22819

22819

145644

145644

324594

324594

5011

5011 60783

60783

584471

584471

32541

32541 4

4 33

33 95

95 6157

6157

3245

3245

1344

1344

19

19 25

25 263

263 63

63 4593

4593

14122

14122

26072

26072

115

115 5924

5924

评论