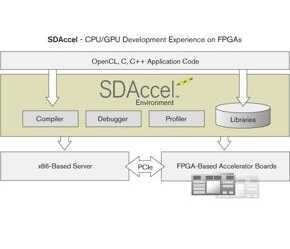

OpenCL 标准为软件开发人员提供了一个统一的编程环境,可编写高效、可移植的代码,实现丰富的算法,SDAccel 开发环境符合 Khronos OpenCL 1.0 标准, 因此可以轻松地在 FPGA 上对 OpenCL 进行加速。

Xilinx 已经形成一个联盟成员的全球生态系统,可提供各种平台、库和设计服务帮助全球设计团队充分利用在其 OpenCL、C 和 C++ 应用中基于 FPGA 的加速。

以下通过两个视频向您详细介绍 OpenCL 应用架构,以及内存架构,并同时还向您演示如何使用赛灵思 FPGA 进行加速。

OpenCL 应用架构详解

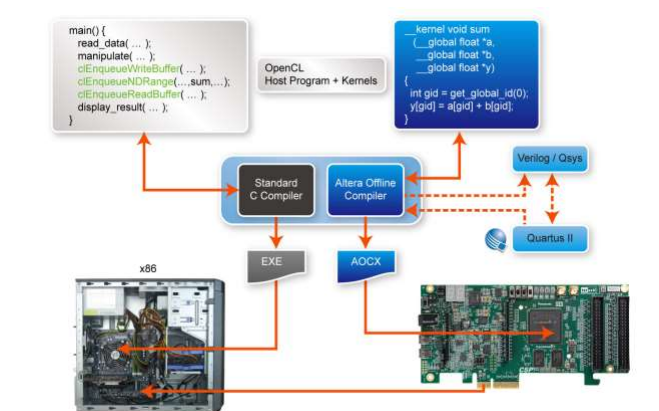

OpenCL 中对于异构计算应用为所有的实现定义了一个基本的编程模型标准。本视频介绍了一个 基于 OpenCL 应用的主机代码和内核元素,并演示了这些元素包含 FPGA 加速器对系统映射的解释

OpenCL 内存架构详解

OpenCL 定义了一个内存架构和抽象模型,是一个可应用于计算设备的通用标准。这就意味着程序员只需要了解一个可简化应用编程的内存模型就足够了。本视频提供了对 OpenCL 内存模型架构的详解,并演示了如何在 FPGA 加速器件上实现它。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639148 -

赛灵思

+关注

关注

33文章

1798浏览量

133651 -

编程

+关注

关注

90文章

3723浏览量

97434

发布评论请先 登录

相关推荐

热点推荐

Intel altera opencl 入门

(RHEL) 5或者6。

对于Linux操作系统, 安装操作系统过程中要把C编译器包括GCC勾选上。

2.安装Altera的软件和搭建OpenCL环境(以Windows为例,Linux也类似

发表于 06-04 18:25

介绍android下的OpenCL开发步骤

1、介绍android下OpenCL开发Firefly rk3288采用Mali-T764的GPU,该GPU支持OpeCL 1.1。下面一步一步介绍android下OpenCL开发。1

发表于 04-11 14:35

Altera发布业界第一个面向FPGA的OpenCL计划

Altera公司(NASDAQ: ALTR)今天发布FPGA和SoC FPGA的开放计算语言(OpenCL™)标准开发计划。OpenCL标准是基于C语言的开放标准,适用于并行编程。Altera的

发表于 11-16 16:12

•1120次阅读

面向Altera FPGA的OpenCL:提高性能和设计效能

开放计算语言(OpenCL)编程模型与Altera的并行FPGA体系结构相结合,实现了功能强大的系统加速解决方案。面向OpenCL的Altera SDK为您提供了设计环境,工程师很容易

发表于 11-06 14:56

•2572次阅读

OpenCL 代码的可移植性优势及异构系统中的应用

编程模型。利用这一 SDK,熟悉 C 语言的系统开发人员和编程人员能够迅速方便的在高级语言环境中开发高性能、高功效、基于 FPGA 的应用。Altera 面向 OpenCL 的 SDK

发表于 09-15 15:46

•0次下载

为OpenCL应用创建、构建和调试英特尔SDK的OpenCL代码

Create, Build, and Debug OpenCL code with Intel SDK for OpenCL Applications

英特尔SDKfor OpenCL使用介绍

了解如何使用英特尔®SDKfor OpenCL™ - 代码分析器来优化英特尔GPU上的OpenCL™应用程序

OpenCL应用程序的主机代码和内核元素

用于异构计算的OpenCL标准为实现OpenCL标准的所有计算设备定义了基本编程模型。

该视频介绍了OpenCL应用程序的主机代码和内核元

适用于OpenCL,C和C ++的Xilinx SDAccel集成开发环境

适用于OpenCL,C和C ++的Xilinx SDAccel集成开发环境符合Khronos OpenCL 1.0规范,并包含OpenCL可安装客户端驱动程序(ICD)。通过ICD扩展

如何使用OpenCL轻松实现FPGA应用编程

实现这一编程思想的转变,是因为 FPGA 借助 OpenCL 实现了编程,程序员只需要通过 C/C++ 添加适当的 pragma 就能实现 FPGA 编程。为了让您用

发表于 07-16 17:58

•7418次阅读

Intel Cyclone V 开发板OpenCL使用手册免费下载

开发环境,以及如何编译和执行C5P的示例项目。请注意,OpenCL编码指令不在本文档的范围内,但用户可以参考Intel FPGA SDK for OpenCL Programming Guide(英特尔FPGA SDK for

发表于 09-01 08:00

•7次下载

OpenCL编程环境作用和介绍

OpenCL编程环境作用和介绍

评论