传输层

数据传输层的主要功能将AD转换器采样的数据映射成8bit位宽的字节数据。先将所有的采样数据线性的排开,然后添加控制字和控制位得到words,也可以选择不加控制字和控制位,则words和之前排列的采样数据相同,添加控制字和控制位有两种方法,第一种在每一个采样点的末尾添加控制位;第二种不在采样点末尾添加控制位,在所有采样点的末尾添加一个控制字,控制字里面的控制位对应前面的采样点。通过添加tail将words进行扩展,使每一个word的位数为N΄位,这个值是4的倍数,控制字不需要扩展。最后将数据划分得到L*F个字节,对应L个通道。在下面会详细介绍。

a) L:AD转换器所拥有的链路数量。

b) M:AD转换器中的转换单元数量。

c) F:每一帧数据中的字节个数。

d) N:AD转换器的分辨率。

e) N΄:每个样本被封装之后的位数。

f) CS:控制位数

g) K:每个多帧的帧数,1到32之间的整数。

h) S:每帧数据中的采样点数

i) HD:高密度模式,HD=0时,单一的采样数据只会在某一个链路上面传输;HD=1时,采样数据会被拆分在多个LANE传输。

j) CF:控制字个数,每一个控制字是8位的数据。

k) T:tail bit

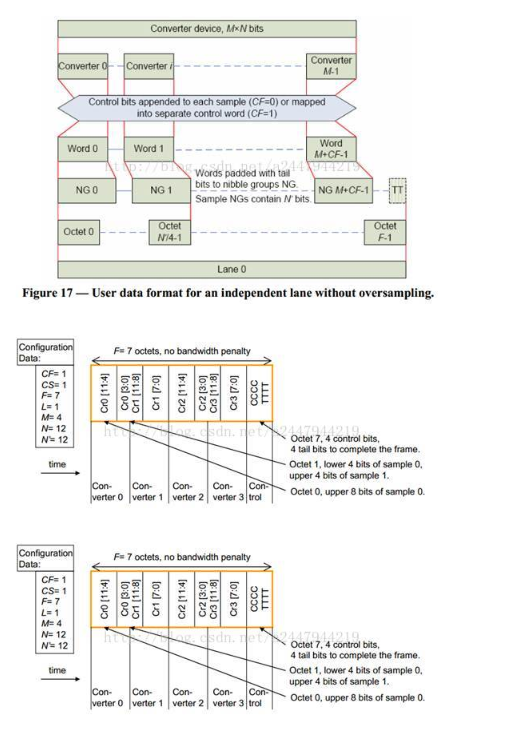

JESD204B数据映射按照S的取值分为两种情况:正常采样情况下的数据映射和过采样情况下的数据映射。当S=1,是正常采样情况下的数据映射;当S》1,是过采样情况下的数据映射。正常采样情况下,帧时钟等于采样时钟;过采样情况下,采样时钟是帧时钟的S倍。

JESD204B数据映射按照L的取值分为两种情况:单通道数据映射和多通道数据映射。当L等于1,是单通道数据映射;当L》1,是多通道映射。

数据映射一共5步,过采样和正常采样的映射主要在第一步数据排列有些不同,正常采样可以看成过采样的一种特殊情况。多通道映射主要在第5步,数据划分的不同。

正常采样情况下的单通道映射(S=1,L=1)

AD转换单元有M个,N位分辨率,数据映射分为5个步骤:

1) 每个AD转换单元有一个采样点,M个转换单元一共M个采样点,每一个采样点有N位数据,将M个采样点线性的排列在一横排,高位在前,低位在后。

2) 将采样点映射为words,这一步实质就是给采样点添加控制位或者控制字。如果这一步选择不添加控制位和控制字(CS=0,CF=0),那么映射的words和之前的采样点完全相同,words的个数与采样点个数相等,M个word,每一个word长度是N位。如果添加控制位和控制字,有两种情况:①在每一个采样点的最低位后面添加控制位(控制位个数根据CS决定)构成word,一共M个word,每一个word长度是N+CS位。②不在采样点的后面添加控制位,将所有控制位组合在一起,构成控制字,放在所有采样点的最后面,控制字个数由CF决定。(控制字的位数:M*S*CS/CF)最后构成了M+CF个words。

3) 如果words不是4的整数倍,需要通过添加tail对words进行扩展,扩展完的words叫“NG”。这一步是可以选择性操作的,当传输效率比易配置优先级更高的时候,这步可以忽略(怎么配置)。通过添加控制位和tail,NG有N΄位,N΄=N+CS+tail,(CS加在控制字里面的时候,这里CS应该为0,只有当CS加在每个采样点后面,CS才等于它实际的值)N΄是4的倍数,N΄其实就是一个采样点最后所要映射成的数据的位数。

4) 映射之后的所有数据如果不是8的倍数,在末尾添加tail,使数据是8的倍数

5) 将所有的数据按8位一个字节划分,一共得到F个字节,所以最后这M个采样点构成了一个F字节的帧。这F字节的帧将在这单通道内传输。

从这上面步骤看出来F其实是根据采样点个数,数据映射方式最后计算出来的。

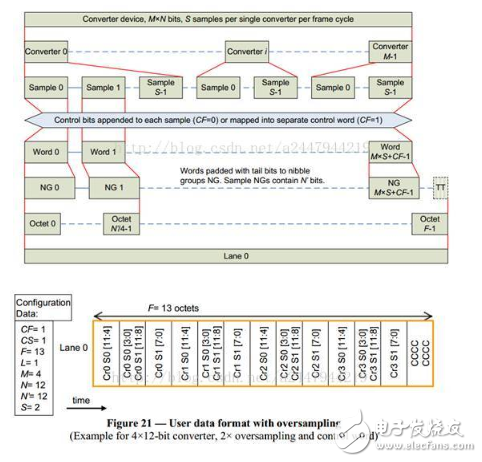

2.2过采样情况下的单通道映射(S》1,L=1)

过采样情况下的映射与正常采样情况下的映射除了第一步不同,其他不相同。M个采样单元,每一个采样单元S个采样点,将这M*S个采样点按照线性顺序排列(ADC1_sample1, ADC1_sample2,……,ADC1_sampleS, ADC2_sample1,ADC2_sample2,……,ADC2_sampleS,……,ADCM_sample1, ADCM_sample2,……,ADCM_sampleS)

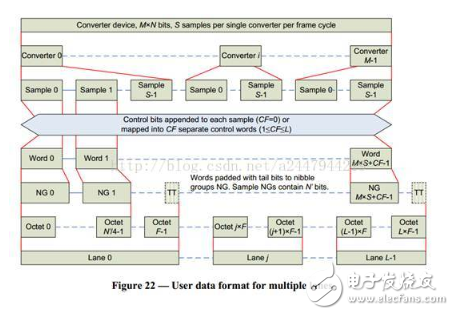

2.3多通道映射数据映射(L》1)

多通道映射和单通道映射前4步相同,只是最后一步不同,最后一步将数据划分为L*F个字节,分别对应L个通道。

在多通道的时候讲了一个参数HD,HD的值决定了一个采样点最后是映射到一个单独的LANE,还是映射到多个LANE。

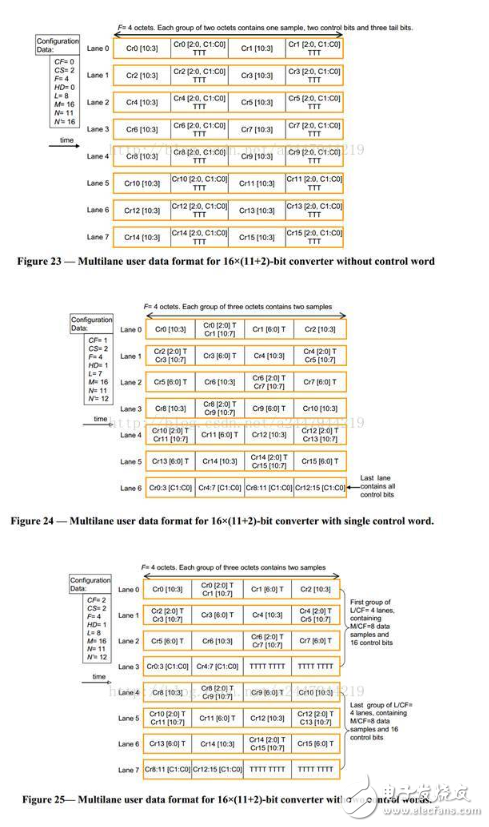

Figure23 24 25分别是无控制字,1个控制字,2个控制字情况下的映射。当多通道映射,且有控制字的时候,L个链路分为CF个组,每一个组包括L/CF个链路,每组传输M*S/CF个采样点。

-

AD转换器

+关注

关注

4文章

245浏览量

40984 -

JESD204B协议

+关注

关注

1文章

4浏览量

2828

发布评论请先 登录

相关推荐

jesd204b协议传输层采样下的单通道映射

jesd204b协议传输层采样下的单通道映射

评论