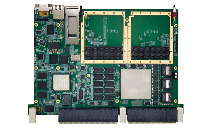

该视频将向开发人员介绍Xilinx和Avnet的新平台,Spartan-6 FPGA 嵌入式套件基于 Spartan®-6 LX45T FPGA 之上,包含可扩展式开发板、关键设计工具以及实现高效嵌入式应用开发所需的 IP 核。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22286浏览量

630298 -

嵌入式

+关注

关注

5186文章

20149浏览量

328848 -

赛灵思

+关注

关注

33文章

1797浏览量

133148

发布评论请先 登录

相关推荐

热点推荐

现已上市:AMD Spartan UltraScale+ FPGA SCU35 评估套件——面向所有开发人员的经济实惠平台

AMD Spartan UltraScale+ FPGA SCU35 评估套件现已开放订购。 该平台由 AMD 构建,为客户提供了一条利用 Spartan UltraScale+

Xilinx FPGA串行通信协议介绍

Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx系统设计中关键的串行通信协议。介绍了它们的特性、优势和应用场景

NICE协处理器接口信号解读--以demo为例

的复位信号。

nice_active表示nice协处理器是否正在工作,但该信号在上层文件中未例化,如下图所示。

nice_mem_holdup信号在e203_lsu_ctrl.v文件中用于覆盖cpu

发表于 10-31 08:01

关于协处理器自定义指令的实现

‘b1111011 ——— 7’h7b

随后的6表示指令的14到12位,即funct3,

协处理器的rtl代码中可见这个定义,这里的110的顺序对应顺序为rd,rs1,rs2,使用寄存器的话就把对应

发表于 10-31 06:36

MD5信息摘要算法实现二(基于蜂鸟E203协处理器)

处理器与E203内核连接,其中状态跳转使用卡洛图进行化简,assign语句实现。使用一个32x6的寄存器堆向MD5协处理器传输数据,控制信号通过对指令译码获得的结果控制MD5

发表于 10-30 07:54

NICE协处理器demo分析及测试

实现思路:

1.硬件设计,编写相应的verilog文件,需要注意的是NICE协处理器定义了一些基本的接口;

2.编写驱动,通过内联汇编的伪指令.insn配置相关的驱动设置;

3.编写用于测试

发表于 10-23 07:05

基于E203 NICE协处理器扩展指令

1、实现功能

基于官方提供的demo nice的硬件代码,设计一个基于e203 nice协处理的加法器。

2NICE协处理器理论学习

nice协

发表于 10-21 14:35

基于E203 NICE协处理器扩展指令2.0

实现功能:基于官方提供的demo nice的硬件代码,设计一个基于e203 nice协处理的加法器。

NICE协处理器理论学习

nice协

发表于 10-21 10:39

AMD Spartan UltraScale+ FPGA的优势和亮点

AMD Spartan UltraScale+ FPGA 集小型封装、先进的 I/O 功能与低功耗等优势于一体。该系列 FPGA 配备高速 16.3 Gb/s 收发器、内置的外部内存控制器以及

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX双FMC接口通用信号处理平台

VPX638是一款基于KU115 FPGA + C6678 DSP的6U VPX双FMC接口通用信号处理平台,该平台采用一片Xilinx的Kintex UltraScale系列

Analog Devices Inc. DC3080A-KIT演示套件数据手册

、DC3078A无线接收器和两个6mm DC3079A应用尺寸接收器。DC3080A-KIT演示套件采用DC3078A无线充电器接收器,具有外部涓流充电电路。当插入电压低于2.8V深度放电电池时,该涓流

spartan 6 14位LVDS 反序列化

spartan 6系列的FPGA 与14位ADC 输出LVDS信号 怎么实现1:14的串转并呢?iserdes2 在ise里面最高只能实现8位啊

发表于 04-25 15:20

Xilinx Spartan-6 FPGA协处理套件演示

Xilinx Spartan-6 FPGA协处理套件演示

评论