近日,基于RISC-V指令集的软核CPU在SWORD4.0上顺利移植,给予用户对SWORD4.0的新体验,用户甚至可以通过Arduino IDE开发RISC-V应用。

在SWORD4.0上移植的是基于RISC-V指令集的F32C开源CPU。CPU通过配置既可以支持RISC-V指令集也可以支持MIPS指令集。

图1F32C github

用户通过对Arduino IDE简单升级,可以使Arduino IDE支持SWORD4.0的RISC-V编译工作。图形化编程环境和大量Arduino范例都有利于用户进行应用开发。

图2升级后的Arduino IDE可以进行RISC-V编译

图3用RISC-V CPU控制LED亮度

图4用RISC-V CPU控制串口输入输出

图5用RISC-V CPU控制7段数码管

RISC-V完全开源、极度精简,非常适合物联网和边缘计算等应用。RISC-V作为SWORD生态系统的一部分,为计算机系统能力培养提供着澎湃动力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

cpu

+关注

关注

68文章

11327浏览量

225899 -

生态系统

+关注

关注

0文章

711浏览量

21617 -

RISC-V

+关注

关注

49文章

2948浏览量

53550

原文标题:RISC-V助力SWORD生态系统演进

文章出处:【微信号:gh_94c30763133f,微信公众号:FPGA那点事儿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

第2章 RV32I:RISC-V基础整数指令集

本章重点讲解构成RISC-V基础整数指令集的基本指令和指

发表于 01-31 21:10

RISC-V基础整数指令集

])标记每个立即数子域。

说明:B类型和 J类型指令如下所述,分支指令(B类型)的立即数字段在S类型的基础上旋转了1位。跳转指令(J类型)的直接字段

发表于 07-27 22:25

RISC-V指令集的特点总结

开源

定义:RISC-V 是完全开源的指令集架构(ISA),意味着任何人都可以查看、使用、修改以及分发其设计,而无需支付版权费用。

优势:这种开源特性促进了全球性的创新和合作。

社区化

定义

发表于 08-30 22:05

RISC-V和arm指令集的对比分析

RISC-V和ARM指令集是两种不同的计算机指令集架构,它们在多个方面存在显著的差异。以下是对这两种指令集的详细对比分析:

一、设计理念

发表于 09-28 11:05

RISC-V指令集概述

的一大特点。

RISC-V指令集有RV32I、RV32E、RV64I、RV64E、RV64I等等,RV代表RISC-V,32/64代表32位或64位,I和E都是基本指令集,

发表于 11-30 23:30

印度确立RISC-V为国家指令集 中国CPU指令集还在孤芳自赏

目前中国CPU指令集还处在群雄割据的状态,印度就已早一步确定了“国家版”,印度将RISC-V确立为国家指令集,并将目标调整为研制6款基于RISC-V

发表于 12-19 16:58

•8206次阅读

RISC-V指令集的起源与发展历史

的大学陆续采纳为教材替代以前的MIPS和X86架构,政府和企业采纳RISC-V为标准指令集,开源的CPU核和SoC芯片不断涌现,生态环境逐渐丰富,开发者社区愈来愈活跃。

发表于 05-02 09:07

•9127次阅读

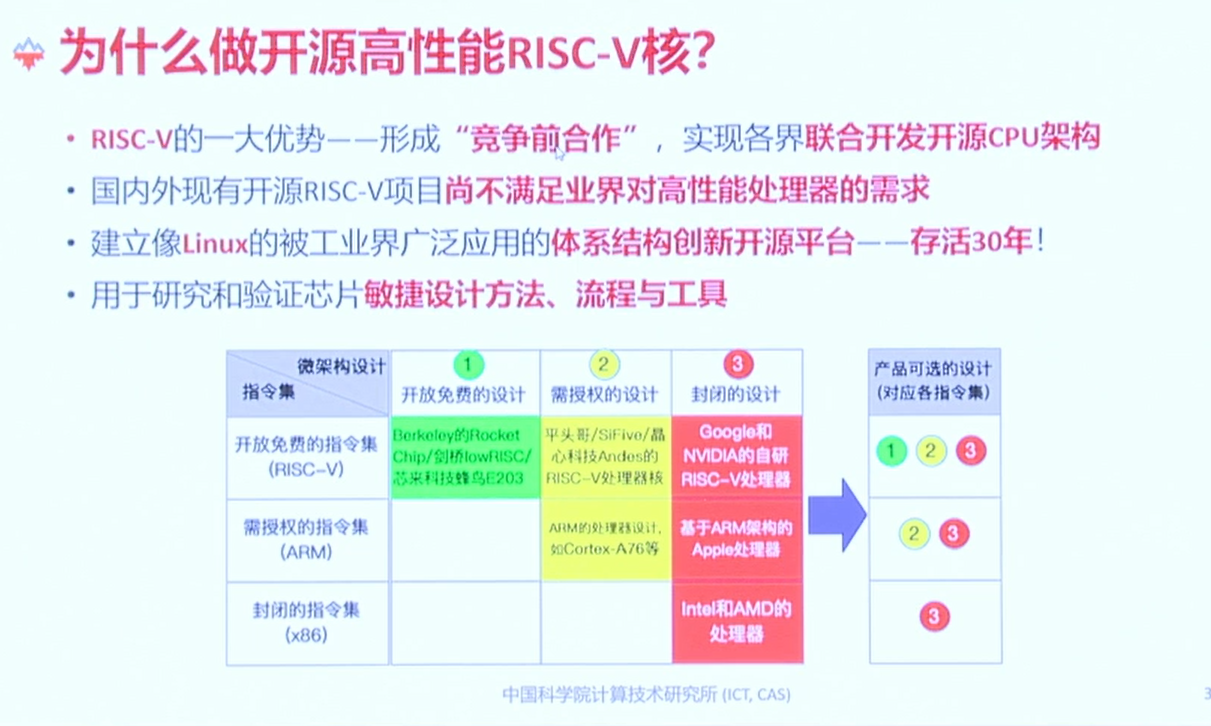

为什么做开源高性能RISC-v核,香山开源高性能RISC-V处理器开发流程

RISC-V是一个基于精简指令集原则的开源指令集架构,那么为什么做开源高性能RISC-v核?

发表于 06-22 14:25

•3496次阅读

什么是RISC-V?RISC-V指令集的优势

CPU 支持的所有指令和指令的字节级编码就是这个 CPU 的指令集架构(Instruction Set Architecture,ISA),

发表于 03-05 10:31

•2737次阅读

RISC-V核低功耗MCU指令集架构(ISA)特点

RISC-V核低功耗MCU通过开源生态、模块化架构与能效优化技术,成为物联网、穿戴设备等领域的理想选择。 一、开源与可定制性 完全开源免费:RISC-V ISA无需专利授权费用,允许开发者

基于RISC-V指令集的软核CPU在SWORD4.0上顺利移植

基于RISC-V指令集的软核CPU在SWORD4.0上顺利移植

评论