数字信号传输系统分为基带传输系统和频带传输系统.频带传输系统也叫数字调制系统。数字调制信号又称为键控信号,数字调制过程中处理的是数字信号,而载波有振幅、频率和相位3个变量,且二进制的信号只有高低电平两个逻辑量1和0,所以调制的过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制,最基本的方法有3种:正交幅度调制(QAM)、频移键控(FSK)、相移键控(PSK).根据所处理的基带信号的进制不同分为二进制和多进制调制(M 进制).多进制数字调制与二进制相比,其频谱利用率更高。本文研究了基于FPGA的MFSK(多频键控)调制电路的实现方法,并给出了MAX+PLUSII环境下的仿真结果。

1MFSK简介

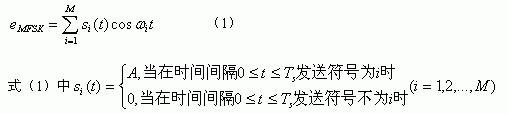

MFSK系统是2FSK(二频键控)系统的推广,该系统有M个不同的载波频率可供选择,每一个载波频率对应一个M进制码元信息,即用多个频率不同的正弦波分别代表不同的数字信号,在某一码元时间内只发送其中一个频率。MFSK信号可表示为:

为载波角频率,通常采用相位不连续的振荡频率,这样便于利用合成器来提供稳定的信号频率。图1 为MFSK系统的原理框图。在发送端,输入的二进制码元经过逻辑电路和串/并变换电路转换为M进制码元,每k位二进制码分为一组,用来选择不同的发送频率。在接收端,当某一载波频率到来时,只有相应频率的带通滤波器能收到信号,其它带通滤波器输出的都是噪声。抽样判决器的任务就是在某一时刻比较所有包络检波器的输出电压,通过选择最大值来进行判决。将最大值输出就得到一个M进制码元,然后,再经过逻辑电路转换成k位二进制并行码,再经过并/串变换电路转换成串行二进制码,从而完成解调过程。

图1 MFSK系统原理框图

2MFSK调制电路的FPGA实现

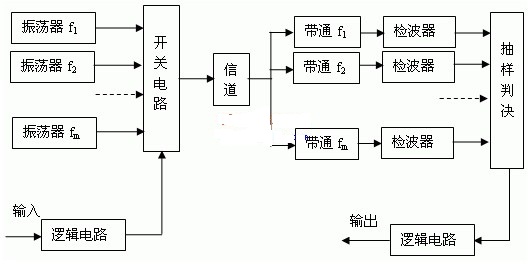

2.1基于FPGA的MFSK调制电路方框图

调制电路方框图如图2所示。基带信号通过串/并转换得到2位并行信号;四选一开关根据两位并行信号选择相应的载波输出(例中M取4)。

图2 MFSK调制电路方框图

2.2MFSK调制电路VHDL程序

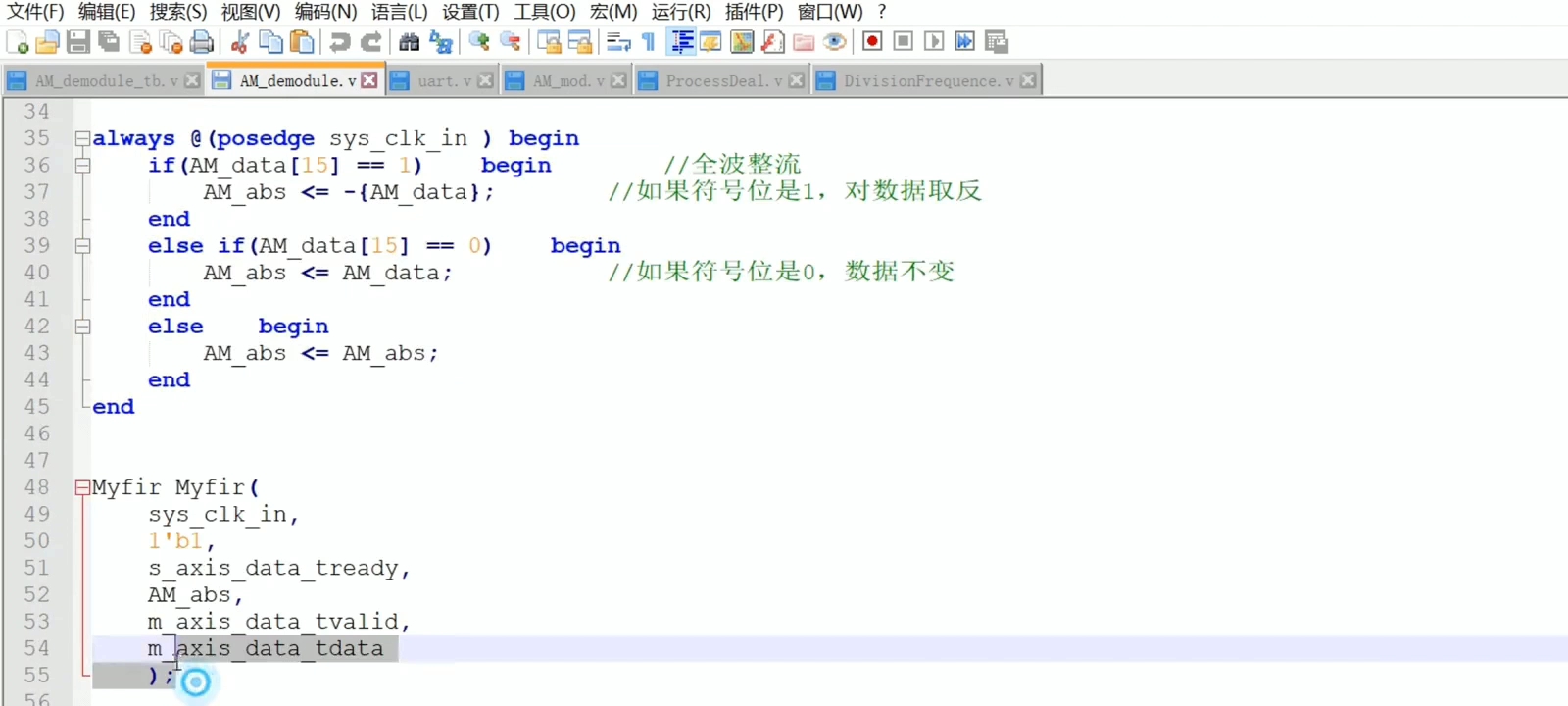

调制电路VHDL关键代码如下:

entity MFSK is

port(clk :in std_logic; --系统时钟

start :in std_logic; --开始调制信号

x :in std_logic; --基带信号

y :out std_logic); --调制信号

end MFSK;

architecture behav of MFSK is

signal q :integer range 0 to 15; --计数器

signal f :std_logic_vector(3 downto 0); --分频器

signal xx:std_logic_vector(1 downto 0); --寄存输入信号x的2位寄存器

signal yy:std_logic_vector(1 downto 0); --寄存xx信号的寄存器

begin

process(clk) --此进程过对clk进行分频,得到4种载波信号f3、f2、 f1、f0。

begin

if clk'event and clk='1' then

if start='0' then f<="0000";

elsif f="1111" then f<="0000";

else f<=f+1;

end if;

end if;

end process;

process(clk) --对输入的基带信号x进行串/并转换,得到2位并行信号的yy

begin

if clk'event and clk='1' then

if start='0' then q<=0;

elsif q=0 then q<=1;xx(1)<=x;yy<=xx;

elsif q=8 then q<=9;xx(0)<=x;

else q<=q+1;

end if;

end if;

end process;

process(clk,yy) --此进程完成对输入基带信号x的MFSK调制

begin

if clk'event and clk='1' then

if start='0' then y<='0'; -- if语句完成2位码并行码到4种载波的选通

elsif yy="00" then y<=not f(3);

elsif yy="01" then y<=not f(2);

elsif yy="10" then y<=not f(1);

else y<=not f(0);

end if;

end if;

end process;

end behav;

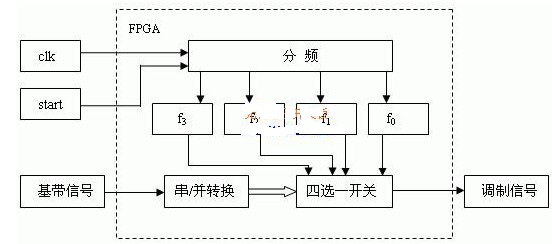

2.3仿真结果

MAX+PLUSII环境下的仿真结果如图3所示。

图3 MFSK调制程序仿真结果

注:中间信号yy与输出调制信号y的对应关系:“00”=f3;“01”=f2;“10”=f1;“11”=f0。

3结束语

多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。本文基于FPGA实现了MFSK调制电路部分,限于篇幅,没有对解调部分的电路进行讨论。在实际应用中,完全可以把调制部分和解调部分电路都集成到一片FPGA芯片内,这样即提高了FPGA内部结构的利用率,又可以降低系统的成本。

-

FPGA

+关注

关注

1655文章

22282浏览量

630078 -

噪声

+关注

关注

13文章

1154浏览量

48893 -

数字信号

+关注

关注

2文章

1044浏览量

48953

发布评论请先 登录

怎么实现基于FPGA的CDMA调制/解调模块的设计?

OOK调制解调的FPGA实现,求Verilog代码

基于FPGA 的QPSK 调制解调电路设计与实现Design

基于FPGA的MSK调制解调器设计与应用

GMSK调制解调的数字实现方法

MFSK调制电路的FPGA设计与仿真

基于VHDL的基带信号的MFSK调制

基于ofdm的调制解调原理,ofdm调制解调fpga代码

基于QPSK数字调制解调的FPGA实现

MFSK调制解调的原理及采用FPGA实现设计

MFSK调制解调的原理及采用FPGA实现设计

评论