引言

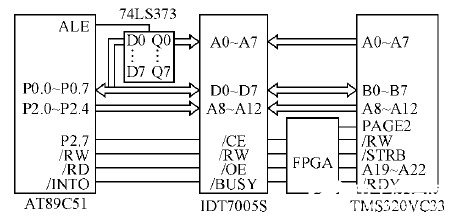

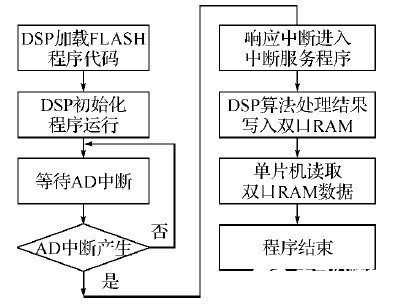

当前国际先进抗恶劣环境计算机相关产品的具有一个显着特征,即采用由超大规模FPGA实现的可定制技术,利用FPGA器件中专门设计的硬件乘法器、乘加结构、DSP块等硬件资源和通用的逻辑单元作为运算的硬件基础,以任务的流水划分和阶段处理为手段,实现CPU、DSP的计算技术的重要补充功能。国外此类超大规模FPGA以Altera Stratix-x系列、Xilinx Virtex-x系列为主,相关产品中大都为Xilinx Virtexx系列FPGA,如GE Fanuc的SBC330、SBC610和Curtiss-Wright的VPX6-185等硬件模块均采用了Xilinx Virtex-x系列FPGA,目前各家公司正在推出集成更多数量和更大规模的异构技术产品,如Curtiss-Wright的CHAMP-FX2使用了双路超大规模Virtex-5以实现功能高可伸缩的定制技术。

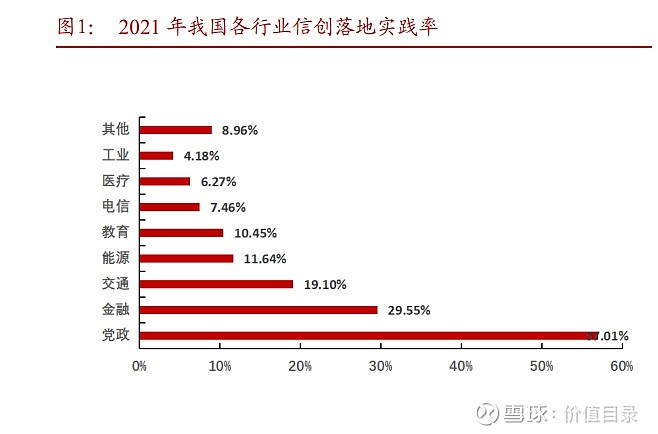

在国内,抗恶劣环境计算机产品主要以通用计算机为主,一般采用CompactPCI、VME等总线,使用1个单核或双核CPU,系统性能较低。这些计算机通用性不强、种类多、开发成本高、可重用性弱、质量保证难度大、资源利用率不高。而且这些计算机一般是使用国外的集成电路设计实现,其关键的功能核心部分仍然无法实现自主可控。

随着我国在国产基础软硬件方面的投入不断加大以及国家政策的指导,国产基础软硬件发展迅速,已接近国外同期水平。国内处理器技术的研究正不断深入,多核技术也已被纳入相应的发展路线图。中国科学院计算技术研究所于2009年底推出龙芯3号处理器,龙芯3号片内集成4个处理器核,处理器主频1GHz以上。当前,国内基于FPGA的应用已相当成熟,尽管目前的抗恶劣环境计算机没有采用可定制技术,但几乎都集成了Altera或Xilinx FPGA的应用,如功能扩展模块、总线接口模块等,国内相关厂商已掌握时序逻辑定制技术、IP核的简单复用和实现技术等FPGA 应用的关键技术,已具备较深厚的可定制实现技术基础。

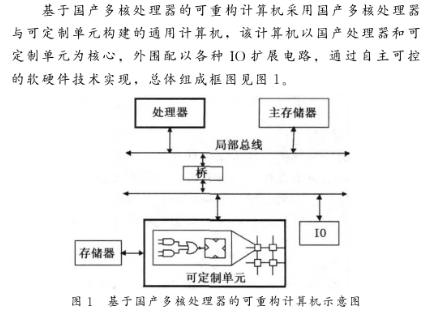

1、计算机组成原理

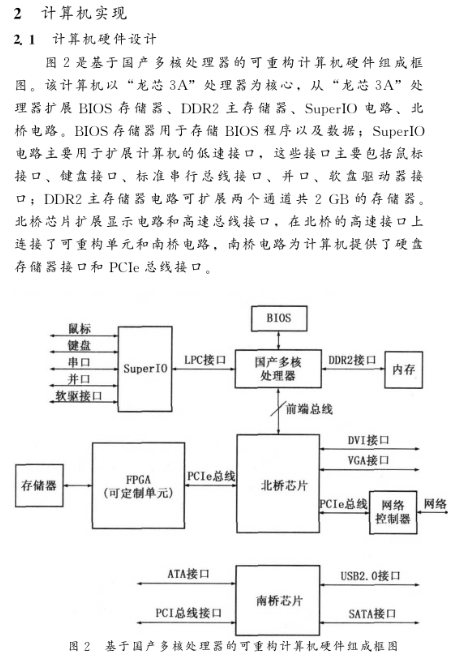

基于国产多核处理器的可重构计算机各个主要的组成功能模块之间采用高性能串行总线互连,如国产处理器与北桥芯片之间、北桥芯片与可定制单元之间、北桥芯片与南桥芯片之间均采用高速串行总线互连。可定制单元采用可编程逻辑实现,处理器和具备硬件可编程能力的可重构逻辑器件(以下简称可重构器件)相结合,应用的一部分被分配到处理器上执行,另一部分则被映射到可重构器件上执行。微处理器上执行的为软件任务,可重构器件上运行的硬件功能模块可称为硬件任务。

根据可定制单元配置文件中的编程信息,改变可定制单元中逻辑单元的功能以及连线的互连方式,从而改变计算机的功能,使其既能在设计实现时定制专用的计算部件,又能够对计算资源进行复用以实现多个不同的计算任务。

2.1.1 器件选型

计算机器件的选型不仅关系到计算机的整体性能,更重要的是,直接影响到潜在用户目标系统在开发时硬件设计的复杂度。因此在完成预期功能要求的前提下,计算机元器件的选型应该充分的考虑计算机的应用环境,如元器件工作与存储的温度范围等。

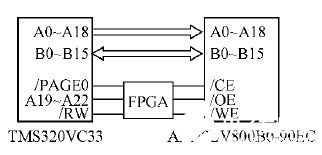

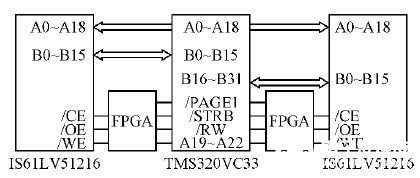

2.1.2 内存设计

龙芯3A处理器上集成2个DDR2通道,每个通道支持的容量为1GB,两个通道共2GB.每个通道采用8颗16位位宽1GB的内存颗粒,两个通道共16颗内存颗粒。其中,CLK0、2一组,CLK1、3一组,即颗粒1、2一组时钟,颗粒3、4一组时钟。特别注意:颗粒的锁相环电源及地需用磁珠进行隔离。通道的内存颗粒连接示意图如3所示。

2.1.3 电源设计

本设计的电源能够提供12V、5V的电压。其它种类电压依照不同的电流需求由电源模块或LDO等提供。系统的上电启动过程,可各路电源同时上电,也可配置处理器I/O、处理器核电压、南桥核电压、北桥核电压的上电顺序。

图3 内存颗粒连接示意图

2.1.4 时钟设计

设计中选用时钟芯片SLG8LP625T来产生处理器HT差分时钟200 MHz,北桥的PCIE及HT 差分时钟100 MHz、14.318MHz,南桥的A-LINK 差分时钟100MHz、14.318MHz、48MHz,4个PCIE网络控制器的差分时钟100MHz,SuperIO的48MHz.处理器的HT差分时钟为做兼容设计采用200 MHz的有源晶振。挂在南桥PCI总线上的PCI桥PLX6254、IDE控制器SiI0680、SuperIO所需的33MHz时钟由南桥输出。处理器的PCI、BIOS时钟33MHz由有源晶振及时钟Buffer输出,系统时钟、内存时钟所需的25MHz由有源晶振输出。4个网络控制器所需25 MHz由Crystal输出。SATA时钟25MHz,RTC时钟32.768kHz由Crystal输出。PCI桥PCI6254时钟66MHz由有源晶振输出。

2.1.5 其它设计

由于整个系统不需要ACPI电源管理,故设计中不分S5及S0状态的电源,但必要的上电先后顺序需要满足。处理器上电时序:当系统上电时,即由CPCI槽供5V、12V电源,处理器核电压由3.3V的POWERGOOD作为使能信号产生,满足要求的上电时序。系统启动时序:南北桥核电压的POWERGOOD信号经MAX708延时200ms后输出到南北桥芯片,延时信号的上升沿作为触发信号输出到南桥使整个系统启动。延时信号SB_NB_PWRGD与南北桥复位信号MASTER_RST/经与门后作为处理器的复位信号。南桥的LDT _PG、LDT_RST分别作为HT_POWEROK、HT_RST接到处理器,以满足HT总线的上电时序。南桥的PCI_RST作为南桥PCI总线的复位信号。南桥的A_RST作为全局复位信号复位IDE控制器、网络控制器、北桥等设备。系统复位时序:复位按钮可控制整个系统的复位。当系统作为CPCI槽上的从设备时,槽上引入的复位信号可对整个系统复位。

2.2 可重构设计

基于国产多核处理器的可重构计算机的FPGA 配置优化和在线重配置如图4所示。它能够在计算任务运行的同时对可重构器件上的逻辑资源进行重构。计算任务被划分为多个配置文件,每次在可重构器件上加载的配置文件与计算任务中的一个部分相对应,因此在计算任务的执行过程中需要对可重构器件进行多次重构。

图4 FPGA配置优化和在线重配置示意

基于国产多核处理器的可重构计算机设计流程如图5,一个应用首先要进行软件、硬件划分,决定应用的什么部分用软件实现,什么部分用硬件实现。在软、硬件划分时,通常将控制过程的功能模块由软件实现,将数据计算密集型的功能模块由硬件来实现。在软、硬件划分后,就将软件任务映射到微处理器,硬件任务映射到可定制单元(FPGA)。在任务的划分阶段采用非重叠功能调度、自动化建模(硬件任务划分、映射)技术、可重构硬件虚拟抽象等手段实现可重构计算。

图5 基于国产多核处理器的可重构计算机设计流程

2.3 基于国产多核处理器的可重构计算机的IP核设计

IP设计首先是进行规格的定义,根据规格提出功能需求后,建议软硬件的协同仿真环境后进行子模块的设计实现,具体的设计流程见图6.

基于国产多核处理器的可重构计算机的构件及IP核集成和测试是为了保证设计实现提供的功能的正确性,保证功能与设计规格的一致性。通过研究掌握当前主要的验证手段和验证策略,形成一套成体系的设计流程。

2.4 基于FPGA的计算加速设计

以国产多核处理器和可定制单元为载体,采用多核虚拟化、FPGA算法加速、负载均衡、共享数据一致性等技术,在通过FPGA对计算加速和异构多处理数据层次之间进行强实时传递的基础上,实现可定制异构多处理架构,重点解决计算加速问题。可定制异构多处理架构如图7.

3 、结束语

基于国产龙芯3A处理器的CPCI计算机模块的研制,不仅实现核心技术国产化,消除使用国外产品的安全隐患,摆脱受制于人的不利局面,而且随着龙芯处理器的更新换代,龙芯3A处理器是目前国产处理器中性能最高的芯片,4个核心处理器,每个核主频可到800MHz左右,基于国产多核处理器的可重构计算机采用国产多核处理器和FPGA实现,具有良好的计算性能。

图6 IP核设计流程

责任编辑:gt

-

处理器

+关注

关注

68文章

20148浏览量

247132 -

FPGA

+关注

关注

1655文章

22283浏览量

630277 -

计算机

+关注

关注

19文章

7764浏览量

92681

发布评论请先 登录

迅为3A6000_7A2000核心主板龙芯全国产处理器LoongArch架构

迅为3A6000_7A2000开发板龙芯全国产处理器与龙芯 3A5000完全兼容

【悬赏100块】如何实现FPGA可重构计算(Android平台)

星载可重构计算机硬件验证平台设计

龙芯3A4000处理器实测 未来或将达到主流桌面处理器可用的水平

龙芯3A4000处理器的性能测试,相同主频性能提升幅度超过100%

龙芯芯片出货量突破50万颗,3A/3B5000系列主频可提升2.5GHz以上

龙芯3C5000 16核处理器全国产工业计算机模块成功上市

基于国产龙芯3A处理器和FPGA器件实现可重构计算机的设计

基于国产龙芯3A处理器和FPGA器件实现可重构计算机的设计

评论