TMS320F2812/F2811/F28lO/C2812 /C2811/C2810处理器要求采用双电源(1.8 V或1.9 V和3.3 V)为CPU、Flash、ROM、ADC以及I/O等外设供电。为了保证上电过程中所有模块具有正确的复位状态,要求处理器上电/掉电满足一定的次序要求。

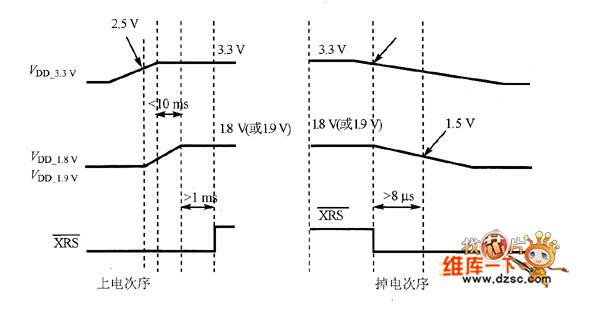

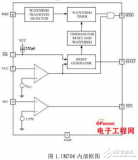

为满足系统上电过程中相关引脚处于确定的状态并简化设计,首先应保证所有模块的3.3V电压(包括VDDIO、VDD3VFL、VDDA1/VDDA2/VDDAIO/AVDDREFBG)先供电,然后提供1.8 V或1.9V电压。要求在VDDIO电压达到2.5 V之前,1.8 V或1.9 V(VDD/VDD1)的电压不能超过0.3 V。只有这样才能够保证在上电过程中,所有I/O状态确定后内核才上电,处理器模块上电完成后都处于一个正确的复位状态。上电次序如图1所示。

图1 281x处理器上电/掉电次序时序

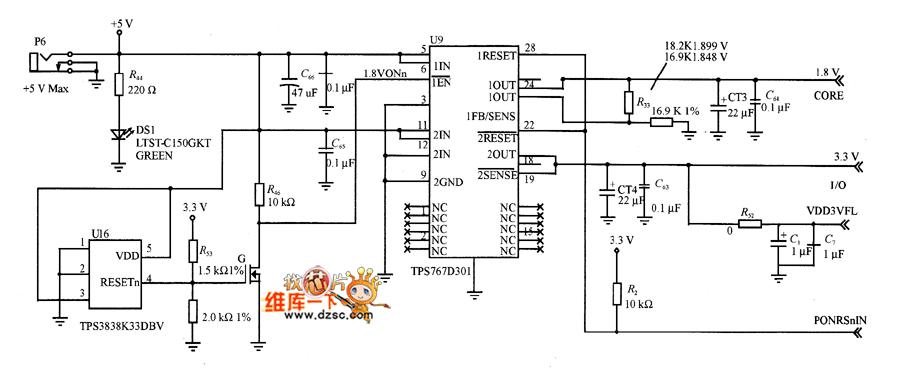

掉电过程中,在VDD降低到1.5 V之前,处理器的复位引脚必须插人最小8 μS的低电平。这样有助于在VDDIO/VDD掉电之前,片上的Flash逻辑处于复位状态。因此,电源设计时一般采用LDO的复位输出作为处理器的复位控制信号。供电原理如图2所示。

图2 281x处理器供电原理图

-

TMS320F2812

+关注

关注

8文章

175浏览量

41014 -

TMS320C2812

+关注

关注

0文章

4浏览量

11490 -

VDD

+关注

关注

1文章

318浏览量

36768

发布评论请先 登录

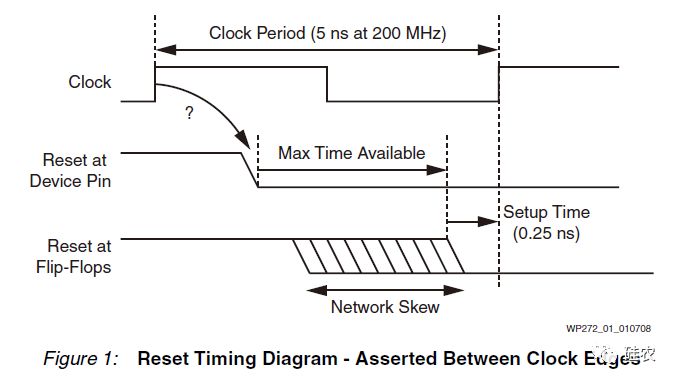

基于Xilinx FPGA的复位信号处理

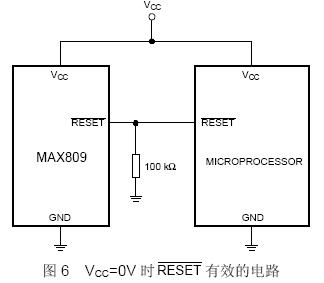

如何确定微处理器复位阈值

MAX809/MAX810 三管脚的微处理器复位芯片

MAX809/MAX810中文资料 (微处理器复位芯片)

集成复位的LDO使用指南

可调滞后的微处理器复位芯片MAX6383

TCM811/TCM812 微处理器复位监控器

lm3702/lm3703微处理器监控电路输出和手动LowLine复位

采用LDO的复位输出作为处理器的复位控制信号

采用LDO的复位输出作为处理器的复位控制信号

评论