代码解析

LTC2308通过一个标准4线SPI数字接口进行通信。LTC2308模数转换芯片有8个ADC通道和12位的分辨率,输入信号时钟频率范围不超过500KHz,按照Nyquist采样定理则建议输入信号在250KHz以下。

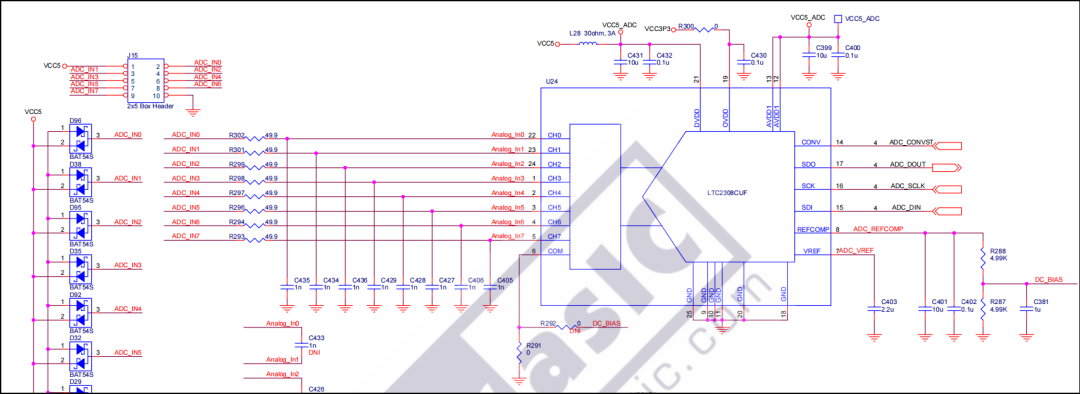

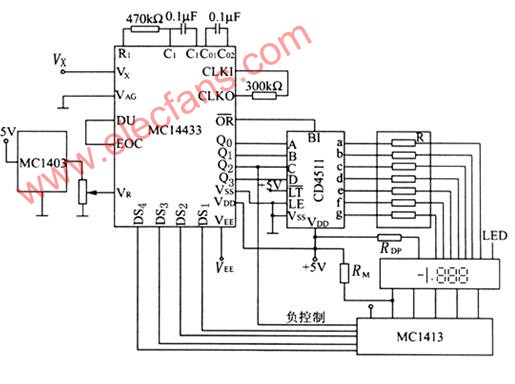

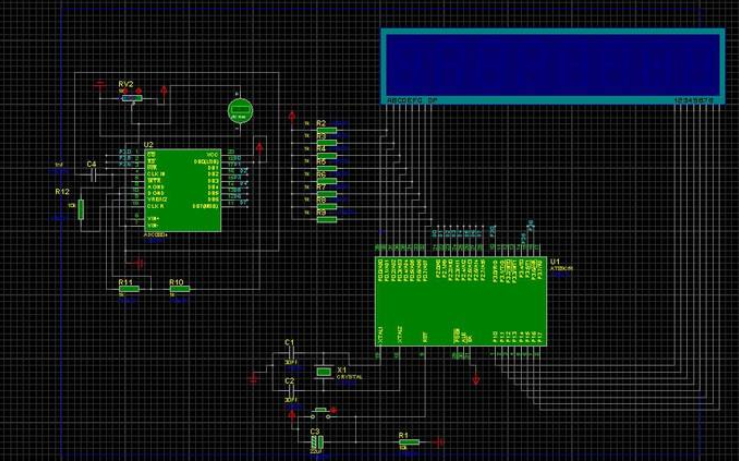

以下是DE10-Standard开发板上的LTC2308电路:

从电路图可知,LTC2308的COM引脚接GND,代表当前DE10-Standard开发板上的LTC2308被固定为单极性输入。

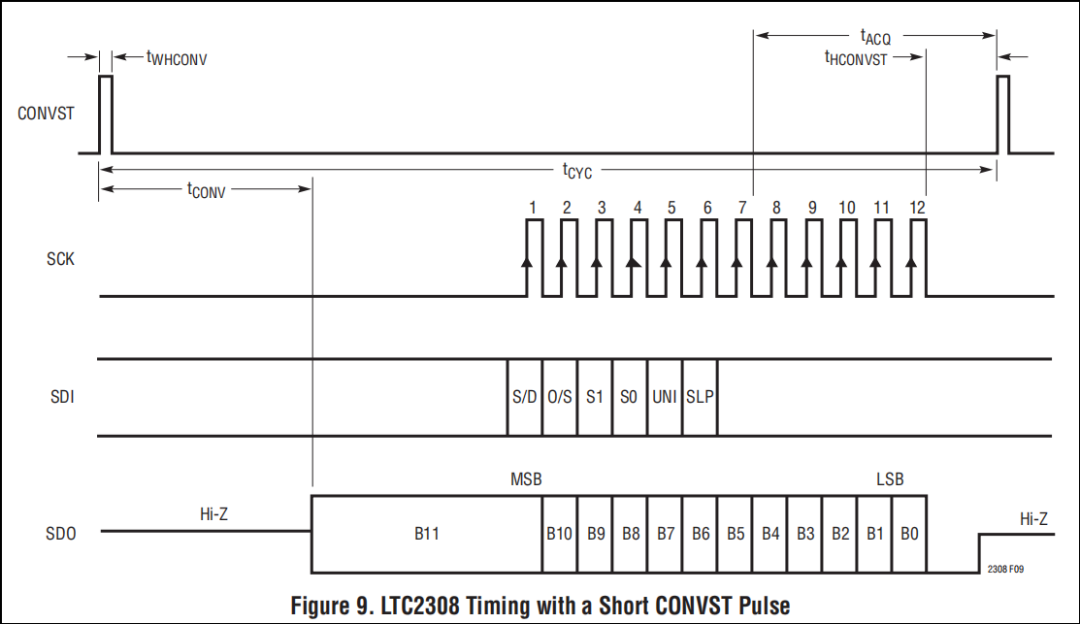

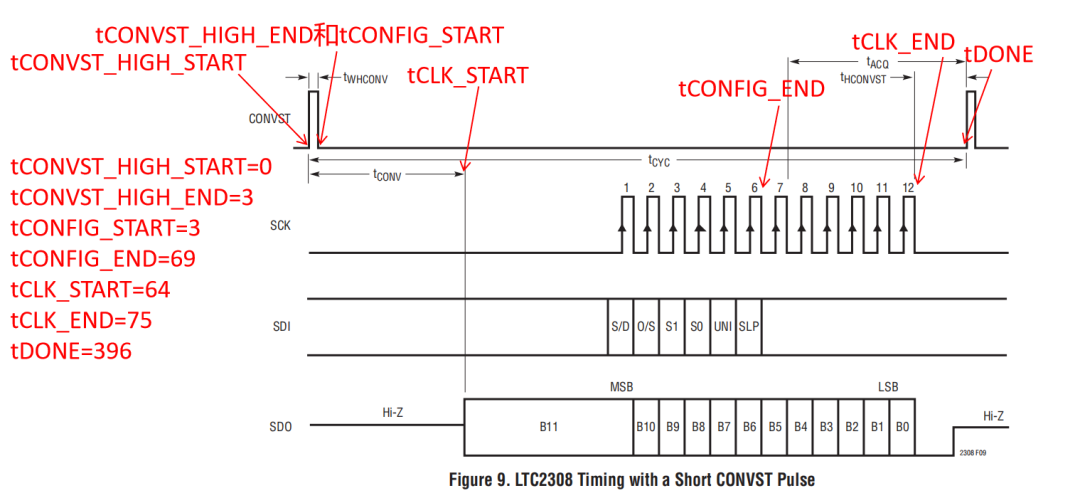

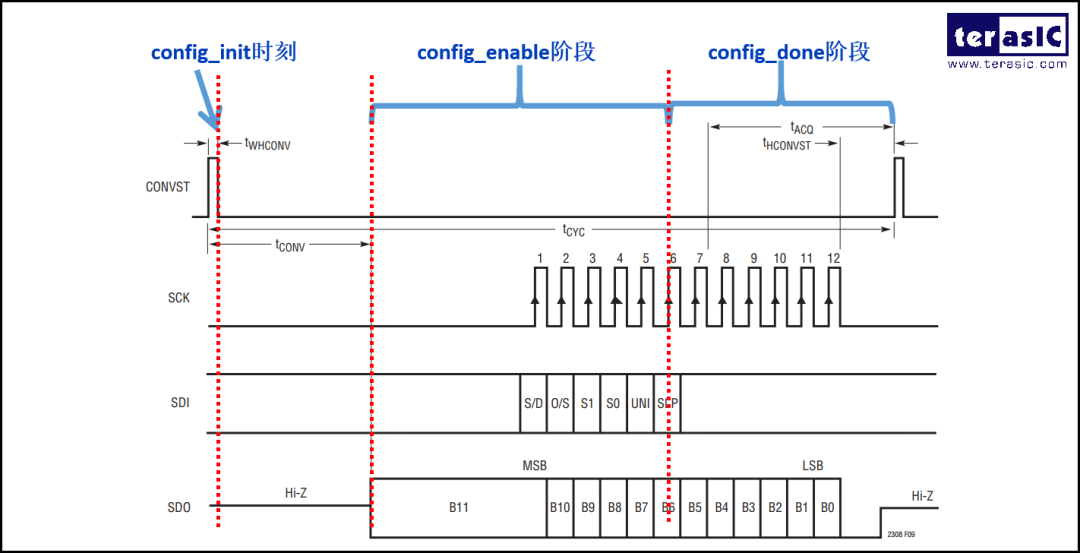

LTC2308的SPI协议时序图如下:

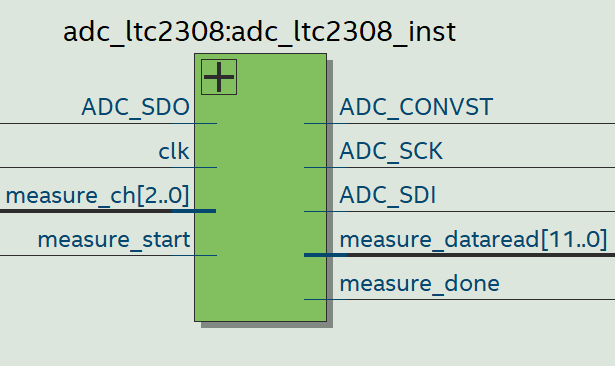

LTC2308控制模块(adc_ltc2308.v)框图如下:

信号列表如下:

模块参数设计:

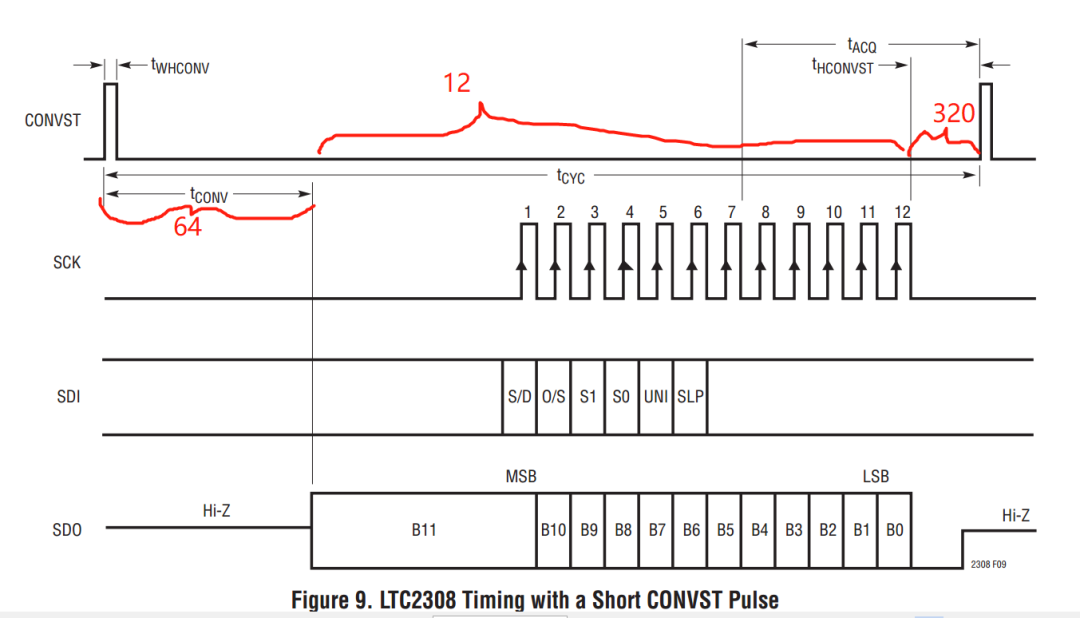

DE10-Standard开发板手册(DE10-Standard_User_manual.pdf)提到如果想设置采样率100Ksps,只需设置tHCONVST 为 320即可。接下来看看320这个数值是如何计算出来的。

根据LTC2308数据手册我们知道其最高采样率是500ksps, SCK最高能达到40MHz, tCONV 的典型值是1.3 us,最大值是 1.6 us。100Ksps的时间周期是10us,40MHz的时间周期是25ns。一次整个过程(包括转换和采样)要占用10us/25ns=400 个周期。1.6us/25ns= 64, 那么tCONV 最多占用64个时钟周期。

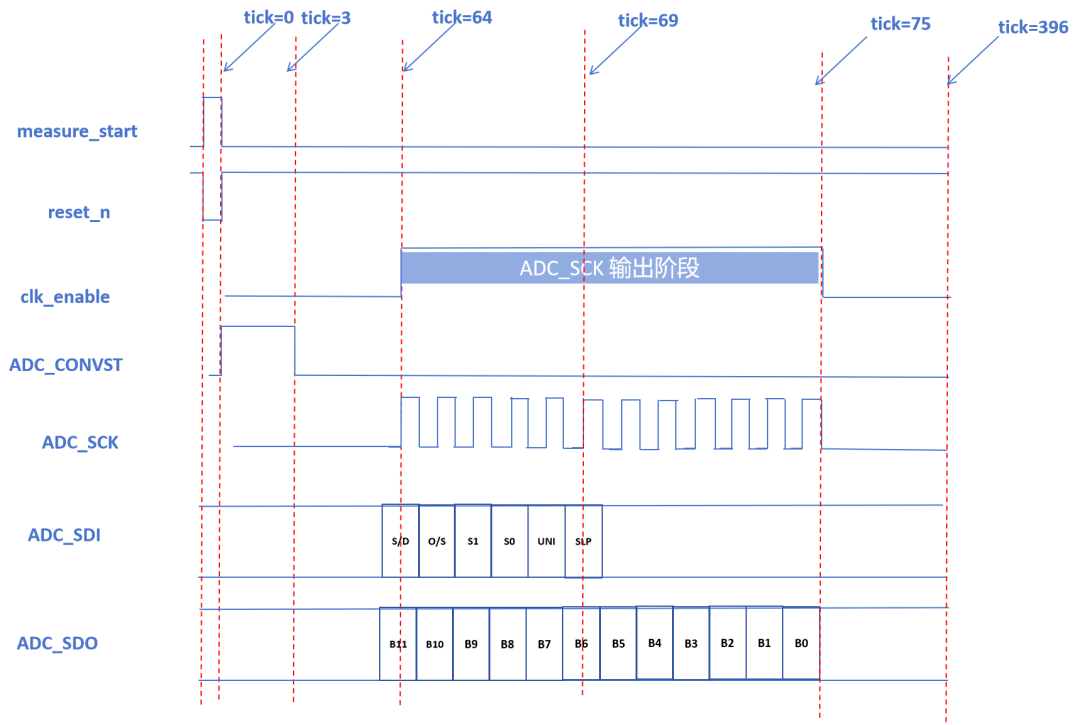

根据时序图和代码来看,64+12+320=396大约是400 。

adc_ltc2308.v代码里面参数设定如下:

代码详解:

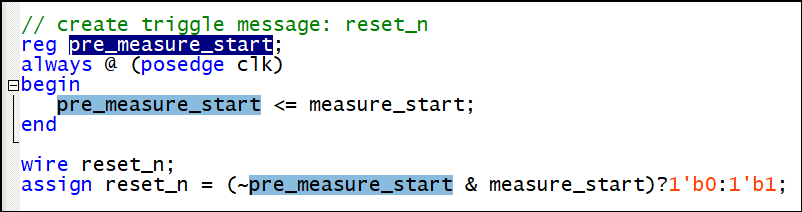

一旦检测到触发信号measure_start的上升沿,adc_ltc2308 模块的系统复位信号就置0:

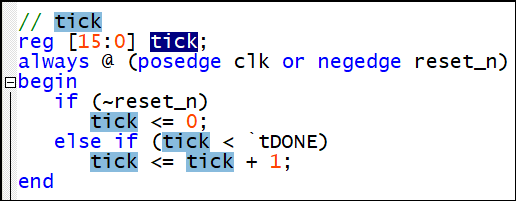

设计一个计数器,对LTC2308的一次完整转换和采集过程所需的时钟周期数进行数节拍:

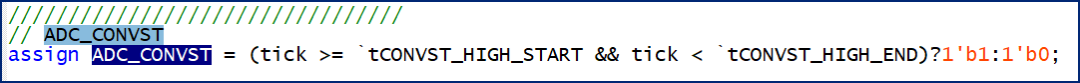

输出ADC_CONVST信号(也就是标记出tWHCONV时间段):

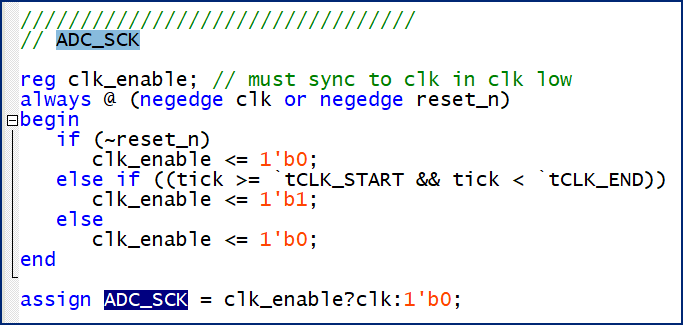

输出SCK时钟,ADC_SCK周期为40MHz,但每一次只有12个周期输出,其他时间输出低电平0 :

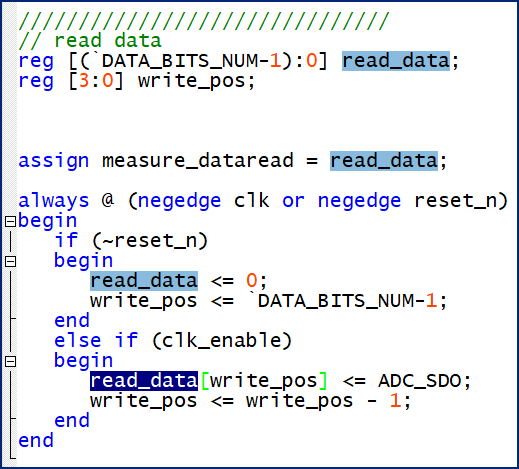

在clk下降沿时刻,将转换完成的数据写入到到寄存器中:

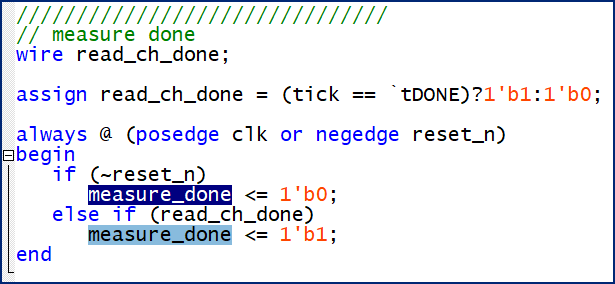

measure_done是一次采集完成标志,每次检测到LTC2308的触发信号上升沿时measure_done信号归0,当一次采集完成后置1:

measure_done是一次转换+传输+采样完成的标志,measure_done信号在开始新一轮采样后清0,当传输完成后置1:

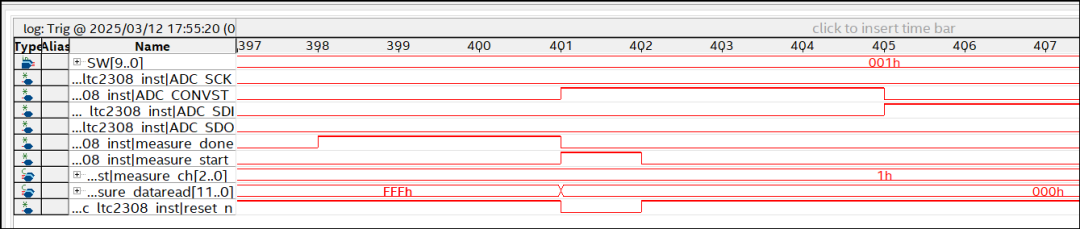

reset_n、clk_enable、measure_done、ADC_CONVST和ADC_SCK信号波形标出如下:

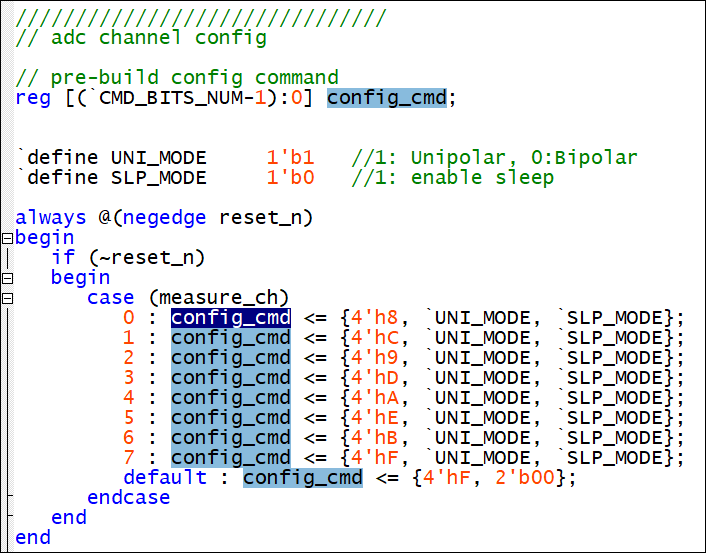

根据输入(measure_ch)的通道选择不同的配置字存储到寄存器config_cmd:

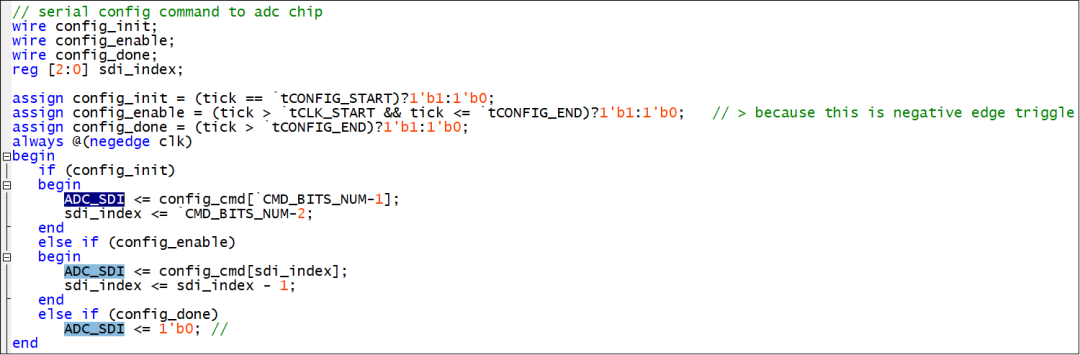

然后根据LTC2308的时序图标记出配置字的三个阶段(三个状态):config_init(配置初始化时间段) 、config_enable(可配置时间段) 和 config_done(配置完成时间段)。

config_init(配置初始化时间段):初始状态下,将配置字的高字节赋给ADC_SDI

config_enable(可配置时间段):将配置字剩余的5个bit逐个赋给ADC_SDI

config_done(配置完成时间段):配置完成阶段将0赋给ADC_SDI

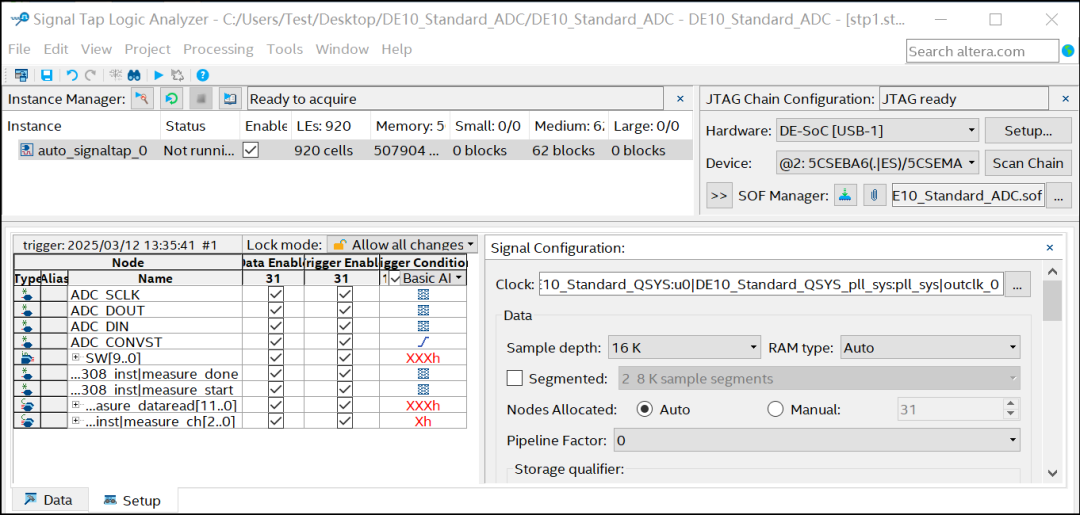

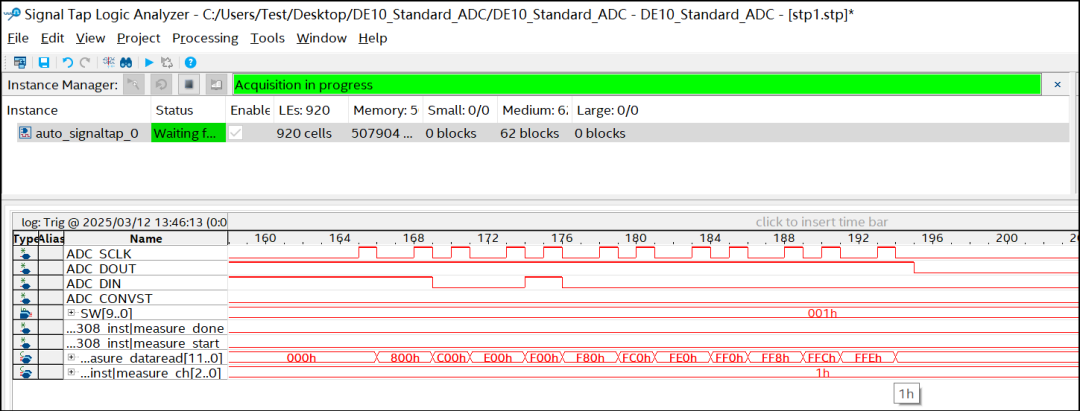

打开~DE10_Standard_ADCstp1.stp 文件(关于Signaltap调试工具的使用请参考之前的推文:SDRAM读写),采样时钟设置的是PLL outclk_0输出的100M,ADC_CONVST作为触发信号:

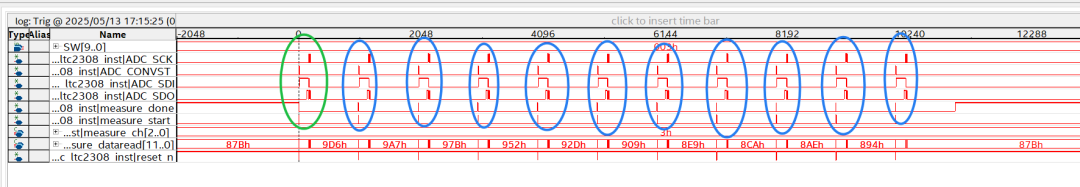

可得到 LTC2308控制模块(adc_ltc2308.v)内部信号的波形如下。

测量11次,第一次的数据忽略, 取后面10次的数据:

ADC_CLK 输出12个时钟周期:

若 stp1.stp 文件采样时钟设置为PLL outclk_1输出的40M,则波形细节如下:

ADC_CONVST占用4个时钟周期(tick=0、1、2、3):

-

FPGA

+关注

关注

1655文章

22280浏览量

630047 -

接口

+关注

关注

33文章

9443浏览量

156108 -

adc

+关注

关注

100文章

7377浏览量

553672 -

引脚

+关注

关注

16文章

2085浏览量

55114 -

SPI协议

+关注

关注

0文章

23浏览量

8785

原文标题:05-基于FPGA和LTC2308的数字电压表设计-用FPGA实现SPI协议通讯

文章出处:【微信号:友晶FPGA,微信公众号:友晶FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

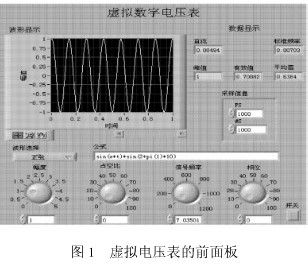

数字电压表的设计

基于LabVIEW8.2的虚拟数字电压表的设计和实现

如何使用FPGA实现数字电压表的设计

基于FPGA的SPI协议及设计实现

数字电压表设计教程之使用FPGA实现SPI协议通讯

数字电压表设计教程之使用FPGA实现SPI协议通讯

评论