概述

MAX9176/MAX9177是670MHz低抖动、低扭曲的2:1多路复用器,尤其适合于保护切换、环回、时钟和数据分配。这些器件具有68ps的超低峰峰值系统抖动,保证在那些定时误差极为敏感的高速链路中可靠工作。

数据表:*附件:MAX9176多路复用器技术手册.pdf

MAX9716具有安全失效的LVDS输入和LVDS输出。MAX9177接收任何差分输入(CML/LVDS/LVPECL),提供LVDS输出。控制掉电输入,可以将输出置为高阻。当输入处于开路、无驱动短路或无驱动终端匹配时,MAX9176的安全失效电路驱动输出为高电平。MAX9177具有偏置电路,在输入开路时驱动高电平输出。多路复用选择端和掉电输入兼容于标准的LVTTL/LVCMOS逻辑。

多路复用选择端与掉电输入端可以承受-1V的下冲和VCC + 1V的过冲。MAX9176/MAX9177提供10引脚µMAX和10引脚薄型QFN封装,工作于3.3V单电源,工作温度范围-40°C至+85°C。

应用

- 时钟分配

- 环回

- 保护开关

特性

- 670MHz时,最大1.0ps

(RMS)抖动 - 800Mbps数据速率时,最大68ps

(P-P)抖动 - 3.3V工作电源

- LVDS安全失效输入(MAX9176)

- 任意输入电平(MAX9177)包括差分CML/LVDS/LVPECL

- 选择输入端和掉电输入端能够承受-1.0V至V

CC+ 1.0V的电压 - 低功耗CMOS设计

- 10引脚µMAX和QFN封装

- -40°C至+85°C工作温度范围

- 符合ANSI TIA/EIA-644 LVDS标准

- IEC 61000-4-2第4级ESD保护

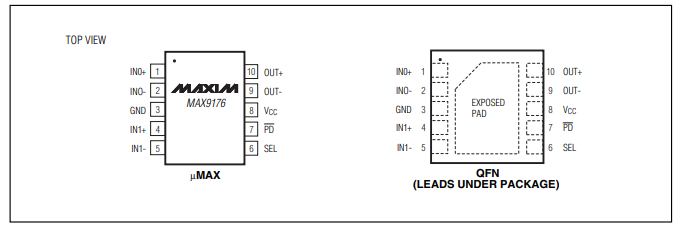

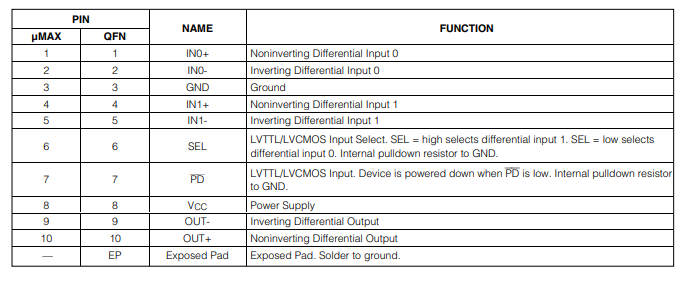

引脚配置描述

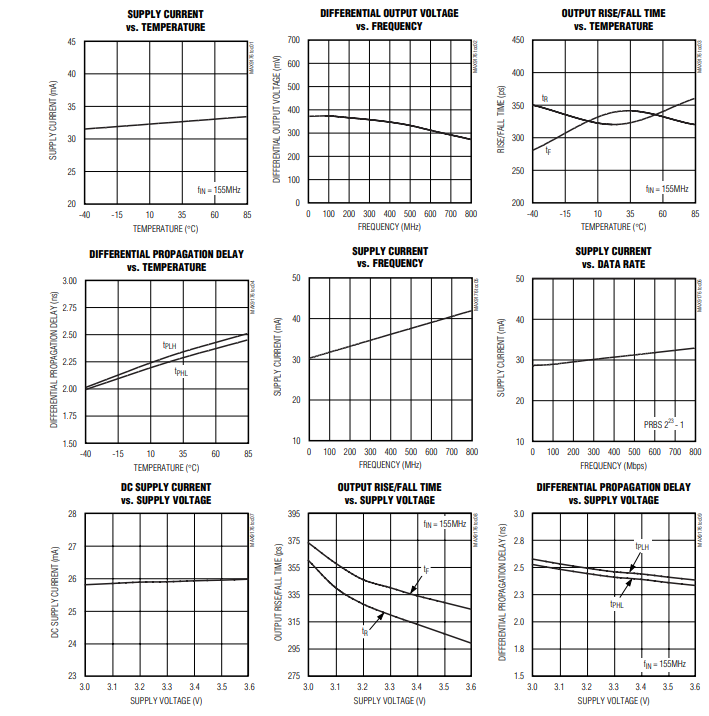

典型操作特性

应用信息

电源旁路

将 VCC 引脚通过表面贴装的 0.1μF 和 0.001μF 高频陶瓷电容旁路至地,尽可能靠近器件,较小容值的电容更靠近 VCC 引脚。

差分走线

MAX9176/MAX9177 的输入和输出走线特性会影响其性能。使用受控阻抗的差分走线(典型值为 100Ω),以减少辐射噪声并确保紧密耦合。为实现共模信号传输,将差分信号对紧密布线在一起。通过匹配差分对的电气长度来减少偏斜。导致差分对出现过大偏斜的两条信号路径会降低磁场抵消效果。保持差分走线之间的距离恒定,以避免阻抗不连续。尽量减少过孔数量,防止出现阻抗不连续情况。

电缆和连接器

LVDS 的互连通常采用受控差分阻抗为 100Ω 的电缆和连接器。使用具有匹配差分阻抗的电缆和连接器,以最大限度减少阻抗不连续情况。避免使用带状电缆或简单同轴电缆等不平衡电缆。双绞线对之类的平衡电缆信号质量更好,且由于磁场抵消效应,往往产生较少的电磁干扰(EMI)。LVDS 接收器所需的平衡电缆应拾取共模信号。

端接

MAX9176/MAX9177 需要外部输入和输出端接电阻。对于 LVDS,在每条差分线路上靠近 LVDS 驱动端的位置连接一个端接电阻。将输入端接电阻尽可能靠近接收器输入。端接电阻应与传输线的差分阻抗匹配。使用 1% 精度的表面贴装电阻。

MAX9176/MAX9177 集成了差分输出电阻。该电阻通过抑制传输线与线路远端端接电阻之间的反射来减少抖动。

电路板布局

将差分信号和单端信号分开,以减少串扰。建议使用四层印制电路板,将差分信号与逻辑信号分开,电源层和接地层分开,以获得最佳效果。

IEC 61000 - 4 - 2 4 级静电放电(ESD)保护

IEC 61000 - 4 - 2 标准(图 10)规定了电子系统的 ESD 容限。IEC61000 - 4 - 2 模型指定了一个 150pF 电容器,通过器件内的 330Ω 电阻放电。MAX9176/MAX9177 的差分输入和输出的额定值符合 IEC61000 - 4 - 2 4 级标准(接触放电 ±8kV,空气放电 ±15kV)。人体模型(HBM,见图 9)规定一个 100pF 电容器通过 1.5kΩ 电阻向器件放电。

由于 IEC 61000 - 4 - 2 放电具有更高的峰值电流和更多能量(因其串联电阻更低、电容更大),相比 HBM 更需关注。

-

复用器

+关注

关注

1文章

794浏览量

29684 -

lvds

+关注

关注

2文章

1216浏览量

69109 -

多路复用器

+关注

关注

9文章

993浏览量

66615

发布评论请先 登录

AD8185缓冲模拟多路复用器

AD8174缓冲模拟多路复用器

组合逻辑基础之多路复用器设计

模拟开关和多路复用器的基础参数

MAX4638,MAX4639低电压模拟多路复用器

MAX4617-MAX4619低电压、CMOS模拟多路复用器/开关

MAX9176多路复用器技术手册

MAX9176多路复用器技术手册

评论