简单的路灯自控电路图(一)

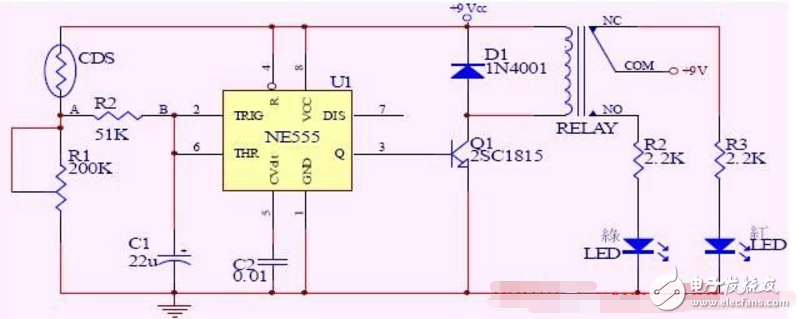

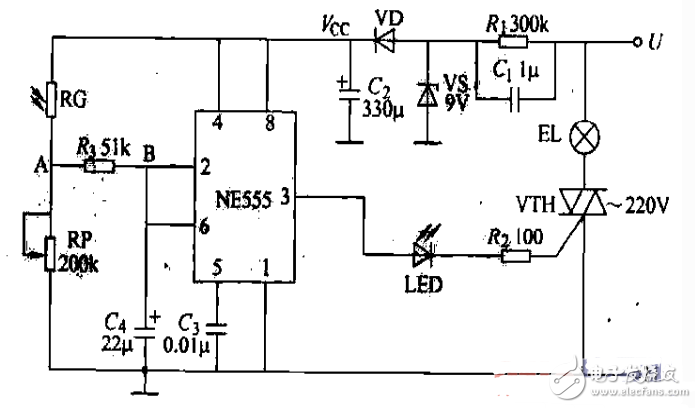

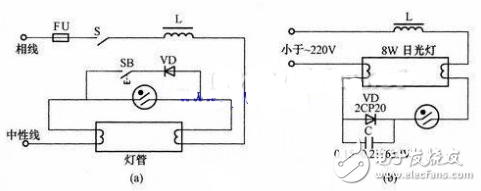

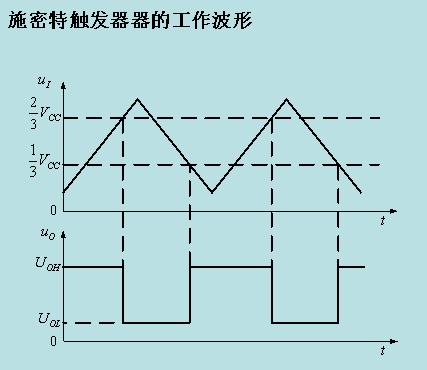

如图1所示。当光照度逐渐减弱,光敏电阻的电阻值逐渐增大,A点电压随Cds的增大而降低,B点电压亦随之下降。当B点电压降至IC的下限电压VIL即1/3VCC时,IC的第三脚输出由原来的低电位变为高电位,推动三极管C、E导通,使得原本是NC继电器切换到NO绿灯亮起。如果此时光照度的波动引起B点电压在1/3VDD上下波动,因不能达到2/3VDD,即IC 的上限电压VIH,所以IC的第三脚输出保持不变,即使此时偶然强光(例如:闪光灯)照射光敏电阻Cds引起A点电压突然高于2/3Vcc,因A点对C1充电,所以B点电压不能突然改变,IC的第三脚输出仍然保持不变。

图1 光控路灯自动控制电路图

直到第二天的黎明来临时,光照度逐渐增强,Cds阻值逐渐减小,A点电压随Cds阻值减少而上升,B点电压也随之上升,当B 点电压升至IC的上限电压VIH,即2/3Vcc 时,IC的第三脚输出由原来的高电位变为低电位,使得三极管C、E间断路,继电器由NO切回到NC红灯亮起。如果此时光度的波动引起B点电压在2/3Vcc上下波动,因不能达到1/3Vcc,即IC的下限电压,所以IC的第三脚输出保持不变。

简单的路灯自控电路图(二)

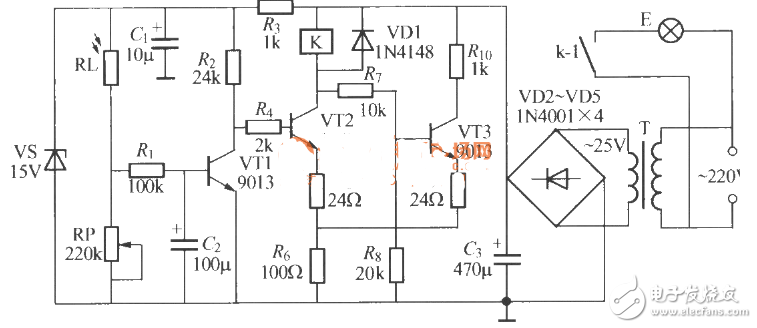

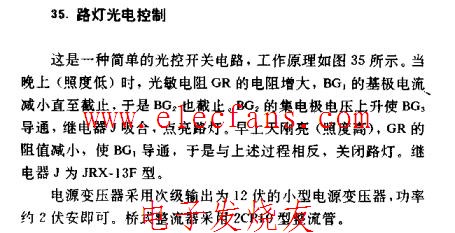

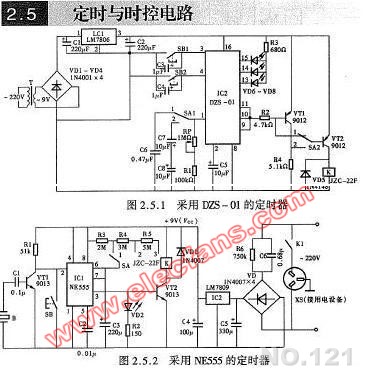

如图所示是一个性能良好的光控自动路灯电路,它具有灵敏度高、性能稳定和抗干扰性能好等特点。图中,R1、C1组成干扰脉冲吸收电路,可防止夜间短暂光线照射或白天落叶、飞纸等短暂遮挡等因素使电路发生误动作。T采用220V/25V、25VA优质电源变压器,要求长时间通电不发热。K可采用JQX-13F、DC24V触点容量为AC220V、15A中功率电磁继电器。

简单的路灯自控电路图(三)

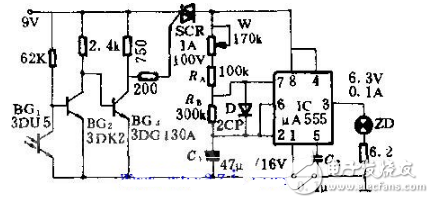

白天由于光线充足,BG3导通,SCR阻断,由IC等构成的振荡电路无电压不能工作,故指示灯不亮。夜晚,由于BG3截止,SCR受触发而导通,所以由IC等构成的振荡电路启振,IC的3不断输出超低频方波,其频率f=1/T=1.44/(W+Ra+2Rb)·C,可看到IC的3与地间所接的指示灯一闪一闪发光,十分醒目。调整Ra·Rb成C1的大小可改变闪光的频率。

简单的路灯自控电路图(四)

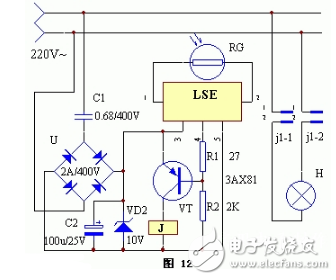

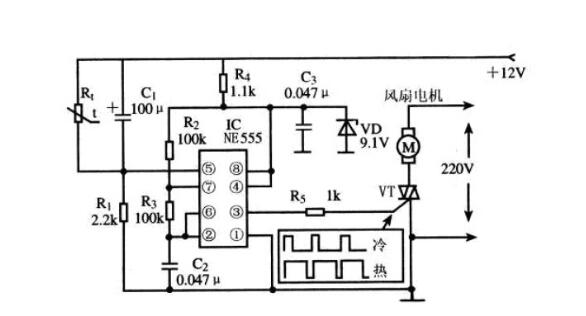

该装置的电路工作原理见图12。白天当有较强的光线照射在光敏电阻RG上时,RG的内阻很小,相当于LSE的①、②脚间串通,此时LSE的④脚输出高电平,三极管VT截止,继电器J释放,路灯H无电源熄灭。一旦夜幕降临,外界的光线很弱,RG的内阻上升,相当于LSE的①、②脚阻断,故LSE的④脚变为高电平,三极管VT导通,J励磁吸合,常开触点j1-1、j1-2闭合,照明灯H获得电源而点亮。

简单的路灯自控电路图(五)

路灯安装一般采用地沟穿管暗敷布线的方法。控制部分安装在大门口或在电工房值班室内统一控制。某厂区内的路灯如图a所示。它除了方便交通外,也是人们在公路两旁休闲、散步、游玩、锻炼身体的地方。

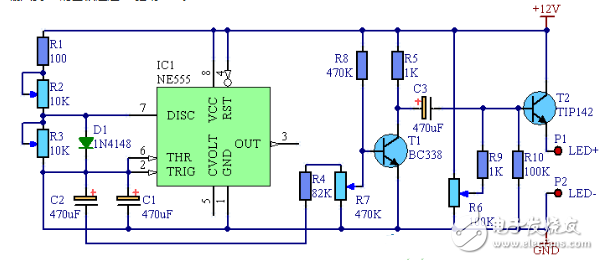

光控路灯电路的工作原理:光控路灯的特点是具有工作稳定、可靠,不会因偶然的强光照射而引起误动作或闪烁。

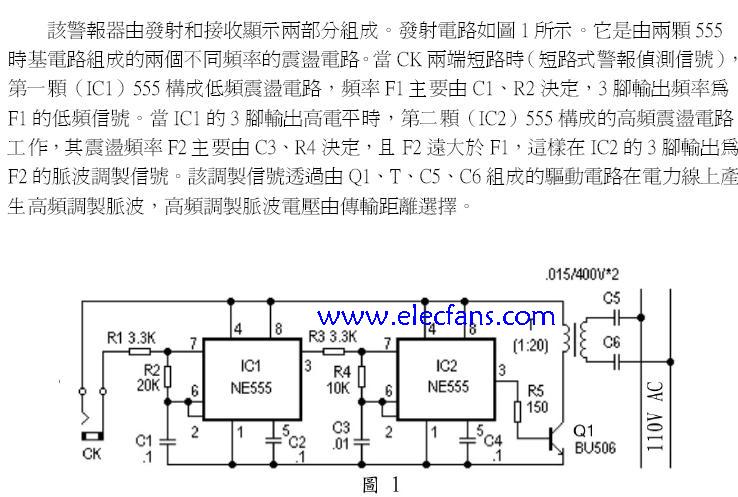

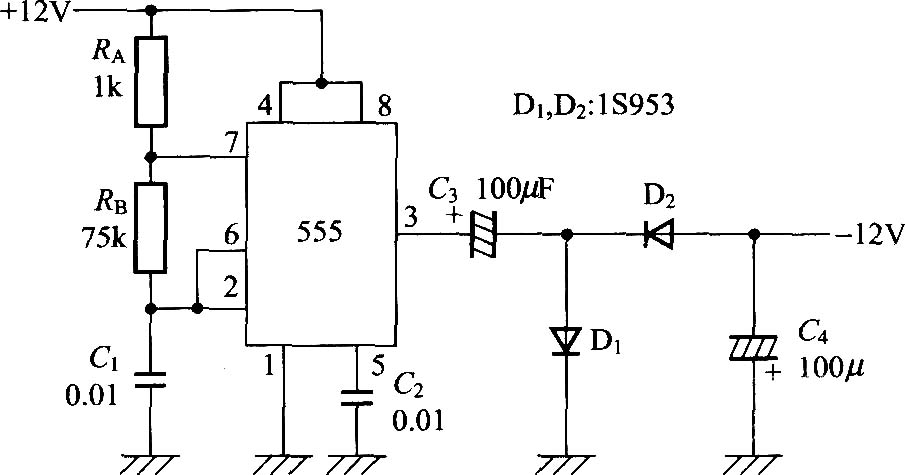

该光控路灯电路由光控触发器电路、开关电路和电源电路组成,如图16-45b所示。光控路灯电路中,光控触发器电路由光敏电阻器RG.电位器RP、电容器C3、电阻器R3和时基集成电路NE555组成;开关电路由晶闸管VTH、电阻器R2和发光二极管LED组成;电源电路由降压电容器Ci、电阻器R,稳压二极管v5、整流二极管VD和滤波电容器G组成。交流220V电压经Cl降压、vs稳压、VD整流及C2滤波后,产生8.5V(V0)直流电压供给NE555。

在白天,光敏电阻器RG受光照射而呈低阻状态,NE555的②脚和⑥脚电位高于2V.T/3,NE555的③脚输出低电平,发光二极管LED不发光,晶闸管VTH处于截止状态,照明灯EL不亮。

当夜幕降临时,光照度逐渐减弱,光敏电阻器RG的阻值逐渐增大.NE555的②脚和⑤脚电压也开始下降,当两脚电压降至V“/3时,NE555内部的触发器翻转。③脚由低电平变为高电平,使LED导通发光.VTH受触发而导通,将照明灯EL点亮。

简单的路灯自控电路图(六)

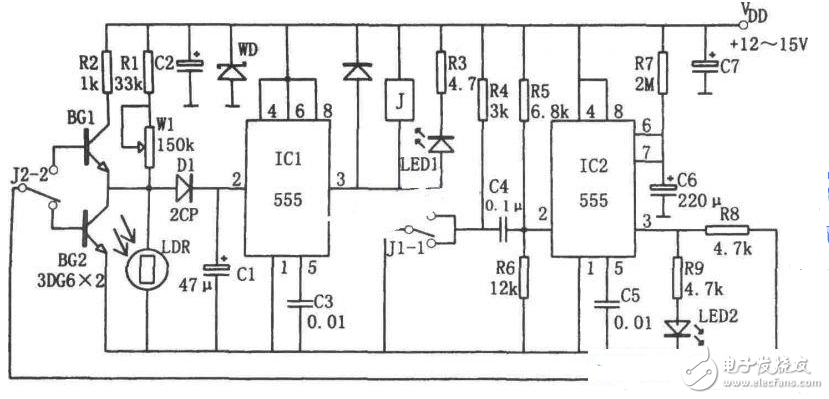

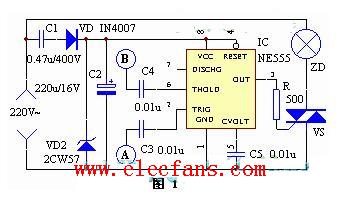

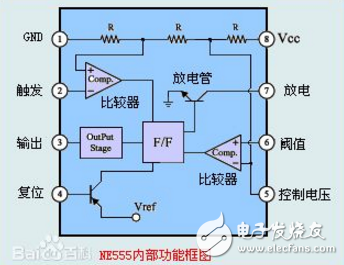

如图所示为高性能路灯光电控制电路。该电路由光电转换元件LDR、比较电路IC1(555)、单稳定时电路IC2等组成。其中IC2与BG1、BG2又构成“动作闭锁”回路,LDR元件采用光敏电阻。

当LDR受到光照时,其呈低阻值,555因②脚输入低电平而发生置位,③脚输出高电平,因此继电器J不动作,发光二极管LED1不发光。夜间,LDR因受不到光照而呈高阻值,555因②脚输入高电平而发生复位,③脚输出低电平,从而使继电器J吸合,发光管LED1发光。此时又触发IC2工作,使其输出定时为td=1.1R7C6(约10分钟)的信号,相应发光二极管LED2发光。这样l0分钟内,可以解决继电器在“临界动作点”不稳定的问题。电路中的“动作闭锁”回路也可以克服继电器在临界动作点因光线不稳定变化而频繁动作的缺点。因此本电路实现了对路灯的高性能的光电控制作用。

简单的路灯自控电路图(七)

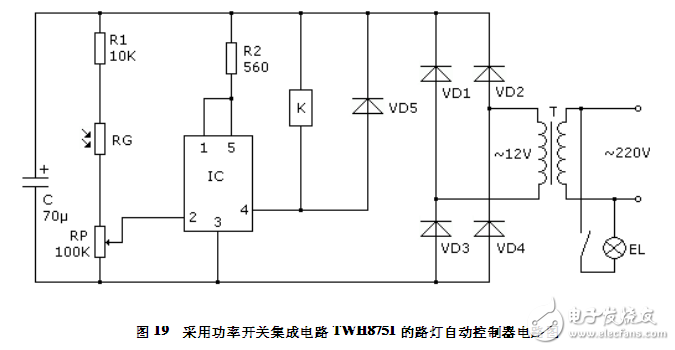

采用功率开关TWH875的路灯自动控制器电路设计

电路工作原理:该光控路灯电路由电源电路和光控电路组成,如图所示。电源电路由电源变压器T、整流二极管VDl-VD4和滤波电容器C组成。光控电路由光敏电阻器RG、电阻器R1、R2、可变电阻器RP、电子开关集成电路IC、继电器K和二极管VD5组成。交流220V电压经T降压、VDl-VD4整流和C滤波后,为光控电路提供+l2V工作电源。白天,RG受光照射而呈低阻状态,使IC的2脚(选通端)和4脚(输出端)均为高电平,其内部的电子开关处于截止状态,K不吸合,路灯EL不亮。夜晚,RC无光照射呈高阻状态,IC的2脚变为低电平,其内部的电子开关接通,EL点亮。调节RP的阻值,可改变光控的灵敏度。

Rl和R2选用1/4W金属膜电阻器或碳膜电阻器。RP选用实心可变电阻器。RG选用RG45系列的光敏电阻器。C选用耐压值为16V的铝电解电容器。VDl-VD5选用1N400l或lN4007型硅整流二极管。IC选用TWH8751型电子开关集成电路。K选用JZX-22F型(触头电流负荷为IOA)l2V直流继电器,可将其两组常开触头并联使用。T选用3-5W、二次电压为l2V的电源变压器。 制作时可自制印刷电路板,也可使用万能印刷电路板,电路安装完成后,只要线路正确,一般无需调试即可正常使用。

-

路灯

+关注

关注

2文章

159浏览量

29057 -

触发器

+关注

关注

14文章

2050浏览量

63042

发布评论请先 登录

【EasyEDA视频教程】以NE555电路为例教您在EasyEDA中绘制电路图

ne555调温电路图大全(六款ne555调温电路)

ne555闪烁灯电路图大全(频闪灯/振荡电路/闪光电路)

简单的路灯自控电路图大全(光控触发器/NE555/光电控制的七款电路详解)

简单的路灯自控电路图大全(光控触发器/NE555/光电控制的七款电路详解)

评论