Question:

Come up with logic that counts number of ‘1’s in a 7 bit wide vector.You can only use combinational logic.

Answer:

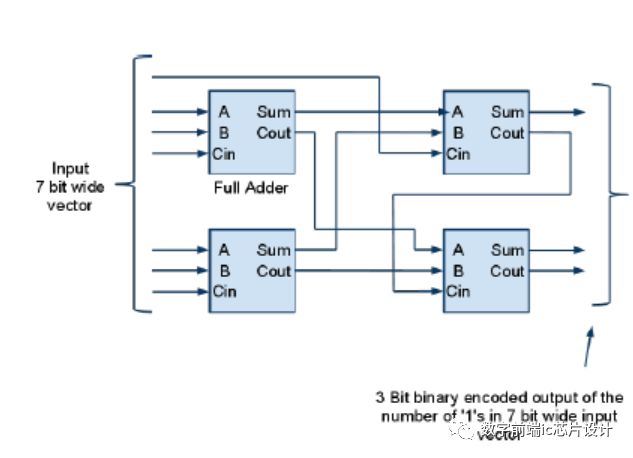

Following is one of the ways to come up with such logic.

Input vector is 7 bit wide. To sum up 7 bits we need 3 bits of binary encoded output.We’ve full adders available. A single full adder can add 3 input bits and generate 2 bitsof binary encoded output.E.g. a full adder can add 3 bit wide input vector ‘111’ and generate ‘11’ output.We can pick two full adders and add up 6 bits of the input vector and will end up withtwo sets of two bit wide binary encoded data.E.g. if input vector is ‘1100111’, we can assume two full adders adding up first 6bits ‘110011’ where first three bits ‘110’ are input to first adder and ‘011’ are inputto second adder. First adder will output ‘10’ (decimal 2) and second adder will alsooutput ‘10’ (decimal 2), and we need to add up two two bit binary vectors. We canagain employ full adders to do this as we still have to account for the 7th input bit ofthe input vector. That can go into the least significant full adder carry-input.

For the above example :

Input vector ‘1100111’

input ‘110’ => full adder => ‘10’ output

input ‘011’ => full adder => ‘10’ output

10

+10

------

100 => output (4)

Now accounting for the seventh input bit ‘1’ as carry into the least significant adder.

1 <= Carry in.

10

+10

-----

101 => Binary encoded decimal 5 which is the input of 1s in inputvector ‘1100111’.

Full adders can be used to add-up 3 input bits at a time. Outputs of first level of fulladders represent the two bit encoded version of the total ‘1’s count, which we need toadd up get the final two digit encoded version of total ‘1’s. Since we need to add up7 bit inputvector, 7th input vector can be used as ‘Carry In’ in the second level of fulladders.

-

asic

+关注

关注

34文章

1277浏览量

124936

原文标题:北美ASIC经典面试试题(2)

文章出处:【微信号:ic_frontend,微信公众号:数字前端ic芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

单片机必掌握|20个经典设计电路,看看有没有你不会的

面试必看!排队自旋锁32位变量的域划分与核心作用

符合 UL1741 标准的北美光伏并网电表应用解析

智行者蜗小白亮相2025 ISSA北美清洁展

人工智能工程师高频面试题汇总:循环神经网络篇(题目+答案)

用30道电子工程师面试题来拷问堕落的你...

天合储能北美大单持续发货

AI芯片,需要ASIC

常见电子类硬件笔试题整理(含答案)

最全的硬件工程师笔试试题集

【硬件方向】名企面试笔试真题:大疆创新校园招聘笔试题

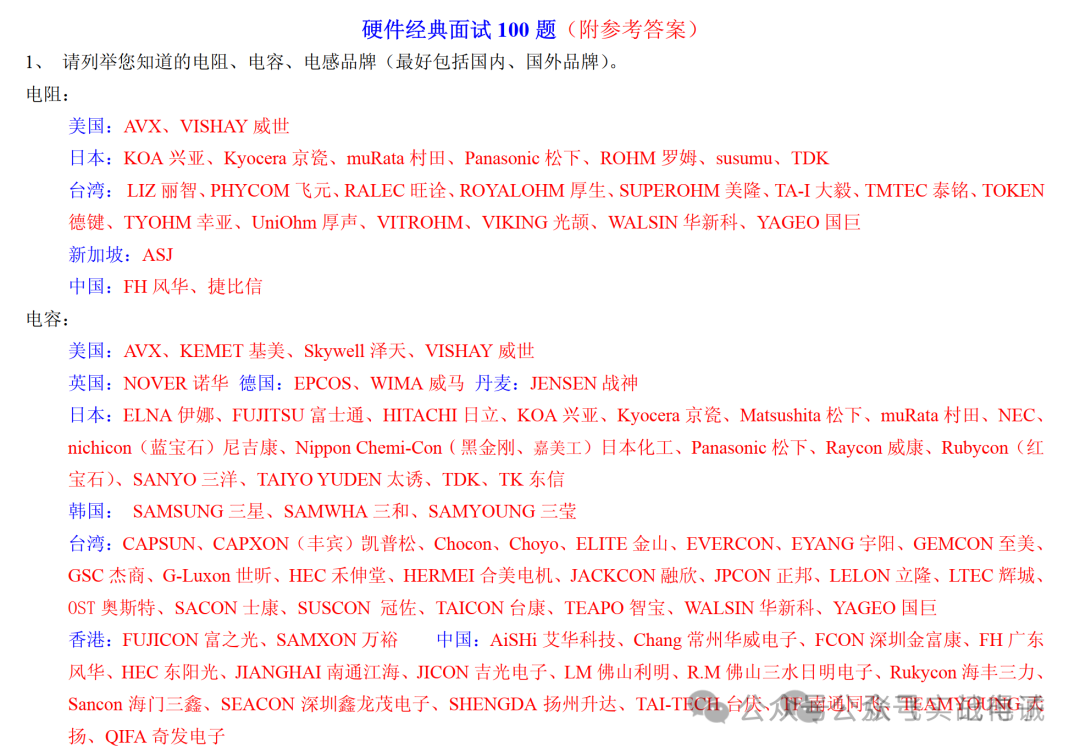

硬件工程师面试/笔试经典 100 题

北美ASIC经典面试试题

北美ASIC经典面试试题

评论