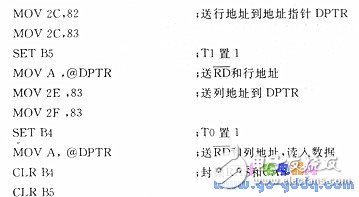

读取一字节数据的程序段如下:

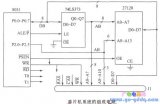

读取数据时,T1先置1,其后的RD信号将行地址送到地址线AB上,并使D。触发器锁存Tl,Q,变成低电平,使RAS有效(低电平),实现行选通;再置TO为l,其后的RD信号将列地址送到AB上,并产生CAS信号,使欲读出单元的数据出现在DB上。RD失效的上升沿使CAS失效,同时,D2触发器置1,使D1清零,RAS也失效变为高电平。经过RC延迟放电,使欲读出单元的数据出现在DB上,D2重新清零,Q2又为高电平,恢复初始状态D1、D2均为零。

程序最后送T0、T1低电平,封锁RAS和CAS,防止系统中其他读/写器动作使DRAM产生误动作。

写数据过程与此类似。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

单片机

+关注

关注

6074文章

45340浏览量

663434 -

DRAM

+关注

关注

40文章

2373浏览量

188147

发布评论请先 登录

相关推荐

热点推荐

如何通过单片机控制 Nand Flash

是前者。(为什么呢?因为该单片机集成了蓝牙,该设备同时需要可以在上位机显示实时数据。)问题来了:1,如何实现,通过单片机写,通过

发表于 09-24 14:09

请问单片机如何控制nand flash

的初步计划是前者。(为什么呢?因为该单片机集成了蓝牙,该设备同时需要可以在上位机显示实时数据。)问题来了:1,如何实现,通过单片机写,通过

发表于 08-29 09:40

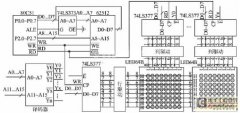

基于MCS51单片机的大屏幕LED显示屏高速控制方案

以MCS51系列单片机为例,介绍单片机对大屏幕LED显示屏的一种高速控制方案。单片机对LED显示屏的显示控制,一般是先从

发表于 01-15 16:22

•2316次阅读

MCS-51单片机指令系统“读-改-写”指令

单片机首先将欲修改的寄存器的内容读回ALU,对相应位进行修改,然后再整个写回原来的寄存器地址,完成该功能的指令就叫做“读-改-

发表于 11-23 13:38

•1892次阅读

单片机烧写器是什么 烧写器怎么用?

编程器就是工具,在进行单片机开发时,你可以编程写了许多代码,只要执行此代码,单片机便依你的指示工作了,但如何将这些代码(或数据)写进单片机内

发表于 02-10 12:16

•5次下载

优化数据库性能使用LSI MegaRAID CacheCade Pro 2.0读/写缓存软件

电子发烧友网站提供《优化数据库性能使用LSI MegaRAID CacheCade Pro 2.0读/写缓存软件.pdf》资料免费下载

发表于 08-10 17:38

•0次下载

MegaRAID CacheCade Pro 2.0读/写缓存软件

电子发烧友网站提供《MegaRAID CacheCade Pro 2.0读/写缓存软件.pdf》资料免费下载

发表于 08-22 10:59

•1次下载

单片机控制的动态数据缓存器的DRAM读/写控制过程

单片机控制的动态数据缓存器的DRAM读/写控制过程

评论