引言

电子设备通常用机壳来屏蔽外界电磁场的干扰,机壳外部通常会开孔来提供通风性、可见性,而这样的开孔会使外部的电磁场通过孔缝耦合到设备机壳内部,从而在机壳内部的设备或印刷电路板上感应出电流和电压,降低设备或元件的性能,严重时会对内部设备造成损坏。因此,研究有空屏蔽腔对电磁干扰的电磁屏蔽效能有重要的实际意义和价值。从以往的研究看,提高屏蔽效能的方法有很多,如相同面积下,孔阵的屏蔽效能优于单孔的屏蔽效能,双层孔的屏蔽效能优于单层的屏蔽效能,也研究了很多因素对屏蔽效能的影响,如孔的大小,形状,孔间距,电磁波极化方向等。本文主要推导出双层加载电路板屏蔽腔屏蔽效能公式,并运用CST仿真验证,研究电路板大小、位置、数量等因素对后腔中心点屏蔽效能的影响。

1 理论

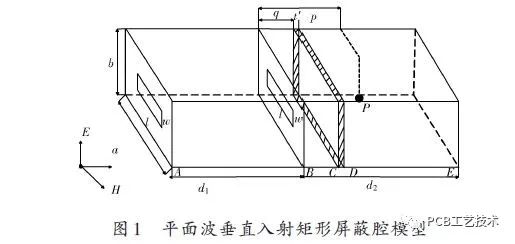

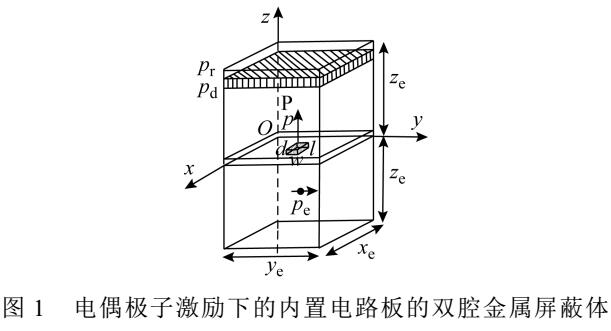

平面波垂直照射双层有矩形孔加载电路板的屏蔽腔的模型如图1所示。一般情况下,由孔缝耦合进入屏蔽腔的能量要比穿透腔体壁进入屏蔽腔的能量要多,因此只考虑耦合能量。

本文采用材料为铜的双层屏蔽腔模型,分前腔和后腔两部分。a ,b 是屏蔽腔的宽和高,前腔长度为d1 ,后腔长度为d2 ;w ,l 为腔体上开孔的长和宽;p 为后腔的中心观测点;q 为内层孔到PCB板的距离;PCB 板厚度为t′ ;腔体厚度为t .

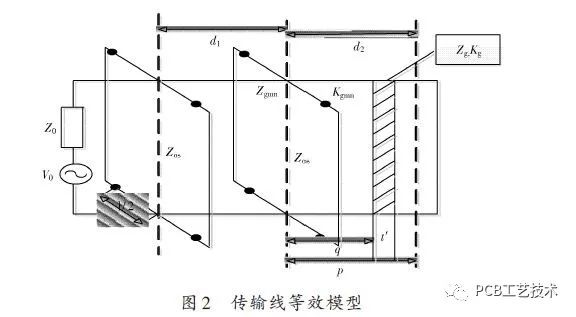

根据M.P.Robinson提出的传输线理论,孔缝等效为两端短路的共面带状传输线,矩形机壳等效为终端短路的波导。该模型等效电路图如图2所示。

在图2中,V0 为等效辐射源,Z0 为空气波阻抗,约为377 Ω ,Zos 为孔缝的特性阻抗,等效矩形波导的特性阻抗和传播常数为Zgmn 和Kgmn .

孔缝特性阻抗由Gupta 给出的公式[6]得出有效宽度:

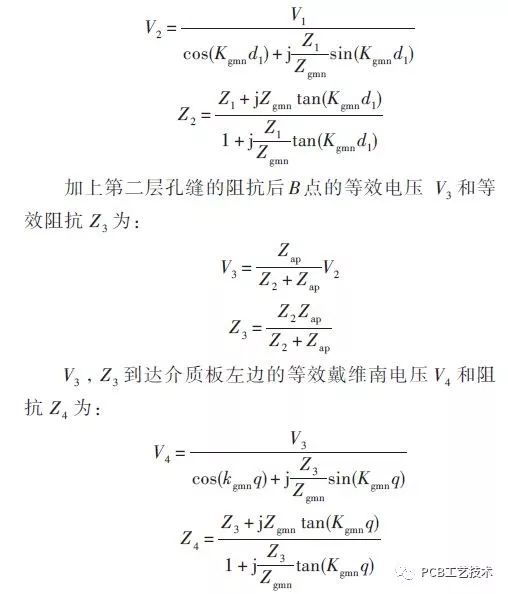

经过AB 之间的传输线后,由戴维南定理可得B 点的等效电压V2 和等效阻抗Z2 :

电路板是一个复杂的整体,它包括金属平板、导线、电子元件和损耗介质等,在此采用一块电导率为σ = 0.22 S - m-1 ,介电常数为εr = 2.65 的宏观介质板代替PCB[7-8],其特性阻抗和传播常数为Zg 和Kg .其中当介质板大小与矩形腔横截面大小无限接近时,腔内电磁场在介质板表面的反射可以忽略,由传输线理论可得介质板左端的电压经过厚度为t′ 的介质板传输到板右侧的电压V5 和阻抗Z5 为[6,8]:

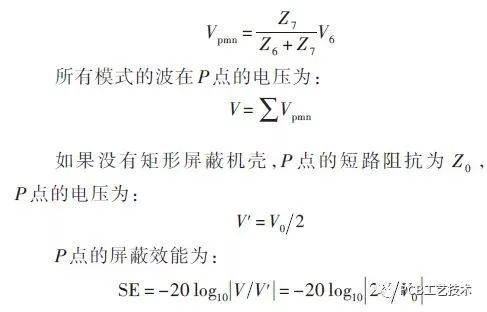

每一种模式的波在P 点的电压为:

2 仿真结果分析

为了验证理论结果的正确性,用电场强度为1 V - m-1 的平面电磁波照射厚度为1 mm的矩形屏蔽壳,腔体尺寸为300 mm × 120 mm × 600 mm ,其中前腔长300 mm ,后腔长300 mm ,孔缝尺寸为80 mm ×20 mm ,介质板尺寸为300 mm × 120 mm × 1 mm ,安装在距离第二层孔缝100 mm 处,仿真频率为200 MHz~1 GHz .

介质板中心与开孔中心以及观测点在一条直线上,当屏蔽腔内有介质板时,入射波耦合进入腔体,遇到介质板,发生介质损耗,电磁波能量主要分为三部分:一部分透过介质板进一步传播,一部分反射,还有一部分通过介质板与腔体的缝隙发生绕射,介质板还会吸收能量。由于电磁波的透射和绕射,在介质板之后的空间还存在电磁场。

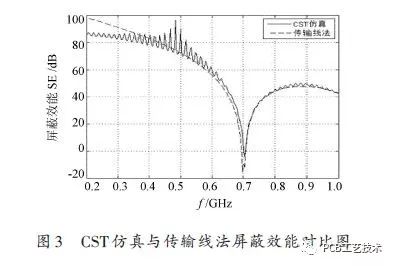

图3 是采用等效传输线法和CST 仿真方法在后腔中心点屏蔽效能的对比,可以看出两种方法的结果在低频有部分差异,但在300 MHz以后较好吻合。且腔体在707 MHz出现谐振现象。

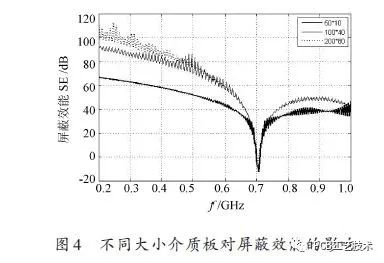

2.1 改变介质板大小对屏蔽效能的影响

图4 中内层孔到加载PCB 板的距离q=100 mm,采用三种不同大小的介质板,分别为500 mm×10 mm,100 mm×40 mm 和200 mm×80 mm.可以看出,在给定频率范围内,介质板越大,腔体屏蔽效能越高,这是因为介质板越大,其介质损耗越大,谐振点的场强越小,屏蔽体的屏蔽效能越大。

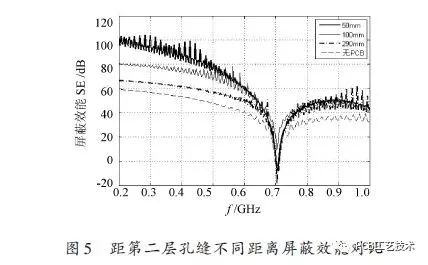

2.2 介质板与第二层孔缝之间的距离对屏蔽效能的影响

介质板尺寸不变为300 mm×120 mm×1 mm.内层孔到加载PCB板的距离q 变化。在这里q 分别取50 mm,100 mm 和290 mm,最后和没有PCB 板的情况做对比。

由图5 可知,在给定频率范围内,介质板离第二层孔缝越远,屏蔽效能越低。当介质板离第二层孔缝50 mm的时候,大部分耦合场发生反射,耦合出腔体,因此第二层腔体中心场强是最小的,屏蔽效能是最大的,随着距离的增大,腔体中心场强也逐渐增大,当增加到290 mm的时候,腔体中心场强达到最大值,与无介质板时的场强接近,屏蔽效能也与无介质板时接近。

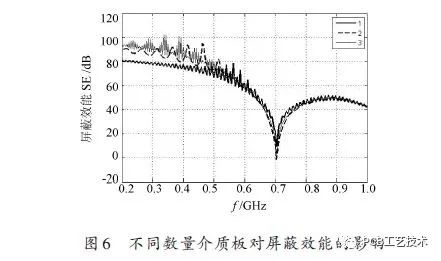

2.3 介质板数量对屏蔽效能的影响

介质板大小均为300 mm×120 mm×1 mm,当只有一块介质板的时候,放置在距第二层孔缝100 mm 的地方,即图1 中q=100 mm 的地方;当有两块介质板的时候,放置在距离第二层孔缝50 mm 和100 mm 的地方,即图1 中q=50 mm 和q=100 mm 的地方,当有三块介质板的时候,放置在距离第二层孔缝50 mm,100 mm 和150 mm 的地方,即图1 中q=50 mm,q=100 mm 和q=150 mm的地方。仿真结果如图6所示。

由图6 可以看出,随着介质板数量的增加,腔体中心位置的屏蔽效能有所增加。

2.4 介质板不同放置方式对屏蔽效能的影响

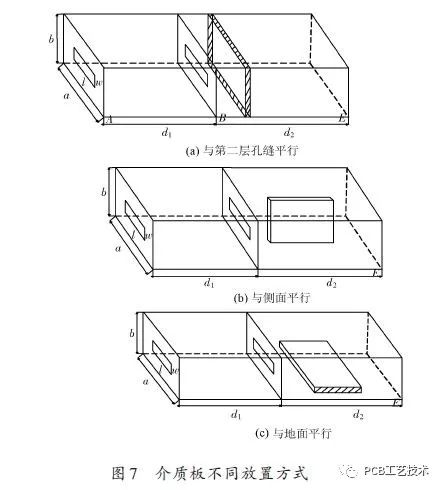

介质板大小不变,以下面三种不同的方式放置:与第二层孔缝平行,放置在距离地二层孔缝100 mm的位置;与侧面平行,放置在垂直于孔缝长边中央的位置;与地面平行,放置在垂直于孔缝短边中央的位置。三种放置方式如图7所示。

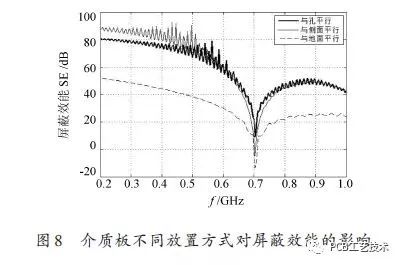

三种情况仿真结果如图8所示。

由图8可知,介质板平行与地面放置时屏蔽效能最差,其他两种放置方式对屏蔽效能影响不大。

3 加载集成运算放大电路板对屏蔽效能的影响

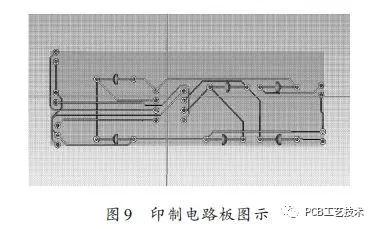

实际的印制电路板和等效的宏观介质板还是存在一定的差异,在这里,将宏观介质板替换为集成运算放大电路板,如图9所示。

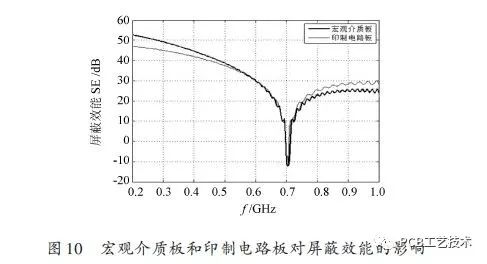

对比介质板和电路板在屏蔽腔中对屏蔽效能的影响,设置介质板大小与电路板相同,均为75.59 mm×25.69 mm×0.711 2 mm,均将模型放置在屏蔽腔后腔中心距z 轴原点-99.288 8 mm 的位置,此处介质板为前面提到的电导率为σ = 0.22 S - m-1 介电常数为εr = 2.65 的宏观介质板,印制电路板采用图9所示的加载集成运算放大电路的电路板。运用CST,将电路板的PCB模型导入到CST的微波工作室中,经过仿真后,其结果如图10所示。

由图10 可知,在大小、厚度、放置位置相同的情况下,宏观介质板和印制电路板得到的屏蔽效能相差不大,即用宏观介质板等效替代印制电路板误差较小。

加载印制电路板后腔体屏蔽效能主要表现在电路板表面电场强度的变化和表面电流的不同,通过CST仿真,得到下述结果。

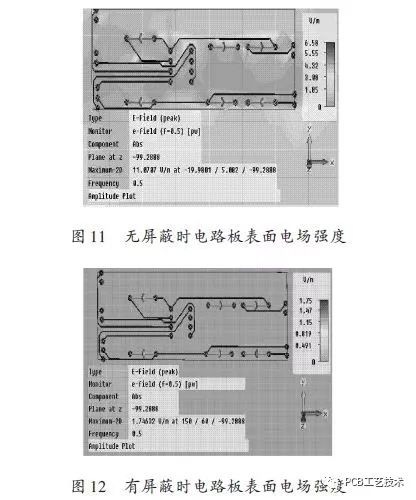

3.1 电路板表面电场

从由图11 和图12 可知,无屏蔽时最大场强为11.070 7 V·m-1 ,有屏蔽时最大场强为0.164 V·m-1 ,可见屏蔽腔对电路板起到了良好的屏蔽效果。并且相隔较近的导线之间容易引起高场强,如果没有屏蔽,将会引起电路板的正常工作,严重时引起损坏。

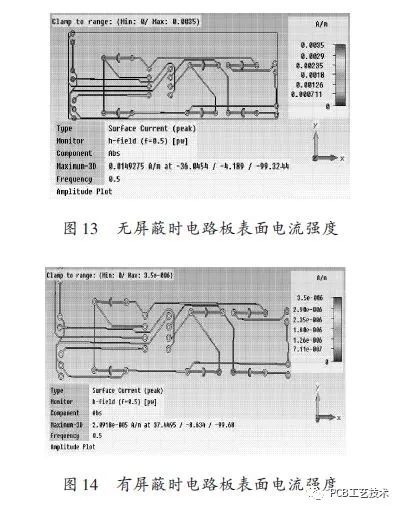

3.2 电路板表面电流

在图13 中,无屏蔽时电路板表面电流最大值为0.014 93 A·m-1 ,图14中,有屏蔽时电路板表面电流最大值为2.091 8e - 005 A·m-1 ,明显比无屏蔽时减小许多,说明屏蔽腔对电路板起到了良好的屏蔽效果。

4 结语

本文用传输线等效模型推出双层加载电路板矩形腔体屏蔽效能的计算公式,通过仿真验证了公式的正确性,并得出结论:在给定频率范围内,介质板越大,腔体屏蔽效能越高;介质板离第二层孔缝越近,屏蔽效能越高;介质板数量越多,屏蔽效能越高;介质板平行与地面放置时屏蔽效能最差,其他两种放置方式对屏蔽效能影响差别不大。通过以上结论,在设计机壳时,可以通过对内部电路板的合理布局提高系统的屏蔽效能,同时,腔体内电路的响应频率应当避开腔体的谐振频率。在本文中,为了更加贴合实际应用,将等效介质板替换为加载集成运算放大电路的印制电路板模型,通过CST仿真,验证了宏观介质板等效代替印制电路板的有效性和相似性,并且验证了屏蔽腔体对内部电路板良好的屏蔽效果以及屏蔽腔体对电路板功能的影响。

-

电路板

+关注

关注

140文章

4621浏览量

92475 -

仿真

+关注

关注

50文章

3872浏览量

132161 -

传输线

+关注

关注

0文章

354浏览量

23766 -

屏蔽效能

+关注

关注

0文章

6浏览量

7583

原文标题:双层加载电路板屏蔽腔屏蔽效能研究

文章出处:【微信号:circuit-ele,微信公众号:PCB工艺技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

微波传输线

基于高速PCB传输线建模的仿真

PCB传输线模型行为特征分析

PCB传输线参数

PSPICE中传输线模型求解?

并联电阻的等效计算公式

复杂多腔体电磁串扰屏蔽效能的解析研究

用传输线等效模型推出双层加载电路板矩形腔体屏蔽效能的计算公式并验证

用传输线等效模型推出双层加载电路板矩形腔体屏蔽效能的计算公式并验证

评论