如何从Flash启动嵌入式系统

以Arty A7开发板为例手把手教你实现

在诸多关于MicroBlaze软核处理器的例程中,往往都是使用JTAG下载然后借助SDK执行程序代码。然而无论是在项目展示还是实际应用中,我们都希望我们的设计可以即插即用,免去重复烧写的麻烦和必须使用SDK运行程序的限制。

事实上,为了部署一个真实的系统,需要在没有任何人为操作的情况下从非易失性存储器中启动MicroBlaze处理器并加载程序代码。

本篇文章,我们就围绕这个话题,以Digilent Arty Artix-7开发板为例,教你如何在板载的QSPI Flash中存储比特流配置文件和应用程序。

QSPI有两个主要作用:

配置Artix FPGA

存储应用软件

对于第一个功能,我们在Vivado设计中不需要包含QSPI接口。我们只需要在Vivado配置中更新对QSPI的设置,提供QSPI Flash存储器与FPGA配置管脚的连接。然而,一旦FPGA配置完成并调用MicroBlaze软核处理器,我们则需要在设计中引入与QSPI Flash通信的接口。这个新添加的接口允许引导程序(bootloader)从QSPI Flash存储器中复制应用程序到Arty实际执行的DDR SDRAM存储介质中。

当然,这会引起一个问题,即MicroBlaze bootloader(引导程序)从何而来?

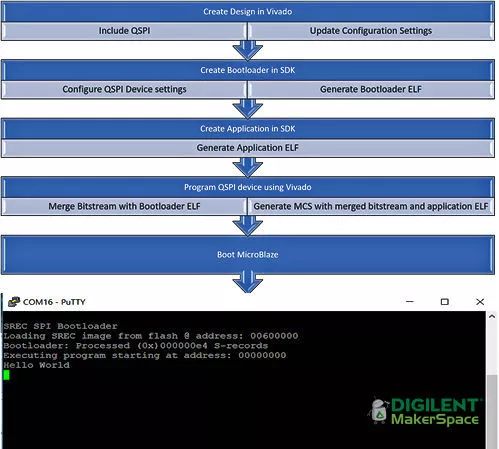

开发bootloader(引导程序)的流程图如下所示:

我们的目标是创建一个MCS镜像,它包含了FPGA比特流和应用软件文件,我们要将它烧写到QSPI Flash中。为了实现这个方案我们需要在Vivado和SDK中执行以下步骤:

在已经存在的Vivado MicroBlaze设计中引入(添加)一个QSPI接口。

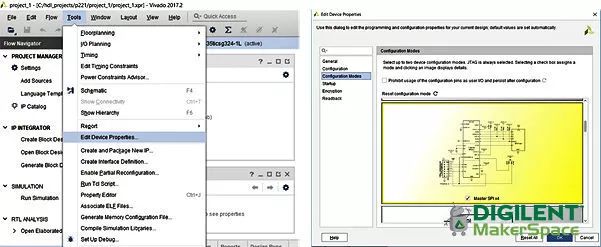

在Vivado中编辑器件设置,使用Master SPI_4来配置器件,并且将bit文件压缩,构建完成后将应用导出到SDK。

在SDK中,基于导出的硬件设计创建一个新的应用工程。在工程创建对话框,选择SREC SPI Bootloader模板。这个选择会创建一个SREC bootloader应用,它会从QSPI Flash中加载主应用程序代码。在构建bootloader ELF之前,我们首先要为应用软件定义对于QSPI基址的地址偏移,在这个示例中为0x600000。我们在blconfig.h中定义这个偏移量。我们还需要更新SREC Bootloader BSP来鉴别正确的串口Flash存储器件。因此重新配置BSP。使用的系列标识号在BSP libsrc目录下的xilisf.h中定义。对于这个应用我们选择类型5,因为Arty板卡使用Micron QSPI器件,它的标识号即为类型5。

现在我们在SDK中创建第二个应用工程。这也是我们将使用bootloader加载的应用程序。在这个应用中我们创建了一个简单的“hello world”工程,确保在linker文件中这个程序从DDR SDRAM开始运行。为了创建MCS文件,我们需要应用程序为S-record格式。这个格式以ASCII格式存储二进制信息。(这个格式已经有40年的历史,最初是为8位Motorola 6800微处理器而开发的。)我们可以使用SDK将生成的ELF转换为S-record格式。为了在SDK中生成S-record文件,我们打开bash shell窗口,切换到ELF所在的目录然后输入如下命令:

cmd /c mb-objcopy -O srec

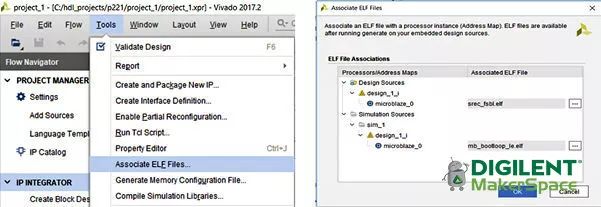

创建好bootloader ELF文件后,现在我们要在Vivado内将比特流(bitstream)文件与bootloader ELF文件合并。这个步骤允许bootloader被加载到MicroBlaze处理器的本地存储空间,并且按照配置运行。因为这个存储空间很小,所以bootloader应用也需要很小才可以。如果你正遇到减小软件应用大小的问题,不妨在增加本地存储内存之前考虑使用编译器优化。

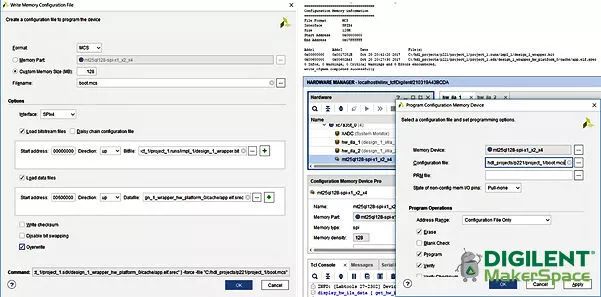

创建好bit文件和S-record文件后,我们使用Vivado硬件管理器来增加配置存储器。

最后一步是生成统一的MCS文件,包含合并的bitstream(比特流)文件和应用软件。当生成这个文件时,我们需要记住加载应用程序时使用与SREC bootloader相同的偏移量。

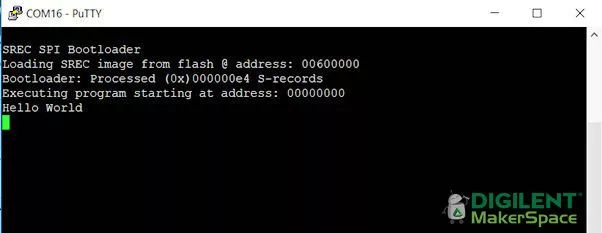

一旦这个文件构建完成并烧写到QSPI存储中,我们就可以进行测试查看MCS文件的工作情况。将Arty板卡与PC终端建立连接然后按下板卡上的复位(reset)按钮。几秒钟后你就会看到Arty板卡上的“done”LED灯亮起,然后在终端窗口中看到SREC bootloader的执行结果。报告应该显示S-record文件在程序执行前已经从QSPI加载到DDR SDRAM中了。

到这里,我们就有了一个可以部署到我们设计中的MicroBlaze工作系统了。

-

嵌入式系统

+关注

关注

41文章

3817浏览量

133865 -

artya7

+关注

关注

0文章

1浏览量

2535

原文标题:以Arty A7为例,教你如何从Flash启动MicroBlaze软核

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

LAT1198+通过 KEIL 制作 QSPI 接口的外部 Flash 下载算法应用笔记

使用TinyFPGA-Bootloader将比特流加载到FPGA

配置文件损坏可能会带来哪些安全风险?

教你如何在板载的QSPI Flash中存储比特流配置文件和应用程序

教你如何在板载的QSPI Flash中存储比特流配置文件和应用程序

评论