声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22283浏览量

630292 -

Xilinx

+关注

关注

73文章

2192浏览量

129929

原文标题:[器件更新] Xilinx UltraScale+ 器件集成 MIPI D-PHY

文章出处:【微信号:xilinx_inc,微信公众号:赛灵思】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx DDR 控制器。 DDR PHY 与电路板调试: Zynq UltraScale+ MPSoC VCU DDR 控制器采用 MIG PHY。 这意味着您可以使用标

发表于 01-07 16:02

Gowin MIPI D-PHY RX TX Advance用户使用指南

Gowin MIPI D-PHY RX/TX Advance 用户指南主要内容包括功能特点、端口描述、时序说明、配置调用、参考设计等。主要用于帮助用户快速了解Gowin MIPI D-PHY

发表于 09-30 06:41

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

本文试图搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何

发表于 06-28 15:53

•2908次阅读

MIPI和Xilinx MIPI解决方案的介绍

本视频简要介绍了MIPI和Xilinx MIPI解决方案,以及如何查找有关Xilinx FPGA提供的D-PHY

对于MIPI系列之“D-PHY”的性能分析和介绍以及应用

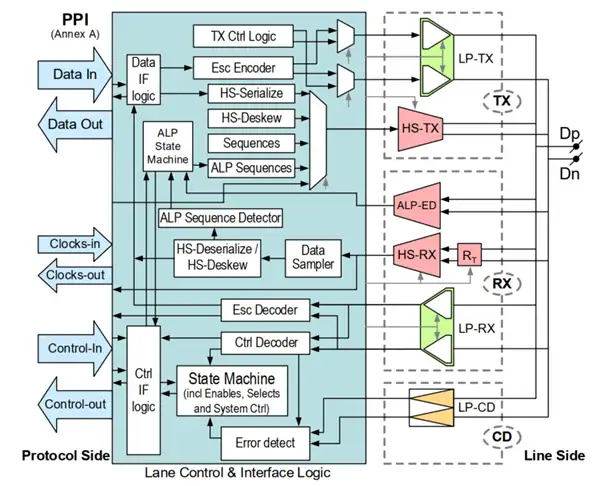

本篇主要介绍MIPI物理层规范中的D-PHY,主要包括D-PHY的架构、操作模式、电气特性等。 MIPI D-PHY将百万像素摄像头和高分辨

发表于 09-15 17:33

•9541次阅读

MIPI D-PHY的静噪措施

从主板和模块之间的MIPI D-PHY布线通过的数字信号从FPC电缆中放射出来,与无线电路的天线耦合,从而可能降低天线接收灵敏度。因此需除去通过MIPI D-PHY布线的噪声。

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

发表于 03-14 19:19

•1次下载

IP_数据表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

IP_数据表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

发表于 03-14 19:20

•0次下载

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

发表于 07-05 19:45

•1次下载

IP_数据表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

IP_数据表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

发表于 07-05 19:46

•1次下载

Diodes公司推出一款符合MIPI D-PHY 1.2协议的信号ReDriver

Diodes 公司 (Diodes) (Nasdaq:DIOD)推出一款低功耗、高性能且符合 MIPI D-PHY 1.2 协议的信号 ReDriver。

聚焦MIPI 系列之四:一文盘点D-PHY/C-PHY/M-PHY之架构与测试解决方案

5G设备、车联网和物联网中扮演着关键角色。本文将深入探讨MIPI D-PHY、C-PHY和M-PHY的架构特点,并盘点相应的测试解决方案。 # 01

AMD助力打造MIPI C-PHY/D-PHY测试方案

凭借增强的 MIPI C-PHY/D-PHY 芯片功能,第二代 AMD Versal Premium 系列可支持显示器和摄像头测试中的新兴连接标准。

Xilinx UltraScale+ 器件集成 MIPI D-PHY

Xilinx UltraScale+ 器件集成 MIPI D-PHY

评论