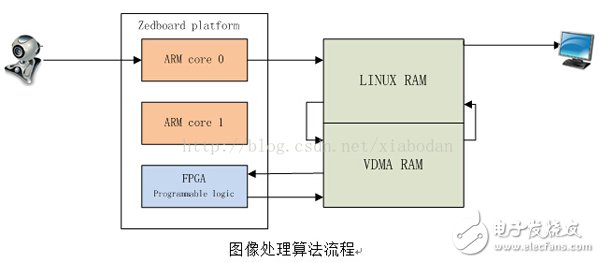

总体设计思路

sobel 算法理论基础

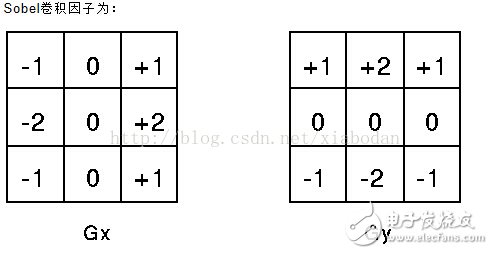

索贝尔算子(Sobel operator)主要用作边缘检测,在技术上,它是一离散性差分算子,用来运算图像亮度函数的灰度之近似值。在图像的任何一点使用此算子,将会产生对应的灰度矢量或是其法矢量。

该算子包含两组3x3的矩阵,分别为横向及纵向,将之与图像作平面卷积,即可分别得出横向及纵向的亮度差分近似值。如果以A代表原始图像,Gx及Gy分别代表经横向及纵向边缘检测的图像灰度值,其公式如下:

Gx = (-1)*f(x-1, y-1) + 0*f(x,y-1) + 1*f(x+1,y-1)

+(-2)*f(x-1,y) + 0*f(x,y)+2*f(x+1,y)

+(-1)*f(x-1,y+1) + 0*f(x,y+1) + 1*f(x+1,y+1)

= [f(x+1,y-1)+2*f(x+1,y)+f(x+1,y+1)]-[f(x-1,y-1)+2*f(x-1,y)+f(x-1,y+1)]

Gy =1* f(x-1, y-1) + 2*f(x,y-1)+ 1*f(x+1,y-1)

+0*f(x-1,y) 0*f(x,y) + 0*f(x+1,y)

+(-1)*f(x-1,y+1) + (-2)*f(x,y+1) + (-1)*f(x+1, y+1)

= [f(x-1,y-1) + 2f(x,y-1) + f(x+1,y-1)]-[f(x-1, y+1) + 2*f(x,y+1)+f(x+1,y+1)]

其中f(a,b),表示图像(a,b)点的灰度值;

图像的每一个像素的横向及纵向灰度值通过以下公式结合,来计算该点灰度的大小:

通常,为了提高效率 使用不开平方的近似值:

如果梯度G大于某一阀值则认为该点(x,y)为边缘点。

然后可用以下公式计算梯度方向:

Sobel算子根据像素点上下、左右邻点灰度加权差,在边缘处达到极值这一现象检测边缘。对噪声具有平滑作用,提供较为精确的边缘方向信息,边缘定位精度不够高。当对精度要求不是很高时,是一种较为常用的边缘检测方法。

流程

HLS算法验证与实现

算法验证包括算法C/C++实现,综合编译仿真,实现导出pcore用于-------》XLINX EDK

EDK硬件工程搭建

EDK中主要搭建zedboard硬件平台,实现VDMA(用AXI-Stream),HDMI,DDR等等,生成system.bit,用于连同uboot、fsbl生成zedboard bootload (BOOT.BIN)。

参考:

zedboard启动过程分析 :

LINUX 系统移植

准备一张》8G的SD卡,分区为FAT32+EXT4(其中EXT4为文件系统》4GB,FAT分区为内核 设备树 bootloader) 可以采用gparted分区工具完成,apt-get install gparted

系统移植包括内核镜像的编译,bootloader的移植,设备树的编译,文件系统的移植

具体移植步骤参见:

内核镜像地址:git clone

uboot源码 :git clone git://git.xiinx.com/u-boot-xarm.git点击打开链接点击打开链接点击打开链接

设备树在内核中可以找到,将设备树,内核镜像,BOOT.BIN拷贝到SD卡中FAT分区中

文件系统: 直接拷贝到SD卡中EXT4分区中

LINUX VDMA驱动应用程序编写与实现

编写驱动程序是为了我们能在PS中对VDMA进行管理和控制。前提是在底层中我们已经做好了所有相关的硬件设计等等。

移植OPENCV库:用于对比FPGA算法处理速度比较,有两种方法移植OPENCV库,

1:apt-get install libopencv-dev python-opencv(用于python中)

2:下载源码编译

源码地址:

编译步骤参考:基于opencv网络摄像头在ubuntu下的视频获取

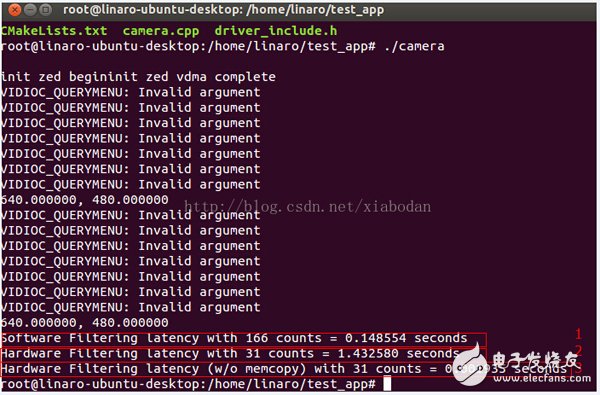

结果展示

FPGA硬件实现Sobel效果 OPENCV软件实现Sobel

处理时间显示

结果分析

上图处理时间中 640*480的视频

1:opencv处理一帧的时间0.148554s 大约为7帧每秒

2:fpga硬件实现一帧总时间(算法时间+VDMA拷贝时间)

3:fpga硬件实现一帧的算法时间,不包含拷贝DMA时间

在cortex A9 700MHZ 速度中 ,FPGA实现的算法速度比OPENCV软件实现速度快50-100倍,FPGA一秒钟可以处理500帧图像,OPENCV只能处理10张不到

但是缺点是,视频拷贝花费了太多的时间。所以我个人认为FPGA处理图像不在算法实现有多复杂与困难,因为FPGA的并行率理论上是无穷的,但是视频流的输入输出的速度直接决定了处理速度。暂时没想到好的方法解决。

-

Vivado

+关注

关注

19文章

846浏览量

70474 -

Zedboard

+关注

关注

45文章

70浏览量

50143

发布评论请先 登录

探索Vivado HLS设计流,Vivado HLS高层次综合设计

新手求助,HLS实现opencv算法加速的IP在vivado的使用

怎么在Vivado HLS中生成IP核?

【正点原子FPGA连载】第七章OV5640摄像头Sobel边缘检测-领航者ZYNQ之HLS 开发指南

Vivado HLS实现OpenCV图像处理的设计流程与分析

Vivado HLS设计流的相关资料分享

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(4)

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(4)

Hackaday读者有话说:Vivado HLS使用经验分享

Vivado+Zedboard之入门实例精选

基于Vivado HLS平台来评估压缩算法

用Vivado-HLS实现低latency 除法器

如何创建Vivado HLS项目

关于Vivado HLS错误理解

Vivado HLS在Zedboard中的Sobel滤波算法实现步骤教程

Vivado HLS在Zedboard中的Sobel滤波算法实现步骤教程

评论