一 简述

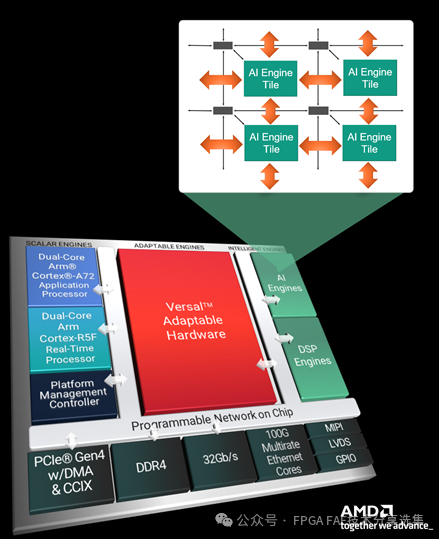

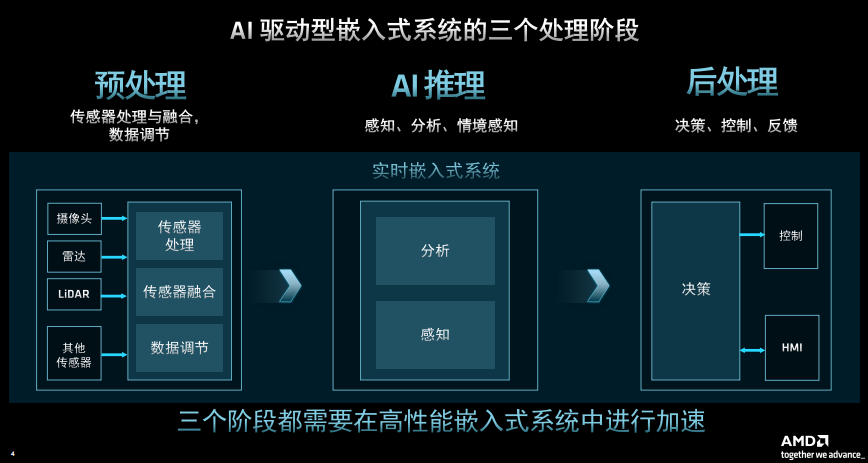

为了应对无线波束形成、大规模计算和机器学习推断等新一代应用需求的非线性增长,AMD 开发了一项全新的创新处理技术 AI 引擎,片内集成该AI Engine的FPGA系列是Versal 自适应计算加速平台 (ACAP) 。

有很多文档都描述了AI Engine的架构和性能参数,但是看完这些后,现实中遇到的问题最多的是这个AI Engine到底怎么用,在Vivado中怎么调用,数据怎么跟PL、ARM之间进行交互,数据怎么给AIEngine运算,计算后的结果又怎么获取,有没有相关的例程等等。我想通过以下教程从Vivado建工程、添加 AI 引擎和应用、Vitis Unified裸机应用程序并生成bin文件在硬件上跑起来一个完整的步骤来告诉大家AI Engine是怎么用起来的,通过这个例子能够让大家熟悉Vivado和Vitis Unified IDE对AIE怎么操作。

作者在创建本文例程时使用的开发工具版本是VitisUnified 2023.2。

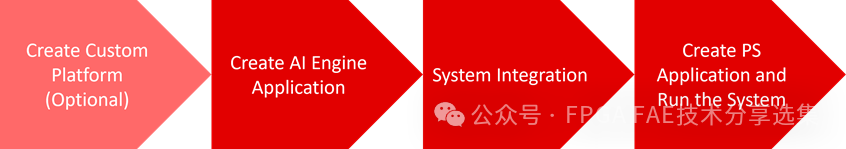

二 AI Engine裸机应用创建的流程

流程分为以下四个步骤,如下图所示:

步骤一:定制平台的创建

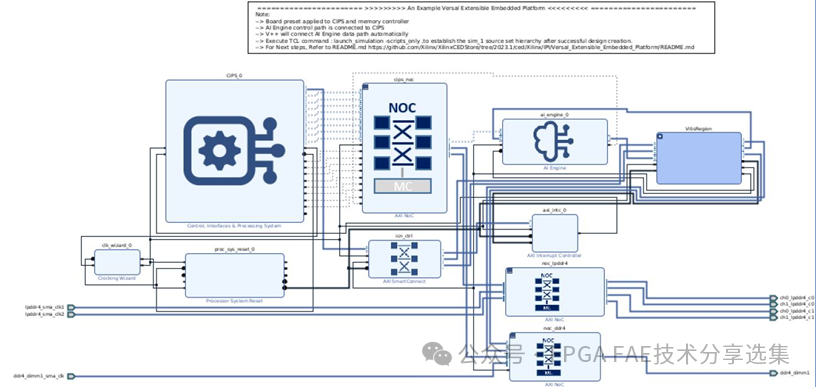

构建硬件平台是设计的起点,将用于构建 Vitis 软件平台应用程序。在本教程的这一步骤中,描述了如何创建新平台的示例。首先使用 AMD Vivado设计套件中的AI引擎构建硬件系统。

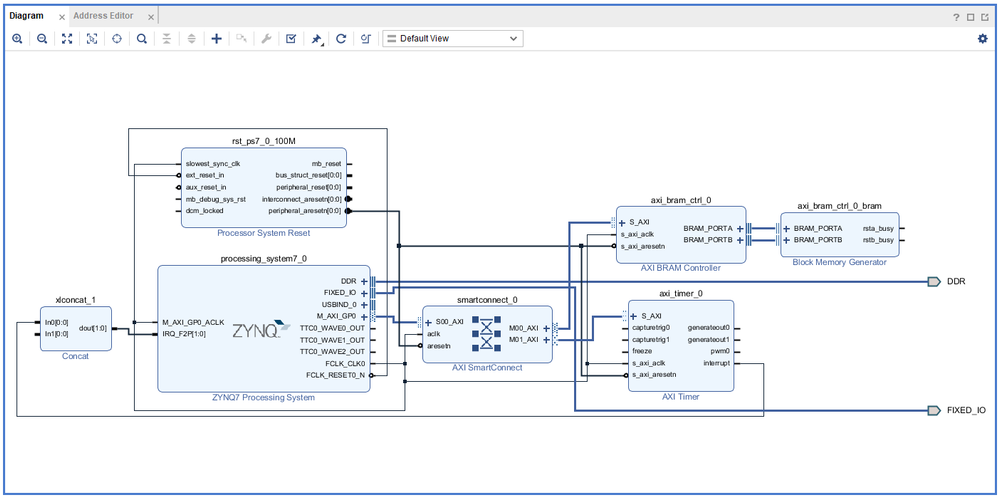

1.在Vivado中构建AMD Versal可扩展嵌入式平台示例设计

1)启动Vivado,然后在欢迎窗口中选择Open Example Project;

2)先单击Next,在Templates选择页面中选择VersalExtensible Embedded Platform,点击Next;

3)将此项目命名为custom_pfm_vck190或者自定义并单击Next;

4)在开发板选择页面中,这里选择的是Versal VCK190 Evaluation Platform,点击Next;

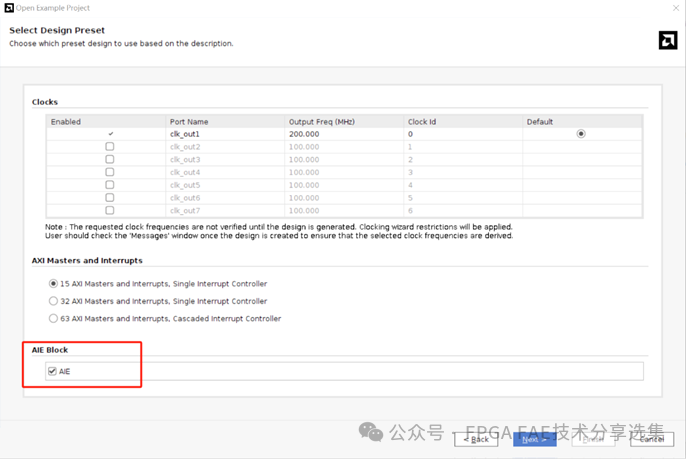

5)在设计预设页面中,保持默认设置。请注意,示例中的可扩展平台AI引擎已添加;

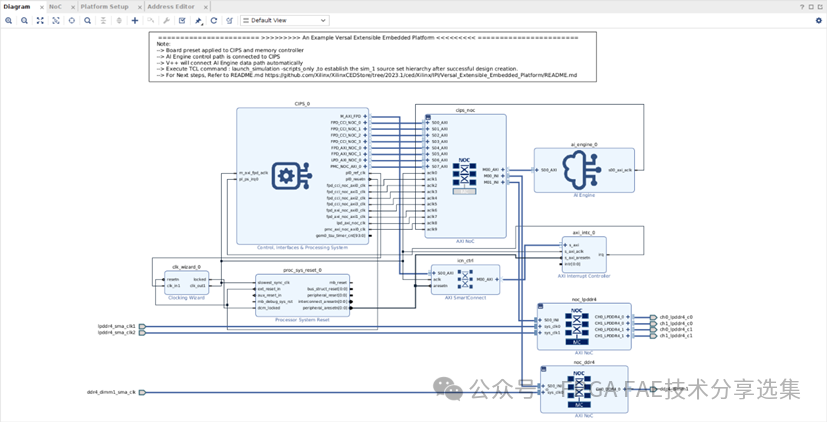

6)单击Finish完成示例工程的创建,Vivado自动使用刚刚创建的模板设计打开 Vivado项目,可以打开Block Deisgn来查看平台设计的详细信息。通过使用预构建的可扩展平台模板,可以轻松获得经过验证的平台硬件设计,以继续下一步。在实际的设计开发过程中,可以使用它作为baseline设计并在此基础上进行进一步的修改;

7)在Vivado左侧的Flow Navigator 面板中单击GenerateBlock Design,单击Generate,然后等待该过程完成;

注意:生成模块设计时,Vivado会显示严重警告,这是因为中断控制器IP有一个未连接的输入。可以忽略,因为Vitis稍后会在流程中自动连接该输入。

8)从Vivado菜单中单击File,然后选择Export -> ExportPlatform,点击Next;

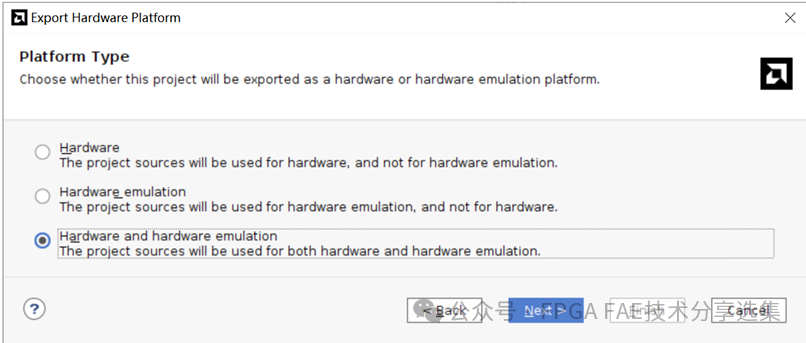

A.在第二页上,选择Hardware and hardware emulation作为平台类型,单击Next;

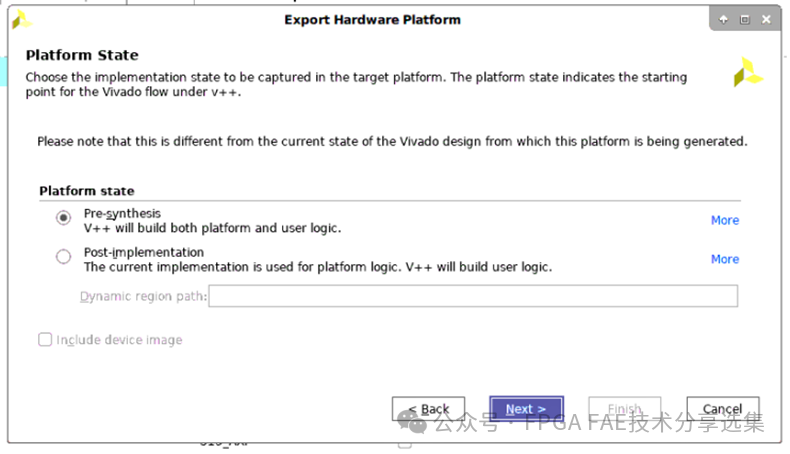

B.在第三页上选择Pre-synthesis,单击Next;

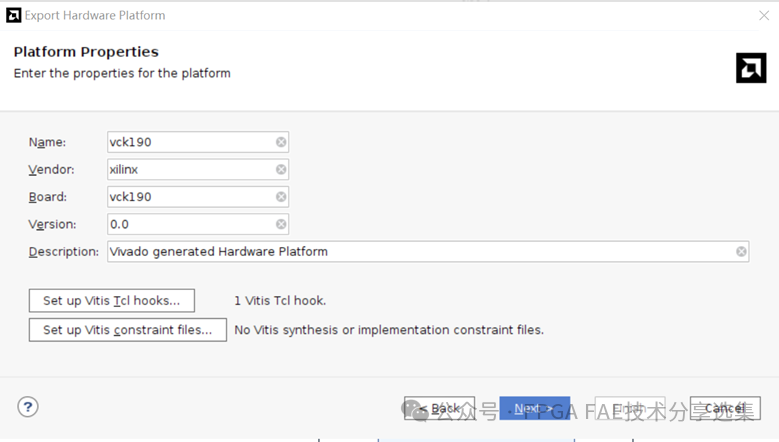

C.在第四页上,添加平台名称,单击Next;

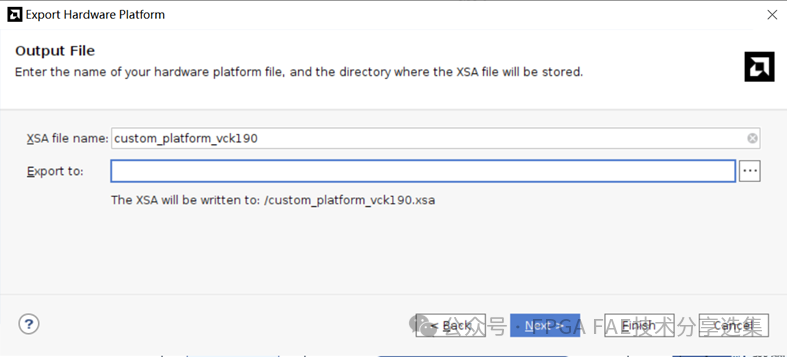

D.在第五页中,设置XSA的名称,然后单击Finish;

9)导出硬件平台后关闭Vivado工程。

2. 在 Vitis 软件平台中构建平台

1)打开 Vitis Unified,然后选择一个工作区;

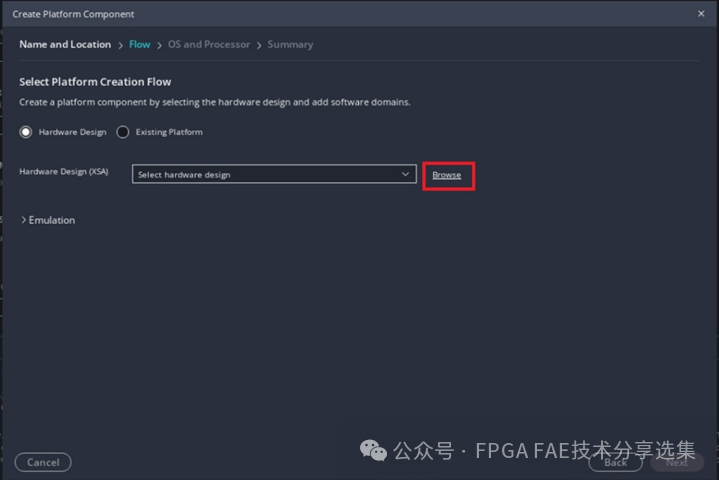

2)在欢迎页面上,选择Create PlatformComponent,或选择File -> New Component ->Platform;

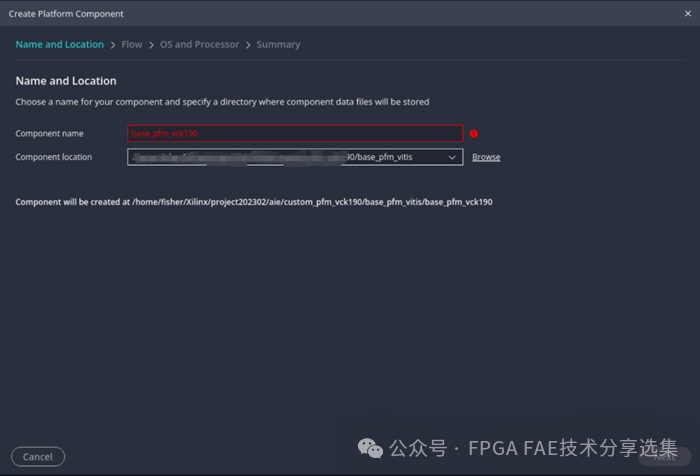

3)将平台组件名称设置为base_pfm_vck190,然后单击Next;

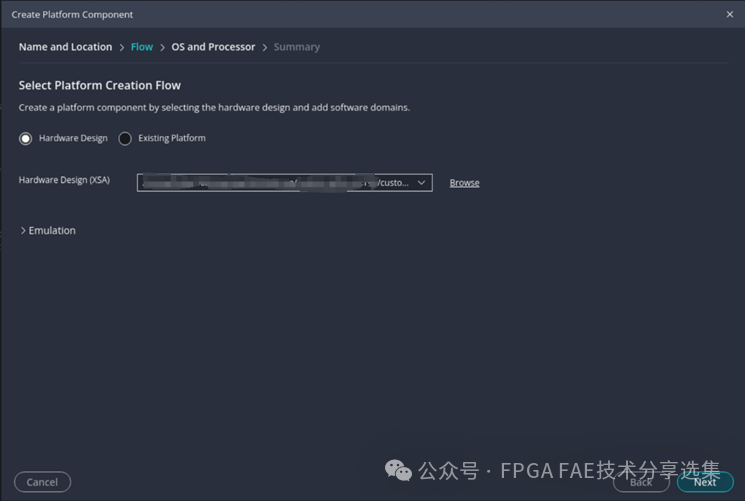

4)选择Hardware Design并使用上一步Vivado导出的 XSA,然后单击Next;

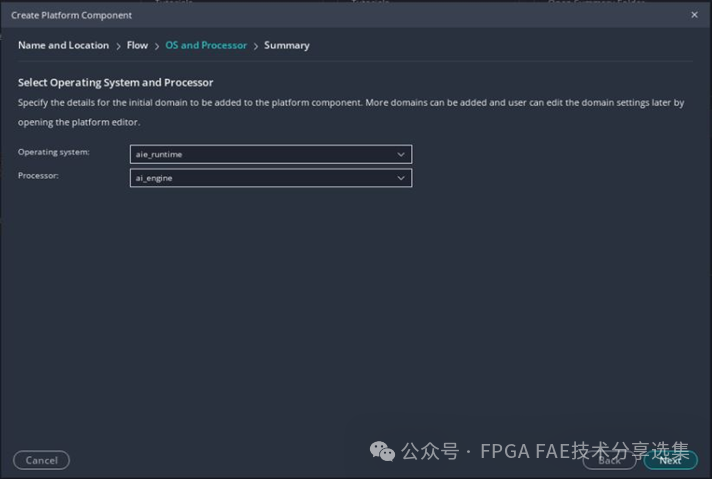

5) 将操作系统设置为aie_runtime,将处理器设置为ai_engine,然后单击Next,接着再单击Finish完成平台组件创建;

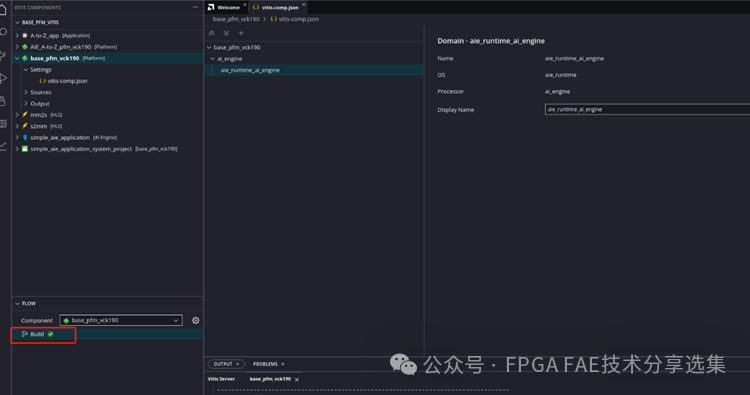

6)然后通过在流程导航器中单击Build并选择base_pfm_vck190组件来构建平台;

注意:如果后面要更改XSA文件,单击位于该平台组件的Settings文件夹中的 vitis-comp.json,然后单击Switch XSA;

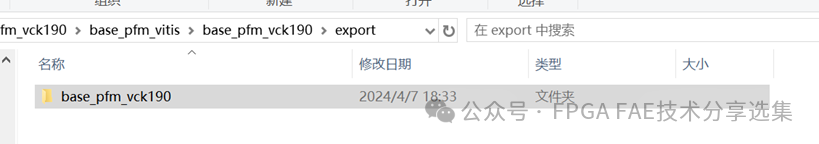

7)生成的平台可以在base_pfm_vck190/export中找到。

在此步骤中,从Vivado Design Suite中开始创建硬件平台,然后根据导出的XSA文件在Vitis Unified软件平台中构建平台。下一步骤,将使用Vitis Unified中的平台构建AI Engine应用程序。

步骤二:创建AI引擎应用

在这一步骤中,将学习如何从模板创建新的AI Engine应用程序工程,并运行Emulation-AIE程序。

1. 新建一个AI Engine应用项目

1)如果已关闭 Vitis UnifiedIDE,将其打开,使用步骤一中相同的工作区;

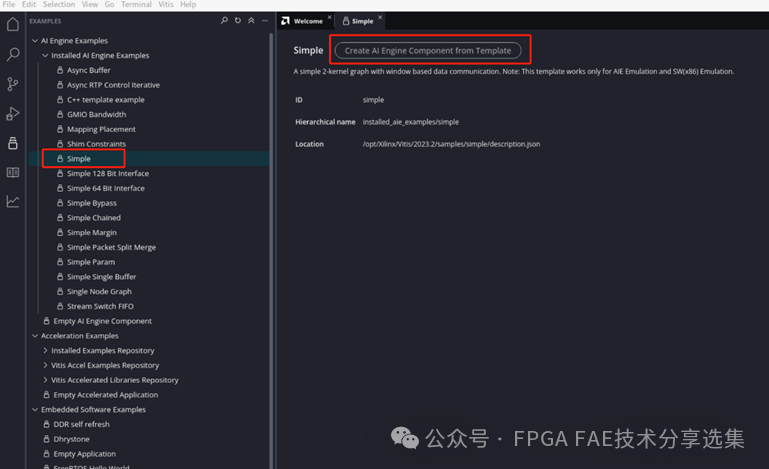

2)单击View -> Examples查看随Vitis Unified安装的应用实例;

3)在AI Engine Examples ->Installed AI Engine Examples下选择Simple,并单击Create AI Engine Component from Template;

注意:在Simple模板的描述中,它表示该模板仅适用于AIE仿真和SW(x86)仿真。在下面步骤中,将学习如何使其在硬件上运行。

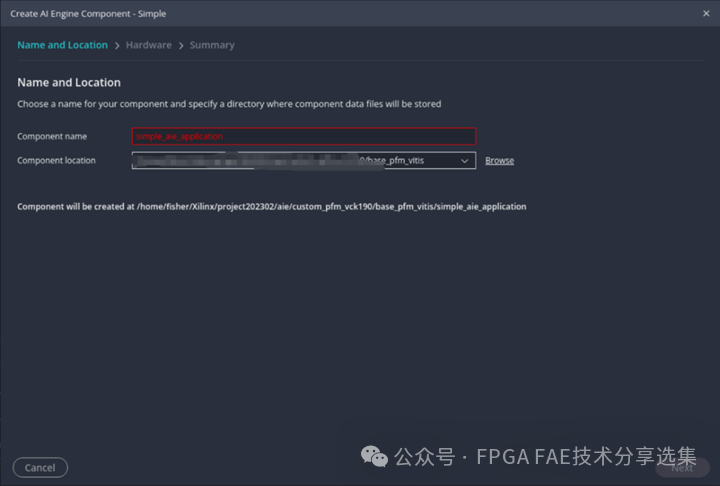

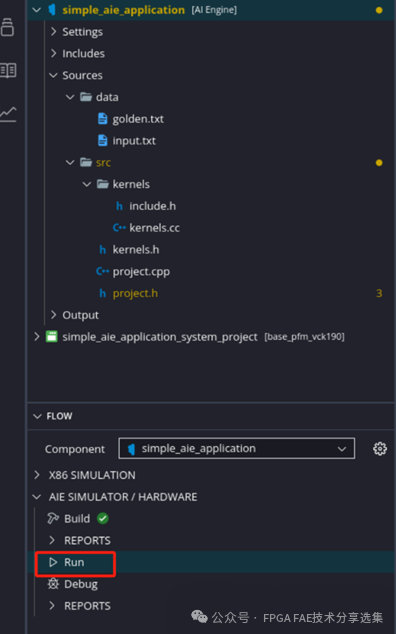

4)将AIE组件名称设置为simple_aie_application,然后单击Next;

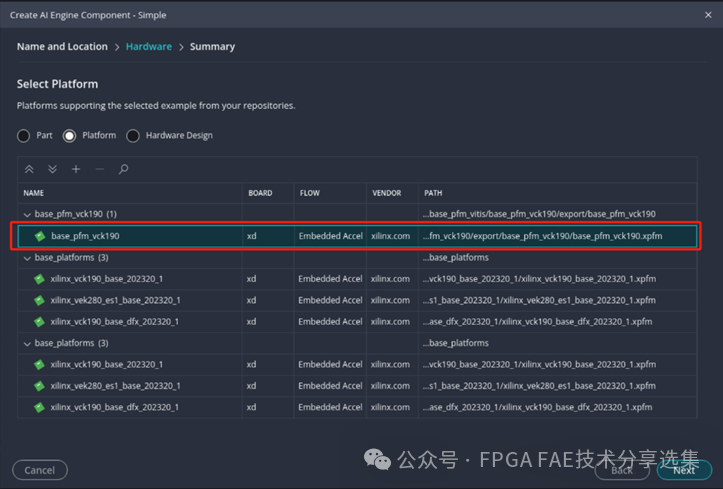

5)在Select Platform页面中,选择要使用的平台,选择刚刚创建的base_pfm_vck190平台, 单击Next,然后下一页面中单击Finish;

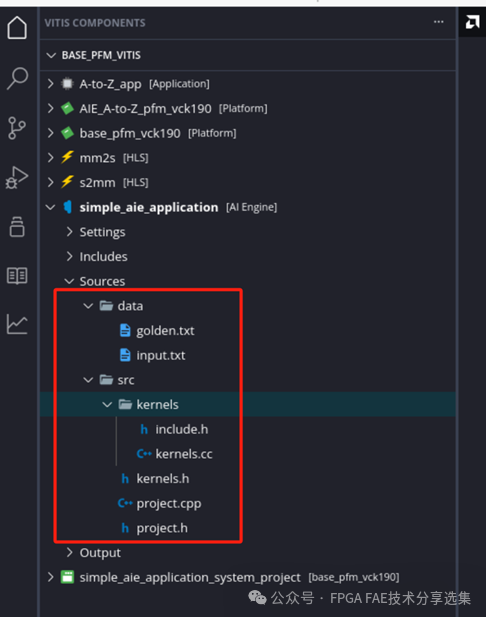

6)该Simple模板导入了两个文件夹:

A.Src文件夹包含kernels和graph的源代码;

B.Data文件夹包含仿真输入的数据(input.txt)和正确的输出数据 (golden.txt)。

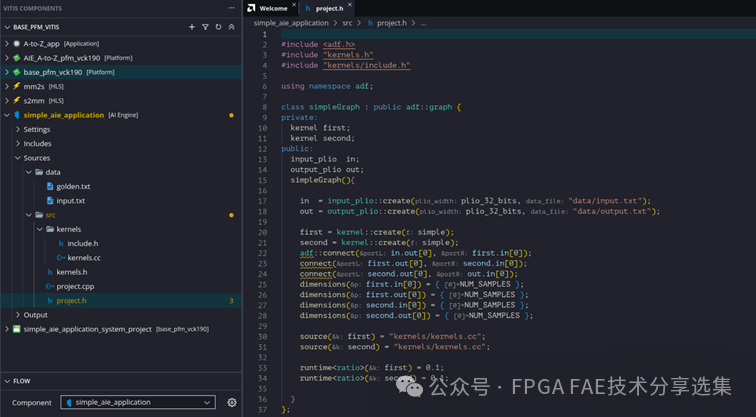

7)打开文件project.h查看graph,可以看到该AIE示例graph有一个输入和一个输出,并实现了具有相同功能的两个内核,第一个内核的输出提供给第二个内核;

first = kernel::create(simple);

second = kernel::create(simple);

adf::connect(in.out[0], first.in[0]);

connect(first.out[0], second.in[0]);

connect(second.out[0], out.in[0]);

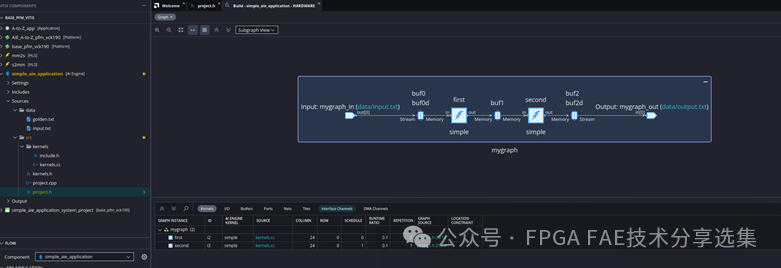

该graph的图形表示如下:

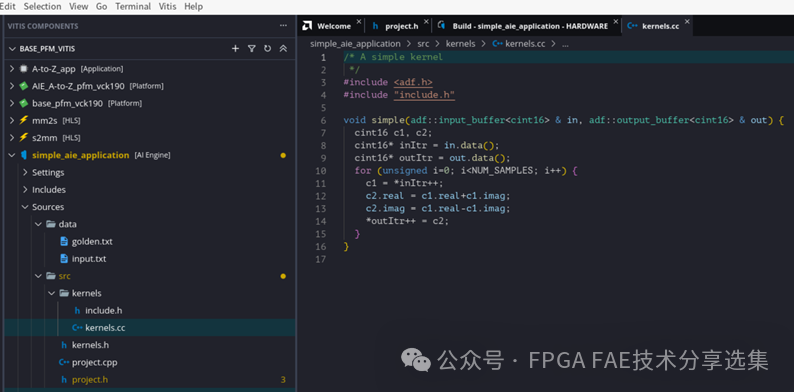

8)打开kernels/kernels.cc文件查看内核中实现哪些功能,可以看到这是一个简单的计算,将输入的实部和虚部相加给输出的实部,输入的实部减去虚部给输出的虚部。

2.构建项目并通过Emulation-AIE运行

1)在流程导航器中,确保选择simple_aie_application组件,然后单击AIE SIMULATOR / HARDWARE下的Build;

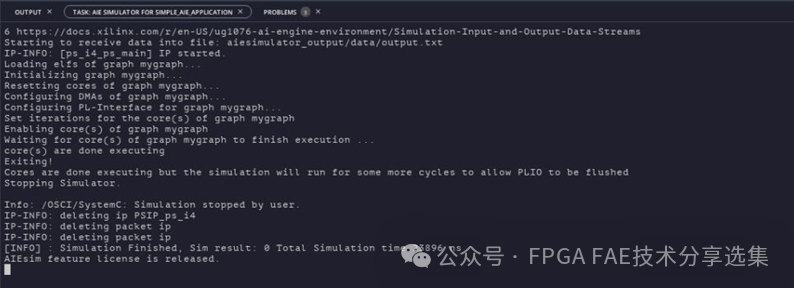

2)Bulid完成后,要运行 System C 仿真(Emulation-AIE或AIE SIMULATOR),在 Flow 导航器中,确保选择simple_aie_application组件,然后单击AIE SIMULATOR / HARDWARE下的Run;

3)在控制台中可以看到仿真成功运行,输出数据文件已经生成build/aiesimulator_output

/data/output.txt,可以将文件output.txt与golden.txt文件里面数据进行比较,output.txt与golden.txt数据一样。

步骤三:系统集成

步骤三:系统集成

在这一步骤中,将学习如何将 HLS 中的可编程逻辑 (PL) 内核添加到系统项目中,并构建整个系统。

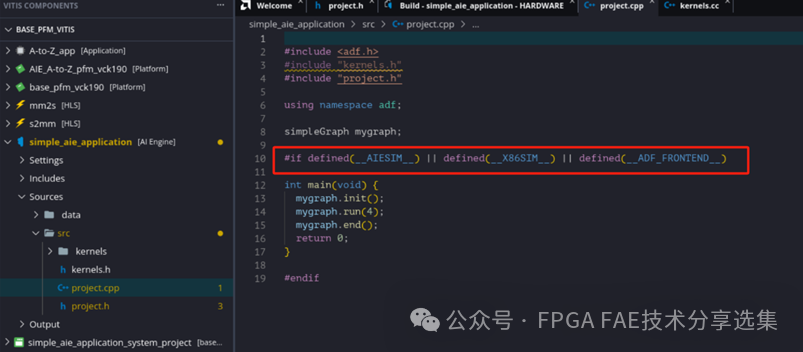

1.修改graph以用于硬件构建 步骤二已经创建了一个可以在AI Engine阵列上运行的应用程序,现在需要修改AI Engine graph以便在硬件中使用,并使用 Vitis 编译器 (V++) 将AI Engine阵列连接到PL;project.cpp中的main函数不会在硬件运行中使用,因此需要添加一个开关(#ifdefined(...)),以便在硬件构建时不考虑这个main函数;

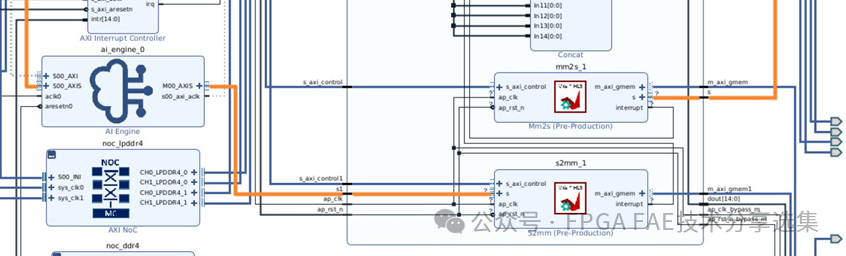

2.添加 PL 内核

在此示例中,使用 HLS 内核用于连接memory和 AXI4-Stream 接口,以便memory和 AXI4-Stream接口之间的数据交互;

mm2s kernel:从memory读取数据并将其输入到AI Engine阵列中;

s2mm kernel:从AI Engine阵列接收输出数据并将其写入memory。

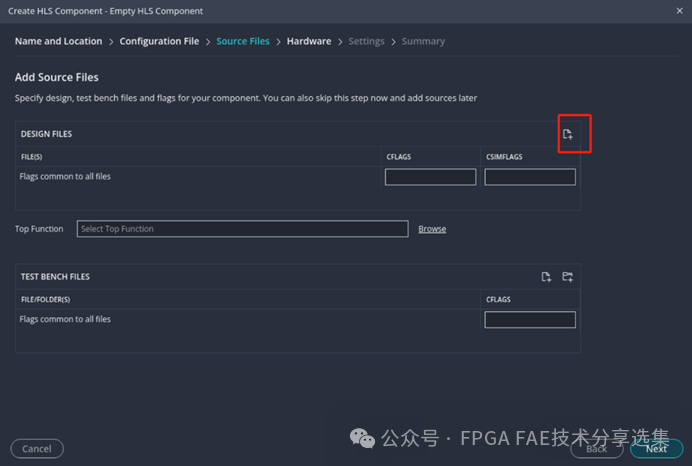

1)在 Vitis Unified IDE 中,单击File -> New Component -> HLS;

2)将第一个组件命名为mm2s并单击Next;

3)在Configuration File页面中,保留默认设置(Empty File),然后单击Next;

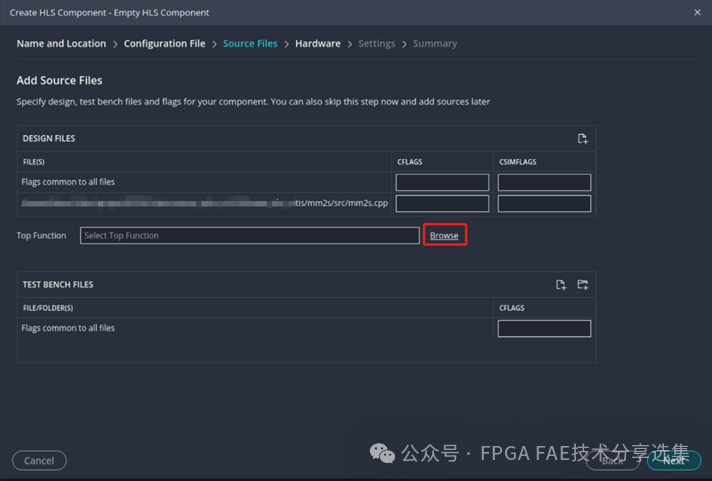

4)在Source Files页面中,添加mm2s.cpp文件;

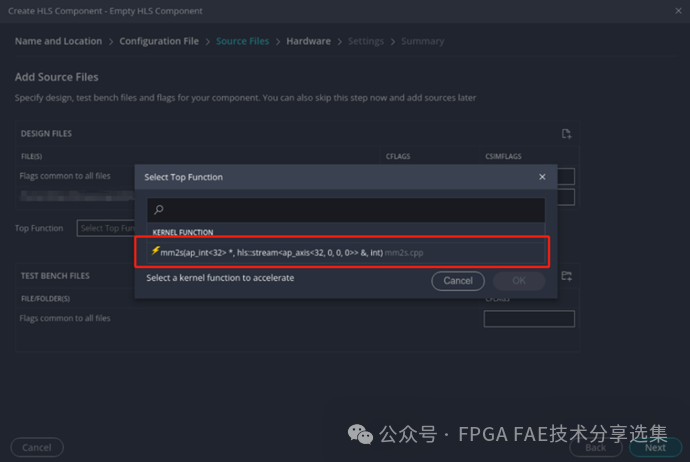

5)在同一页面

中,将mm2s函数设置为top function(点击Browse并选择mm2s),然后单击Next;

6)在

Hardware选择平台页面中,选择刚刚创建的base_pfm_vck190平台,点击Next;

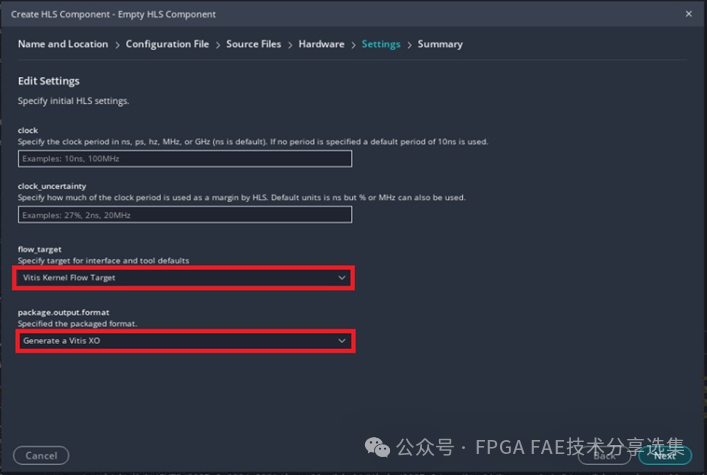

7)在

Settings页面中flow_target下选择Vitis KernelFlow Target,package.output_format下选择Generate Vitis XO,单击Next,然后单击Finish;

8)重

复以上1 到 7 ,使用s2mm.cpp文件创建一个名为s2mm的 HLS 组件。

3. 配置硬件链接项目

刚刚已经导入了kernels,现在我们需要告诉 Vitis Linker如何将所有组件连接在一起

1)在Vitis Unified IDE中单击File -> New Component -> System Project创建一个新的系统项目组件;

2)将此系统组件命名为simple_aie_application_system_project并单击Next;

3)在Platform页面中选择刚刚创建的base_pfm_vck190平台;

4)跳过Embedded Component Paths页面(单击Next),此页面用于运行 Linux 的系统,这个示例是裸机系统,所以不用管,然后在下一面中单击Finish;

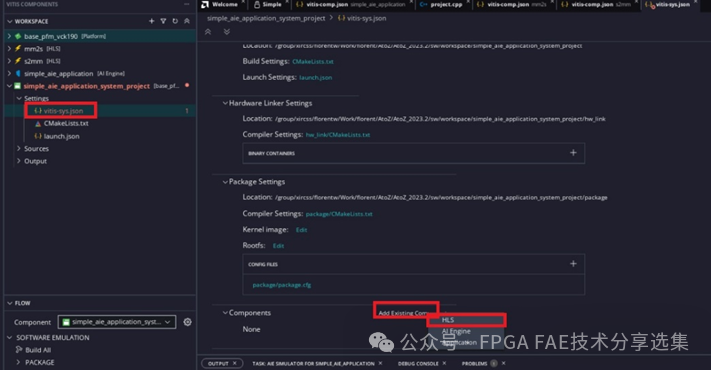

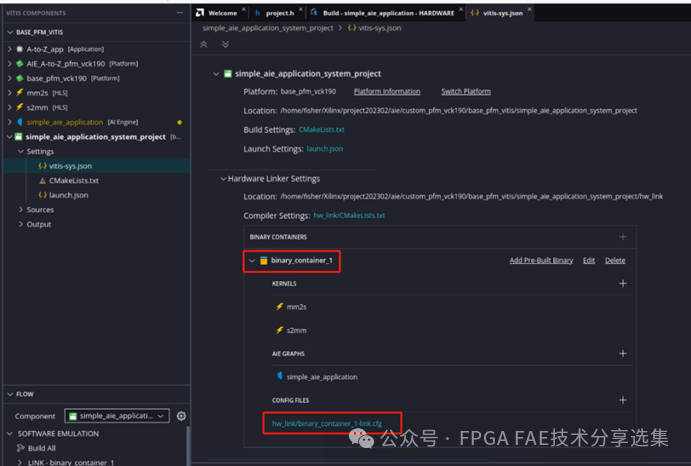

5)打开simple_aie_application_system_project-> Settings

下名为vitis-sys.json 的设置文件,然后单击文件底部Components部分中的add Existing Component,单击HLS并选择mm2s和s2mm组件;

6)再次单击文件底部Components部分中的add Existing Component,单击AIEngine并选择simple_aie_application组件;

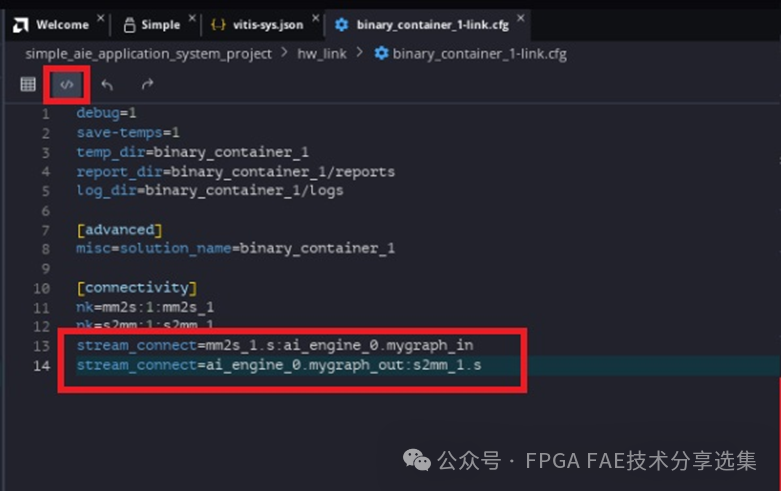

7)现在需要告诉 Vitis 编译器系统的连接情况,此步骤是使用配置文件完成的。仍在设置文件vitis-sys.json中,在Hardware LinkSettings下单击binary_container_1展开,然后单击hw_link/binary_container_1-link.cfg;

将binary_container_1-link.cfg显示更改为Source Editor,并在[connectivity]下添加以下行;

以上计算单元的命名规则参照Vitis Unified Software Platform Documentation: ApplicationAcceleration Development (UG1393);

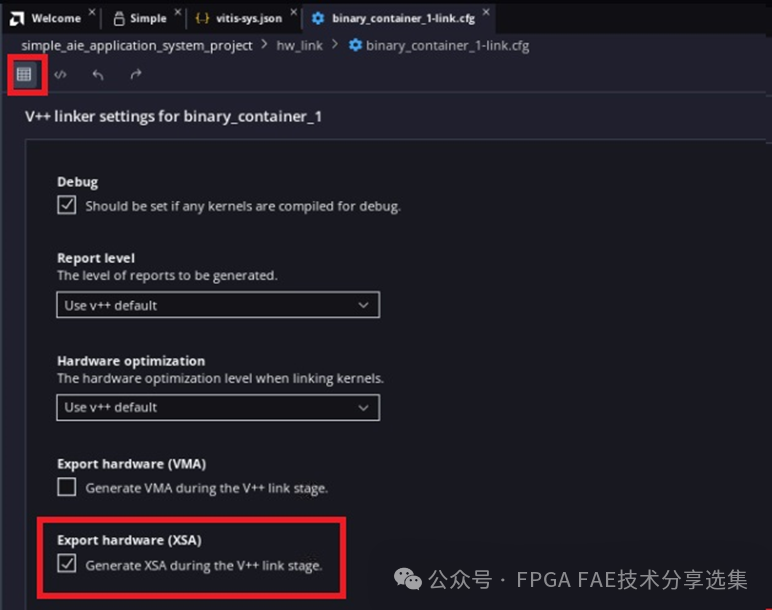

8)在binary_container_1-link.cfg页面中,将显示更改回Settings Form并启用Exporthardware (XSA)。

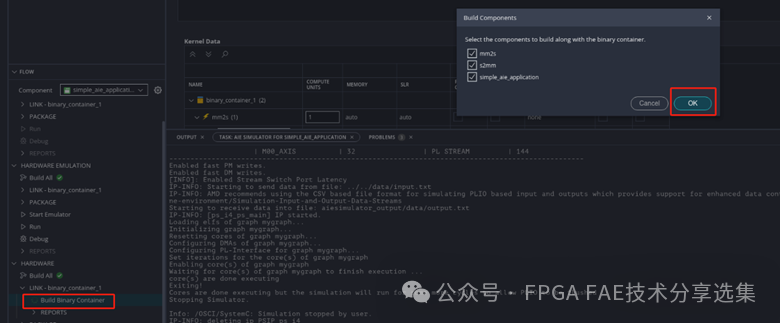

4.构建系统

1)在Vitis Unified IDE的流程导航器中,确保选择了simple_aie_application_system_project并单击HARDWARE -> LINK - binary_container_1下的Build Binary Container,当弹出页面要求构建组件(simple_aie_application、mm2s 和 s2mm)时,全选上后单击OK开始编译,编译过程需要一些时间才能完成,依次编译AI Engine应用工程、HLS硬件内核工程、硬件链接工程,过一段时间后系统可以成功构建并没有错误;

2)可以打开生成的Vivado工程

在下一步骤中,将创建一个处理系统 (PS) 裸机应用程序,并用它来运行该系统。

步骤四:PS 应用程序的创建和运行

在这一步骤中,将学习如何使用上面步骤中生成的XSA构建PS裸机应用程序,然后编译并运行整个系统。

1.在裸机Domain中创建一个新平台

1)在 Vitis Unified IDE 中,工作区目录与上面步骤中相同,单击File -> New Component-> Platform;

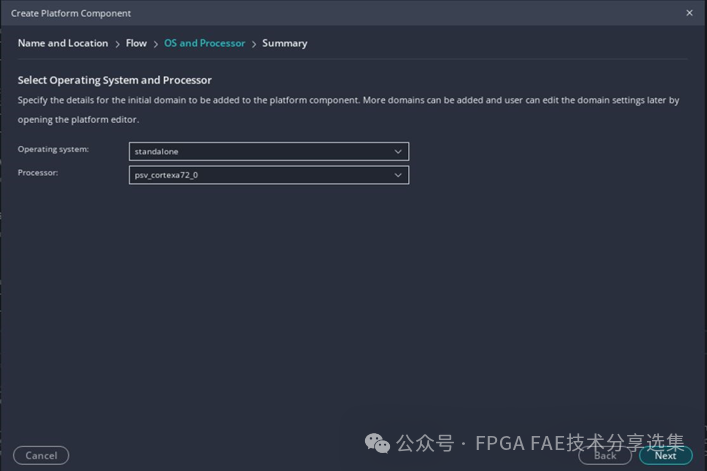

2)将平台项目名称设置为AIE_A-to-Z_pfm_vck190,然后单击Next;

3)使用上面步骤中生成的XSA,可以在以下位置找到该XSA:

4)将Operating system设置为standalone,将Processor设置为psv_cortexa72_0,单击Next,然后下一页面中单击Finish;

5)编译平台。

2.创建裸机的AI引擎控制应用程序

1)在 Vitis Unified IDE 中单击File -> New Component -> Application创建一个新应用程序;

2)将应用程序的名称设置为A-to-Z_app并单击Next;

3)选择刚刚创建的AIE_A-to-Z_pfm_vck190作为平台,然后单击Next;

4)选择 A72_0 domain(standalone_psv_cortexa72_0),单击Next,然后在下一页面中单击Finish;

5)右键单击A-to-Z_app工程下的src文件夹,然后单击Import -> Files;

6)将aie_control.cpp从simple_aie_application project工程中( simple_application/build/hw/Work/ps/c_rts/aie_control.cpp)导入到src文件夹中;

7)从文章末下载链接下载main.cpp导入到文件夹src中,浏览main.cpp文件的内容,可以看到代码正在初始化输入数据和输出数据的内存空间,需要注意的是这里使用.init()和.run()APIs 来控制AI引擎:

printf("Starting AIE Graph ");

printf("GraphInitialization ");

mygraph.init();

printf("Done ");

printf("- ");

printf("Running Graph for 4iterations ");

mygraph.run(4);

从系统中启用AI引擎graph有两种方式:

A. 在 PDI 中启用graph,这表示该graph将在BOOT 期间启动并永远运行;

B.使用

APIs从PS程序中启动AI引擎graph,本例中就是使用的该启动方式。

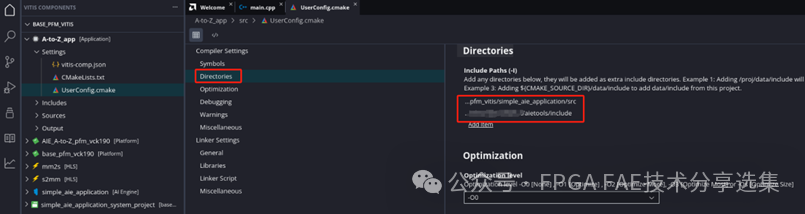

8)在A-to-Z_app 组件下,打开Settings下的UserConfig.cmake,在Directories中的Include Paths (-I)里添加以下目录:

A.

B.$ENV{XILINX_VITIS}/aietools/include。

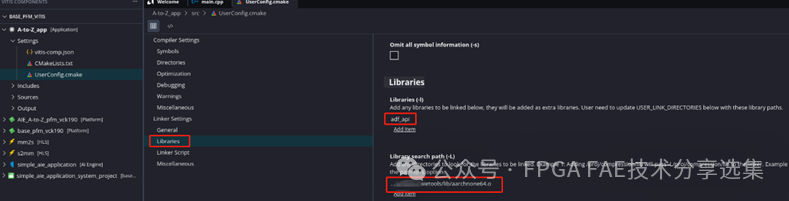

9)仍在UserConfig.cmake文件中的Libraries部分中添加以下:

A.在Libraries (-l)里添加adf_api;

B.在Librarysearch path (-L)里添加$ENV{XILINX_VITIS}/aietools/lib/aarchnone64.o。

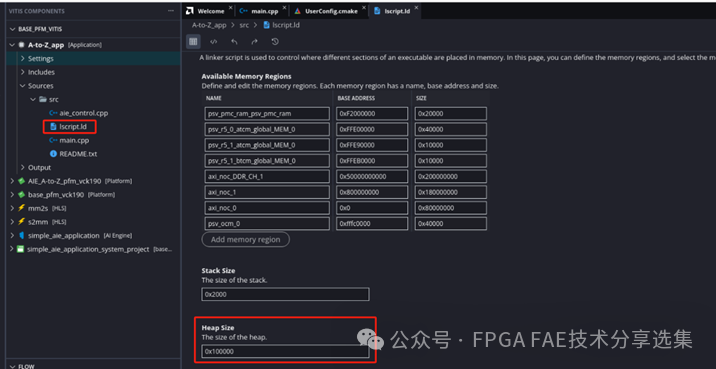

10)修改Linker Script以增加 AIE 库的heap;

A.展开A-to-z_app组件;

B.在src目录中,单击lscript.ld打开该项目Linker Script;

C.在Linker Script中将heap大小修改为0x100000(1MB)。

11)构建组件A-to-Z_app。

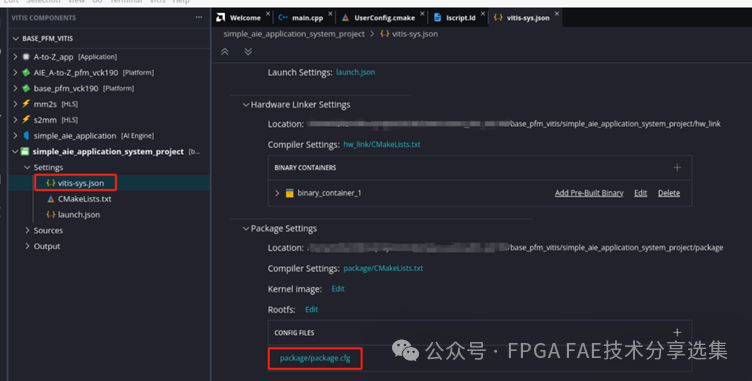

3.打包整个系统

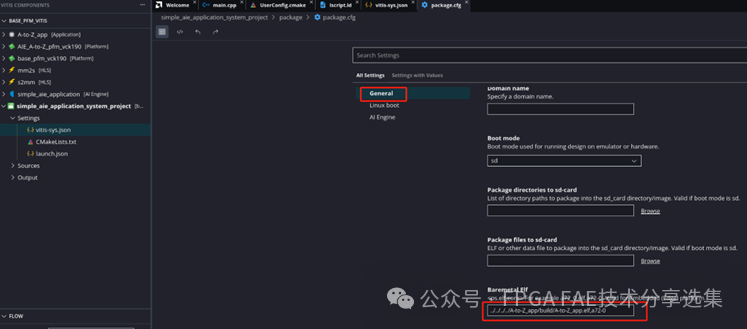

1) 展开simple_aie_application_system_project,在Settings目录中,单击打开vitis-sys.json,然后单击Package Settings下的package.cfg配置文件;

2)在package.cfg的General部分的 Baremetal Elf 设置中添加以下内容,告诉打包程序添加应用程序可执行文件,并在A72处理器上运行它;

../../../../A-to-Z_app/build/A-to-Z_app.elf,a72-0

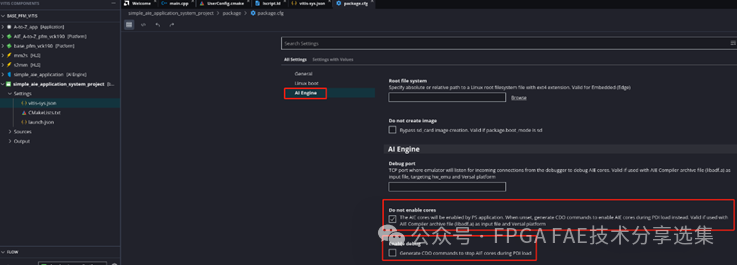

3)在AI Engine部分中,选择Do not enable cores选项,取消选择Enabledebug选项;

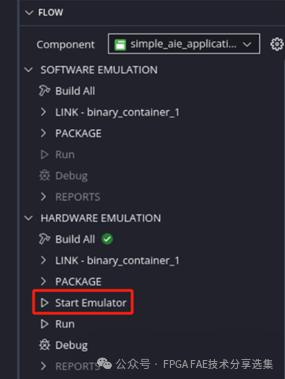

4)编译用于硬件仿真的simple_aie_application_system_project项目(单击Flow 导航器中HARDWARE EMULATION下的Build All )。

4.在Hardware Emulation中运行系统

现在整个系统已经构建完成,可以在 hardware emulation中对其进行测试;

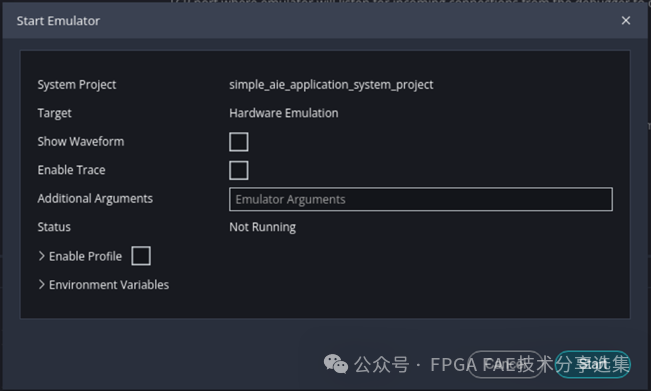

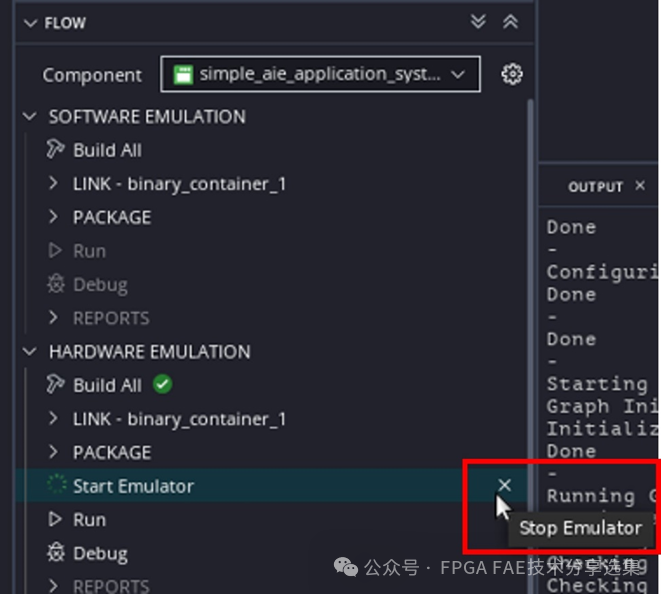

1)选中simple_aie_application_system_project,在流程导航器中,单击HARDWARE EMULATION下的StartEmulator;

2)在Start Emulator弹出窗口中,保留默认设置并单击Start;

注意:可以使能Show Waveform选项打开Vivado Simulator,并观察 PL 信号的波形,如果使能了此选项,请确保在Vivado Simulator中运行simulation,因为 QEMU将等待它。

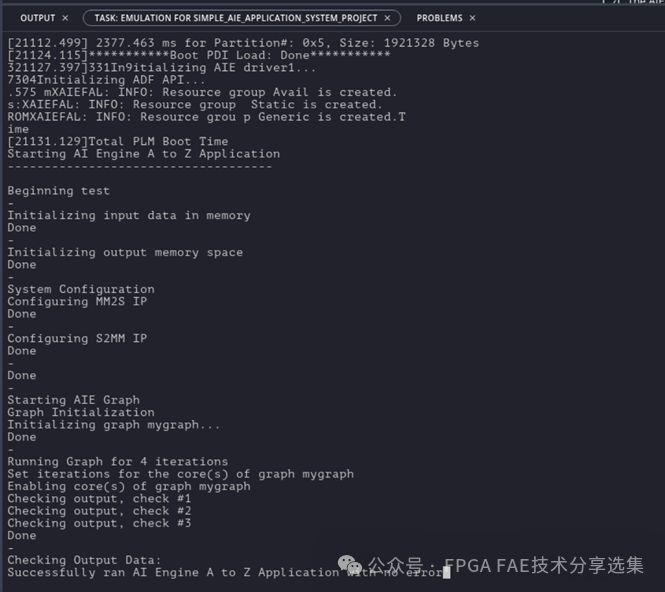

3)可以在Vitis控制台中看到应用程序成功运行且没有错误;

4)要停止Emulator,单击流程导航器中Start Emulator上的ⅹ。

5.针对硬件构建系统

在硬件中运行系统之前,需要重建系统以针对硬件;为硬件编译构建simple_aie_application_system_project项目(单击Flow 导航器中HARDWARE下的Build All )。

6.在硬件中运行系统

使用 SD 卡运行应用程序:

1)正确连接好开发板的电源线、JTAG USB 线、UART USB 线,并将启动模式设置为 SD 启动;

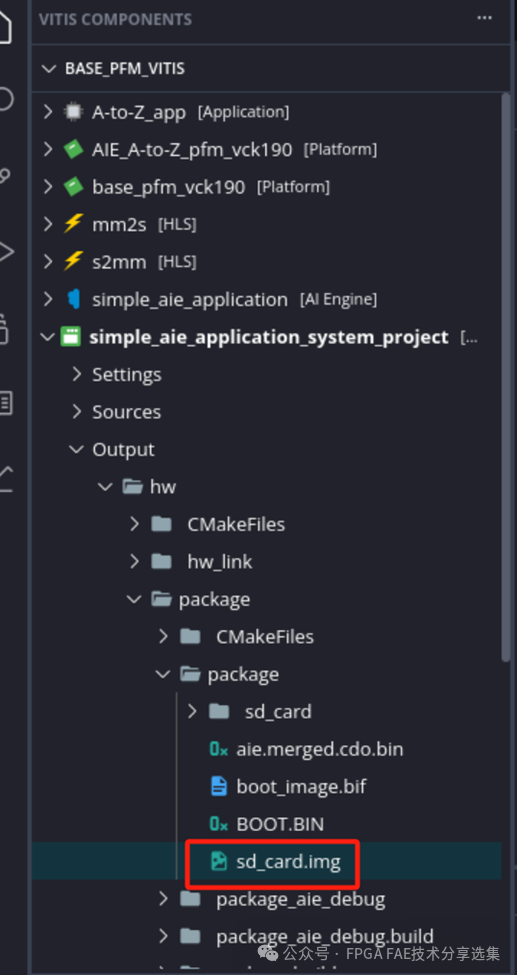

2)展开simple_aie_application_system_project组件下的Output -> hw -> package,在该package目录中,有一个sd_card.img文件;

3)使用balenaEtcher工具将sd_card.img烧录到SD卡中;

4)启动连接到VCK190 COM端口的UART终端;

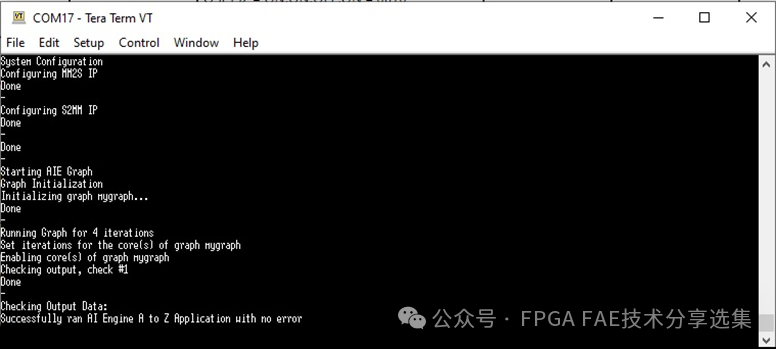

5)将 SD 卡插入开发板,然后打开开发板电源,可以看到应用程序成功运行,没有错误。

三总结

在本文中,基于 VCK190评估板,在Vivado中创建了一个通用的硬件平台并导出,在Vitis Unified中将 AI Engine 内核和 PL 内核添加到系统中,并构建了 PS 裸机应用程序来控制系统,并在HARDWARE EMULATION和硬件中运行成功。通过以上步骤可以知道怎么把Versal的AIE用起来,希望能够帮助大家尽快能将AMD Versal中这一全新的创新处理技术AI引擎运用到项目或者产品中。

下一篇文章会基于这篇文章介绍创建一个运行Linux操作系统的Vitis平台,并在该平台上运行AI引擎工程。

审核编辑:刘清

-

Linux系统

+关注

关注

4文章

609浏览量

29629 -

机器学习

+关注

关注

66文章

8541浏览量

136214 -

数据交互

+关注

关注

0文章

30浏览量

10691 -

中断控制器

+关注

关注

0文章

62浏览量

9773 -

Vivado

+关注

关注

19文章

846浏览量

70454

原文标题:Versal裸机使用AI Engine的完整流程

文章出处:【微信号:Comtech FPGA,微信公众号:Comtech FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

Vitis里如何创建嵌入式软件工程

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

StrongARM及其嵌入式应用平台

WP369可扩展式处理平台-各种嵌入式系统的理想解决方案

AMD推出第二代Versal器件,为AI驱动型嵌入式系统提供端到端加速

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

基于AMD、ARM、Intel和NVIDIA技术构建的嵌入式工控机

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程

评论