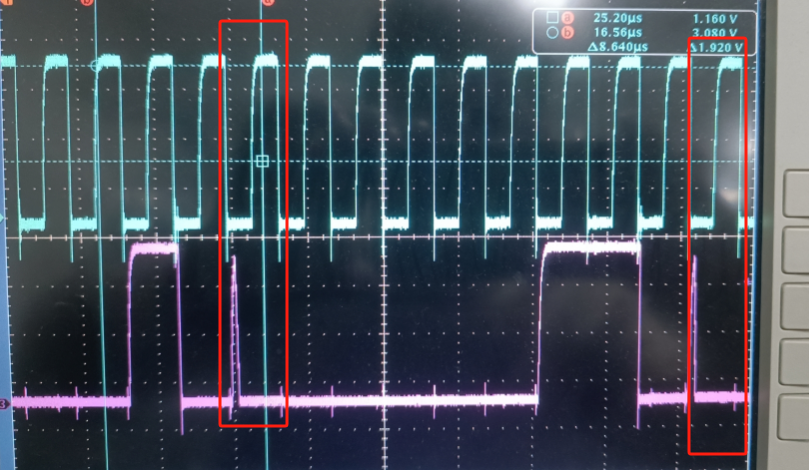

在I2C的波形中,经常会发现有这样的脉冲毛刺,会被认为是干扰或者器件不正常。

看到这个波形时,可以先数一下出现在第几个clock的位置,如果出现在第9个clock的低电平期间,就不是干扰或者器件异常导致。

在I2C的协议中,不管是地址匹配阶段还是数据读写阶段,第9个clock都是ACK和NACK位;

其中NACK为第9个SCL上升沿时SDA高电平:

ACK为第9个SCL上升沿时SDA低电平:

在地址匹配阶段由从机来回复ACK,在数据收发阶段由接受方来回复ACK。

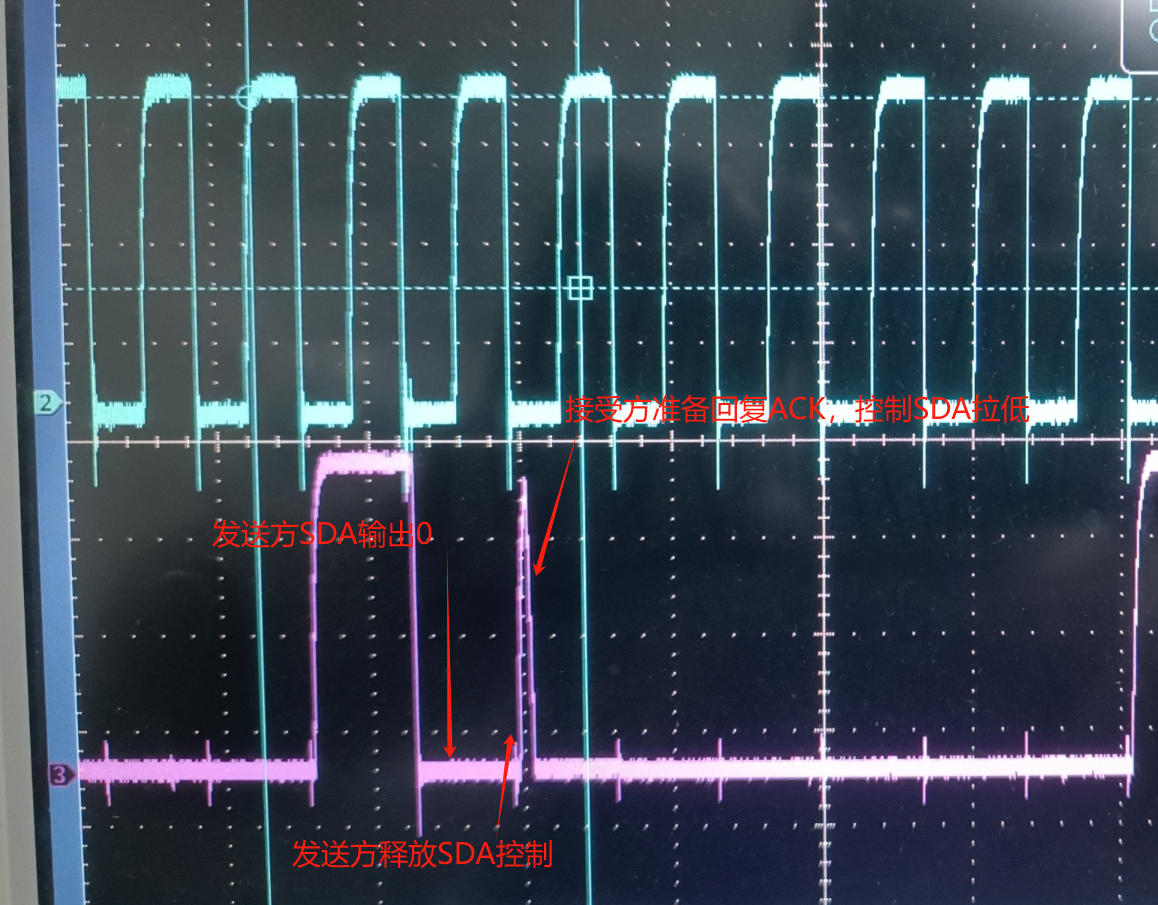

那么I2C是双向半双工通信,SDA引脚通过主机和从机共同控制,ACK回复过程意味着发送方会在通过SDA发送了8个bit的数据后释放SDA控制权给接受方,此时如果最后一个波形数据BIT0是0,那SDA会在SCL下降沿后从拉低状态被释放,由于上拉电阻的作用SDA就会恢复到高电平,但紧接着接受方开始数据建立开启对SDA的控制权,拉低SDA引脚准备回复ACK,于是SDA信号被再次拉低。

由于整个过程是连续的,且都会在SCL第9个Clock的低电平期间完成,产生的波形就会像一个毛刺被误认为干扰。实际上这个波形的出现不用在意,可以不采取任何措施。

-

单片机

+关注

关注

6074文章

45340浏览量

663623 -

mcu

+关注

关注

147文章

18613浏览量

387194 -

嵌入式

+关注

关注

5186文章

20151浏览量

328896 -

I2C

+关注

关注

28文章

1547浏览量

130497 -

GD32

+关注

关注

7文章

429浏览量

26943

发布评论请先 登录

为什么当微控制器 (MCU) 用作 I2C 从机时,I2C_SCL在接收连续数据时会出现时钟拉伸?

为什么当微控制器(MCU)用作I2C从机时,I2C_SCL连续接收数据时会出现时钟拉伸?

MCU实现I2C通信

I2C接口配置ES7243录音芯片,MCU(STM32)收不到I2C ACK的问题

硬件I2C与模拟I2C

I2C通信没反应怎么办?

如何提高I2C调试效率?

为什么MCU I2C波形中会出现的脉冲毛刺?

为什么MCU I2C波形中会出现的脉冲毛刺?

评论