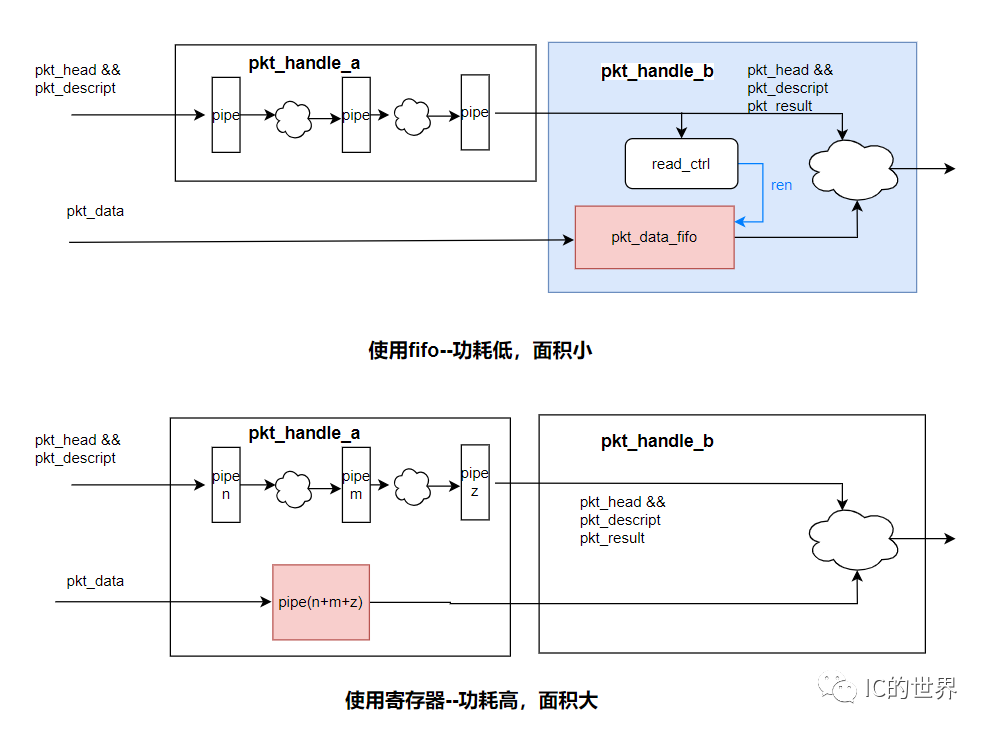

本案例中,我们讲解一种使用fifo节约资源,降低功耗的设计。如图所示,pkt_handle_a模块是对数据包进行处理的模块,但是不需要包数据(pkt_data),而仅仅需要根据包头(pkt_header)和包描述符(pkt_descript)。

这时候该怎么设计呢?

可以采用如下方式:在pkt_handle_b模块使用一个fifo用于存储包数据(pkt_data),pkt_handle_a模块的输入仅仅只有包头和包描述符,pkt_handle_a模块完成包处理后新增处包处理结果(pkt_result),送到pkt_handle_b模块,pkt_handle_b模块在需要读出包数据(pkt_data)的时候才将fifo内的数据读出。

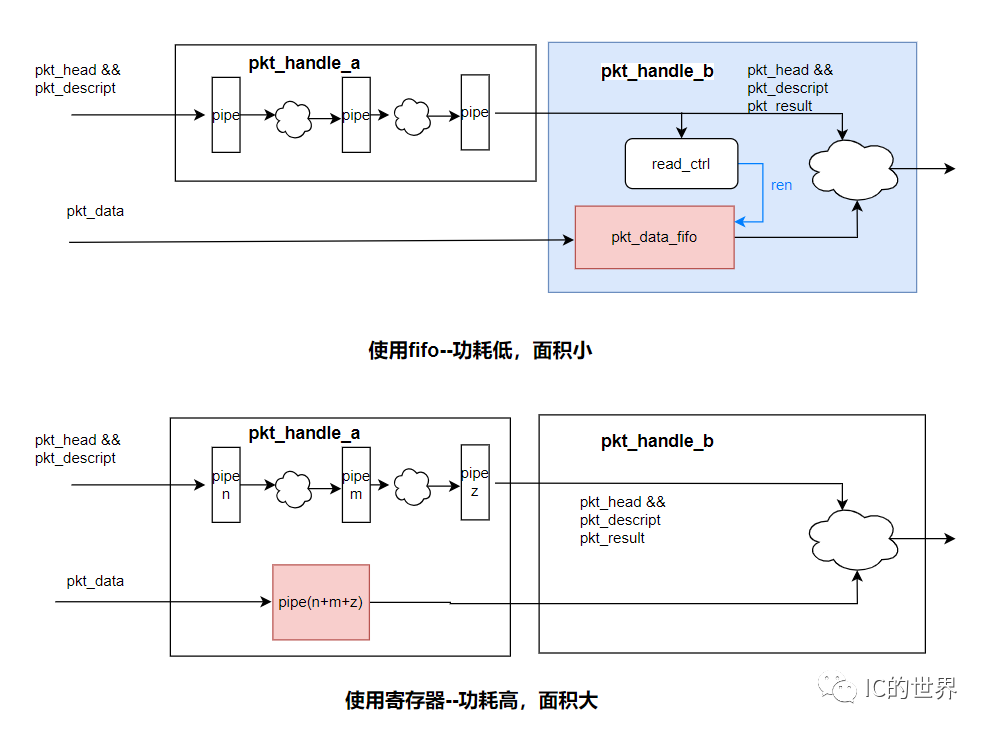

在包数据位宽较大,pkt_handle_a流水拍数较大时,相对于使用寄存器对包数据(pkt_data)进行打拍,使用fifo存储包数据(pkt_data)的实现方式更有优势,功耗低,面积小。

虽然从存储bit位角度计算两种设计需要的bit位几乎相同,但是相对于寄存器,底层用ram实现的fifo面积更小,功耗更低。

pkt_handle_a和pkt_handle_b之间可能存在更多的模块,数据流水可能长达几十到上百个周期,因此流水拍数越大,节约面积,降低功耗的效果越明显。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:IC设计:ram的应用-一种降功耗的设计方法

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

相关推荐

概念: Power/Ground Gating是集成电路中通过关掉那些不使用的模块的电源或者地来降低电路漏电功耗的低功耗设计方法。该方法能

![的头像]() 发表于

发表于 09-16 16:04

•1.1w次阅读

就显得尤为重要。如果OEM选择一种低功耗芯片用于其中一种应用,电池能用九个月,但另外一种芯片能使电池运行一年,那我们当然会选择后者。峰值电流

发表于 03-29 09:36

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一

发表于 02-09 14:58

MCU中的ADC14(集成14位模数转换器)作为示例。低功耗应用,以及减少高占空比应用中的启动时间都是ADC14设计过程中的考量要素。然而,各个应用都有独特的特点,因此,为最大限度地降低功耗,必须谨慎

发表于 11-18 10:14

考虑。工程师在解决功耗问题的时候,可以把下面这些准则作为任何一种设计方法学的有机组成部分加以应用。 IC芯片设计过程中的一个重要参数,在做设计决策和权衡时把

发表于 06-29 16:46

随着车载电子设备越来越多,功耗问题变得日趋严重。例如,如果音频功率放大器的静态电流达到200ma,则采用12v电源时静态功耗就高达2.4w。有没有一种方法能开机但不需要扬声器发出声音的时候,关闭放大器来

发表于 08-06 08:23

引言针对中心机房功耗越来越大的问题,某些电信运营商制定了采购设备功耗每年降低20%的目标。半导体是功耗问题的关键所在,其解决方法是重新设计芯

发表于 07-31 07:13

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一

发表于 08-15 08:28

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一

发表于 11-05 07:54

ZED 和ZC,在组网正常的情况下,ZED可以进入低功耗模式,电流在uA级别。CC2530芯片当关闭ZC后,ZED会持续的进行网络发现,无法进入低功耗模式。电流达28mA;求教TI工程师,如何降低ZC发现网络的频次以

发表于 08-07 07:03

降低功耗不光能够大大的节约电能还能简化电源部分的设计,甚至可以用于手持设备上面使用,这些都已经越来越成为未来产品的设计方向。

发表于 02-26 07:27

本文以嵌入式实时操作系统μC/OS-II在飞思卡尔8位单片机HCS08GT60上的移植为例,详细讨论如何利用μC/OS-II给出的内核扩展接口,实现一个低功耗的嵌入式实时系统;进一步分析如何选择

发表于 04-27 06:26

分享一种具有低功耗意识的FPGA设计方法

发表于 04-29 06:15

随着车载电子设备越来越多,功耗问题变得日趋严重。例如,如果音频功率放大器的静态电流达到200ma,则采用12v电源时静态功耗就高达2.4w。有没有一种方法能开机但不需要扬声器发出声音的时候,关闭放大器来

发表于 11-29 08:14

如何降低设备功耗,降低采集设备功耗的几种方法 工程监测传感器 以下是降低数采设备

![的头像]() 发表于

发表于 10-11 09:29

•609次阅读

一种使用fifo节约资源降低功耗的设计方法

一种使用fifo节约资源降低功耗的设计方法

评论