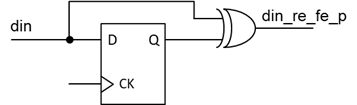

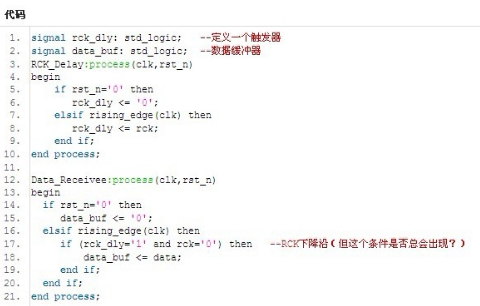

如何知道一个信号上升沿或下降沿是否到来?下面是一个简单的边沿检测电路。

这个电路的原理很简单。当din上升沿或下降沿到来时,din_re_fe_p产生一个脉冲。后续电路看到这个脉冲,就知道din上升沿或下降沿发生了。

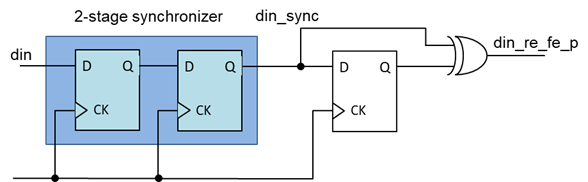

如果din是异步输入,前面要加一个两级同步器(其实就是两级DFF)。

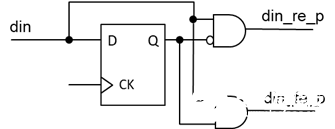

边沿检测可以演化出只检测上升沿,只检测下降沿。

边沿检测电路非常有用。

例1:作为跨时钟域同步握手信号

有一组信号data_bus,需要从clk_a同步到clk_b。如果每一个信号都经过两级同步器,那就太浪费资源了。而且有时一组信号要保证所有位传到clk_b时同时更新,就更不能用两级同步器了。两级同步器的latency在1到3个周期之间,有随机性,无法保证两个信号各自通过同步器后同时更新。

这个场景可以加一个简单的握手信号data_toggle。当clk_a这边信号变化时,data_toggle也改变状态(0->1或1->0)。data_toggle送到clk_b,经过两级同步+边沿检测产生data_toggle_re_fe_p,clk_b这边的逻辑看到data_toggle_re_fe_p脉冲后,就可以放心大胆地锁存data_bus。

喜欢low power的朋友可以把data_toggle_re_fe_p作为ICG的EN信号。RTL写得干净,工具也能自动infer ICG。

边沿检测输出作为ICG EN其实是非常有用的low power技巧之一。

当然,这个例子是很简单地握手方式。复杂一些的可以用request,acknowledge之类的双向握手。

clk_a送一个req=1到clk_b,告诉clk_b数据ready。

clk_b同步req并做上升沿检测。检测到req上升沿后锁存数据。

clk_b发一个ack=1给clk_a,告诉clk_a数据已经锁存。

clk_a同步ack并做上升沿检测。检测到ack上升沿后清除req=0,准备下一次传数据。

clk_b这边检测到req下降沿,清除ack=0,准备接受下一次数据。

审核编辑:黄飞

-

电路图

+关注

关注

10459文章

10749浏览量

551783 -

检测电路

+关注

关注

13文章

314浏览量

59462 -

同步器

+关注

关注

1文章

117浏览量

15528

发布评论请先 登录

数字前端电路:简单的边沿检测电路分析

数字前端电路:简单的边沿检测电路分析

评论